## Massachusetts Institute of Technology Department of Electrical Engineering and Computer Science

6.002 – Electronic Circuits Spring 2002

Homework #4

Issued 2/27/02 – Due 3/6/02

**Exercise 4.1:** Consider the logic circuit that implements  $OUT = IN1 + (IN2 \cdot \overline{IN3})$ . Express OUT as a function of IN1, IN2 and IN3 in the form of a truth table. Also, implement this logic circuit using logic symbols, and using a small number of n-channel MOSFETs and pull-up resistors.

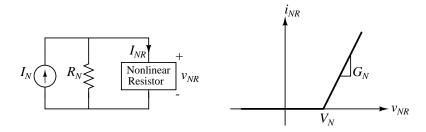

**Exercise 4.2:** A Norton equivalent network is used to excite a nonlinear resistor as shown below. The graphical i-v characteristic that defines the nonlinear resistor is also shown below. Determine the terminal current  $i_{NR}$  and the terminal voltage  $v_{NR}$  of the nonlinear resistor for all values of  $I_N$ . Hint: consider using load-line analysis to gain insight.

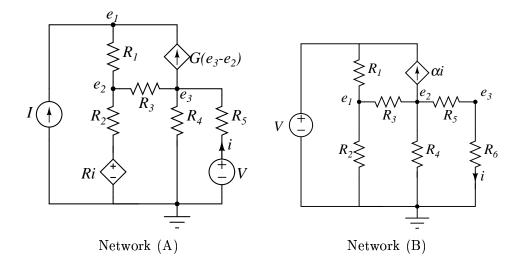

**Problem 4.1:** Following the node method, develop a set of simultaneous equations for the networks shown below that can be solved to determine the unknown node voltages. Express the set of equations in the form

$$G \left[ \begin{array}{c} e_1 \\ e_2 \\ e_3 \end{array} \right] = S$$

where G is a  $3 \times 3$  array of conductance terms and S is a  $3 \times 1$  vector of terms involving the *independent* sources. You need not solve the set of equations for the node voltages.

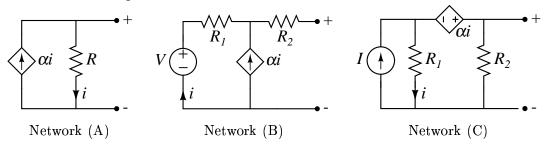

**Problem 4.2:** Determine the Thevenin equivalent of each network shown below. Note that these networks contain dependent sources.

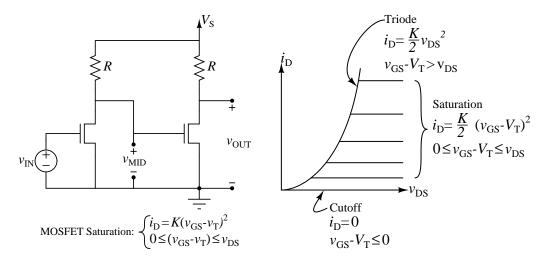

**Problem 4.3:** This problem studies the two-stage n-channel MOSFET amplifier shown below. The two stages are built with identical MOSFETs and pull-up resistors. A simplified model for the MOSFET is also given below. The simplification is that the triode region of operation is compressed onto the curve  $i_{\rm D} = K v_{\rm DS}^2/2$ , which becomes a common curve of operation for  $v_{\rm GS} - V_{\rm T} > v_{\rm DS}$ . Hint a load-line analysis may help solve this problem.

- (A) Determine the range of  $v_{\text{IN}}$  over which MOSFET M1 operates in cutoff. Also, determine  $v_{\text{MID}}$  for this operating range.

- (B) Assuming that MOSFET M1 operates in its saturation region, determine  $v_{\rm MID}$  as a function of  $v_{\rm IN}$ . Also, determine the range of  $v_{\rm MID}$  and the range of  $v_{\rm IN}$  that correspond to the saturated operation of MOSFET M1.

- (C) For values of  $v_{\text{IN}}$  that are above the range found in Part (B), MOSFET M1 operates in its triode region, which in the model below is compressed onto the curve  $i_{\text{D}} = K v_{\text{DS}}^2/2$ . Determine  $v_{\text{MID}}$  for  $v_{\text{IN}}$  in this range of operation.

- (D) Using the results of Parts (A), (B) and (C), determine  $v_{\text{OUT}}$  as a function of  $v_{\text{MID}}$  for the cutoff, saturation and triode regions of operation of MOSFET M2. For each region, state the corresponding operating range of  $v_{\text{MID}}$  and  $v_{\text{OUT}}$ .

- (E) Assuming that both MOSFETs operate in their saturation regions, determine  $v_{\text{OUT}}$  as a function of  $v_{\text{IN}}$ . Also, determine the range of  $v_{\text{MID}}$  and then the corresponding range of  $v_{\text{IN}}$  over

which both MOSFETs operate in their saturation regions.

- (F) Determine the small-signal gain of the amplifier as a function of the operating-point input  $V_{\rm IN}$  assuming that this operating point falls within the range found in Part (E). That is, determine  $dv_{\rm OUT}/dv_{\rm IN}$  evaluated at  $V_{\rm IN}$ .

- (G) Let K=0.02 A/V<sup>2</sup>,  $R_{\rm D}=1$  k $\Omega$ ,  $V_{\rm S}=10$ V and  $V_{\rm T}=1$  V. Plot  $v_{\rm MID}$  as a function of  $v_{\rm IN}$  for  $0 \le v_{\rm IN} \le 3$  V. On the same graph, plot  $v_{\rm OUT}$  as a function of  $v_{\rm IN}$  over the same range of  $v_{\rm IN}$ . Hint: this is particularly simple if you are familiar with MatLab on Athena. Observe the differences of the two plots.

Save a copy of your solutions to help with Homework #5.

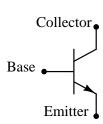

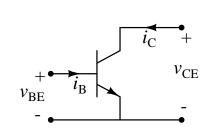

**Problem 4.4:** An NPN bipolar junction transistor (NPN BJT) is a three-terminal device. Its terminals are referred to as the base, the collector and the emitter. The symbol for the NPN BJT is shown below, along with the voltage and current definitions for this BJT when it is viewed as a two-port device. Here, the Base-Emitter port acts as a control port and the Collector-Emitter port acts as a power port, much like the Gate-Source and Drain-Source ports of an n-channel MOSFET, respectively.

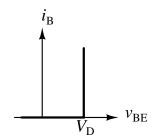

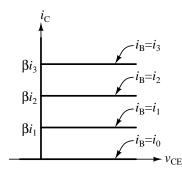

Figures 1 and 2 below describe the *greatly* idealized behavior of an NPN BJT in terms of its port variables. Figure 1 describes the behavior of the control port, and shows how  $i_{\rm B}$  is related to  $v_{\rm BE}$ . Figure 2 describes the behavior of the power port, and shows how  $i_{\rm C}$  is related to  $v_{\rm CE}$  for various values of  $i_{\rm B}$ . In general, for  $i_{\rm B} > 0$  and  $v_{\rm CE} > 0$ ,  $i_{\rm C} = \beta i_{\rm B}$  where  $\beta$  is a gain constant.

This problem investigates the use of the NPN BJT described by Figures 1 and 2 to construct an amplifier. The amplifier is shown in Figure 3. Assume that  $V_S > V_D$ .

- (A) Determine  $i_{\rm B}$  as a function of  $v_{\rm IN}$ . Sketch and clearly label the result. Hint: a load-line analysis might provide useful insight given the nonlinear behavior shown in Figure 1.

- (B) Determine  $v_{\text{OUT}}$  as a function of  $i_{\text{B}}$ ; note that  $v_{\text{OUT}} = v_{\text{CE}}$  for the amplifier shown in Figure 3. Sketch and clearly label the result. Hint: a load-line analysis might provide useful insight given the nonlinear behavior shown in Figure 2.

- (C) Combine the results of Parts (A) and (B) to determine  $v_{\text{OUT}}$  as a function of  $v_{\text{IN}}$ . Sketch and

clearly label the result.

## Symbol

## **Two-Port Definitions**

Figure 1

Figure 2

Figure 3