# Lecture 6

- Design methodology for sequential logic

- -- identify distinct states

- -- create state transition diagram

- -- choose state encoding

- -- write combinational Verilog for next-state logic

- -- write combinational Verilog for output signals

- Lots of examples

9/26/2018 6.111 Fall 2018

6.111 Fall 2018

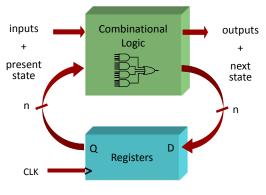

#### Finite State Machines

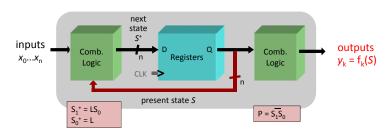

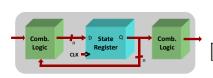

- Finite State Machines (FSMs) are a useful abstraction for sequential circuits with centralized "states" of operation

- At each clock edge, combinational logic computes *outputs* and *next state* as a function of *inputs* and *present state*

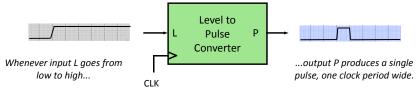

#### Design Example: Level-to-Pulse

- A level-to-pulse converter produces a singlecycle pulse each time its input goes high.

- It's a synchronous rising-edge detector.

- Sample uses:

- Buttons and switches pressed by humans for arbitrary periods of time

- Single-cycle enable signals for counters

9/26/2018 6.111 Fall 2018

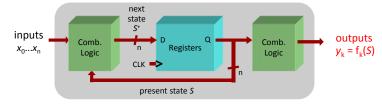

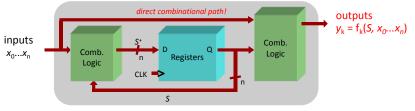

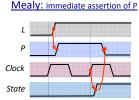

# Two Types of FSMs

Moore and Mealy FSMs: different output generation

#### •Moore FSM:

#### •Mealy FSM:

9/26/2018 6.111 Fall 2018

9/26/2018

6.111 Fall 2018

#### Design Example: Level-to-Pulse

- A level-to-pulse converter produces a singlecycle pulse each time its input goes high.

- It's a synchronous rising-edge detector.

- Sample uses:

- Buttons and switches pressed by humans for arbitrary periods of time

- Single-cycle enable signals for counters

9/26/2018 6.111 Fall 2018

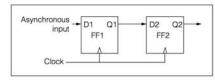

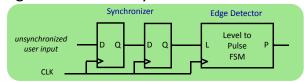

# Reminder on the Synchronizer

Stringing several (often two or three is sufficient) registers in series is enough to isolate an asynchronous input from sensitive downstream logic and registers

9/26/2018 6.111 Fall 2018 6

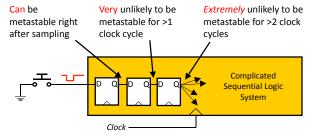

# Handling Metastability

- Preventing metastability turns out to be an impossible problem

- High gain of digital devices makes it likely that metastable conditions will resolve themselves quickly

- Solution to metastability: allow time for signals to stabilize

How many registers are necessary?

- Depends on many design parameters (clock speed, device speeds, ...)

- In 6.111, a pair of synchronization registers is sufficient

# Handling Metastability

Figure 8. Two-flip-flop synchronization circuit.

FF2 (D-reg2) might go a clock cycle late, but it will almost never\* go metastable

\*almost never generally means actually almost never (once in ten years or something)

9/26/2018

"Metastability and Synchronizers: A Tutorial" Ran Ginosar, Technion Israel Institute of Technology

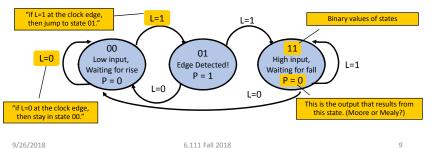

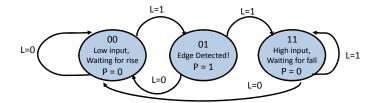

#### Step 1: State Transition Diagram

• Block diagram of desired system:

State transition diagram is a useful FSM representation and design aid:

#### Valid State Transition Diagrams

- Arcs leaving a state are mutually exclusive, i.e., for any combination input values there's at most one applicable arc

- Arcs leaving a state are collectively exhaustive, i.e., for any combination of input values there's at least one applicable arc

- So for each state: for any combination of input values there's <u>exactly one</u> applicable arc

- Often a starting state is specified

- Each state specifies values for all outputs (Moore)

9/26/2018 6.111 Fall 2018 10

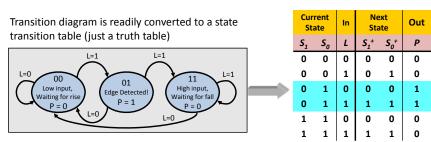

### **Choosing State Representation**

#### Choice #1: binary encoding

For N states, use  $\operatorname{ceil}(\log_2 N)$  bits to encode the state with each state represented by a unique combination of the bits. Tradeoffs: most efficient use of state registers, but requires more complicated combinational logic to detect when in a particular state.

#### Choice #2: "one-hot" encoding

For N states, use N bits to encode the state where the bit corresponding to the current state is 1, all the others 0. Tradeoffs: more state registers, but often much less combinational logic since state decoding is trivial.

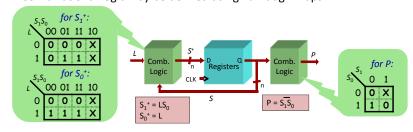

#### Step 2: Logic Derivation

• Combinational logic may be derived using Karnaugh maps

9/26/2018 6.111 Fall 2018 11 9/26/2018 6.111 Fall 2018 12

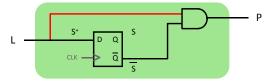

#### Moore Level-to-Pulse Converter

Moore FSM circuit implementation of level-to-pulse converter:

9/26/2018 6.111 Fall 2018

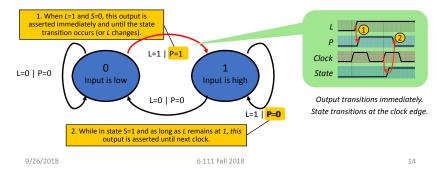

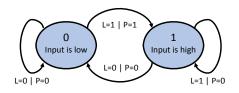

# Design of a Mealy Level-to-Pulse

• Since outputs are determined by state *and* inputs, Mealy FSMs may need fewer states than Moore FSM implementations

### Mealy Level-to-Pulse Converter

| Pres.<br>State | In | Next<br>State | Out |

|----------------|----|---------------|-----|

| S              | L  | S⁺            | P   |

| 0              | 0  | 0             | 0   |

| 0              | 1  | 1             | 1   |

| 1              | 1  | 1             | 0   |

| 1              | 0  | 0             | 0   |

13

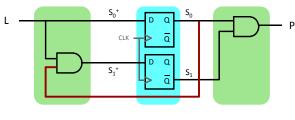

#### Mealy FSM circuit implementation of level-to-pulse converter:

• FSM's state simply remembers the previous value of L

9/26/2018

Circuit benefits from the Mealy FSM's implicit single-cycle assertion of outputs during state transitions

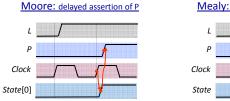

### Moore/Mealy Trade-Offs

- How are they different?

- Moore: outputs = f( state ) only

- Mealy outputs = f( state and input )

- Mealy outputs generally occur <u>one cycle earlier</u> than a Moore:

- Compared to a Moore FSM, a Mealy FSM might...

- Be more difficult to conceptualize and design

- Have fewer states

6.111 Fall 2018 15 9/26/2018 6.111 Fall 2018 16

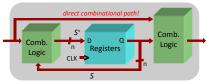

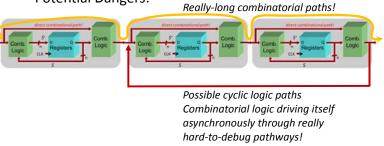

# Moore/Mealy Trade-Offs

- Moore:

- Usually more states

- Each state has a particular output

- Mealy:

- Fewer states, outputs are specified on edges of diagram

• Potential Dangers:

9/26/2018 6.111 Fall 2018 17

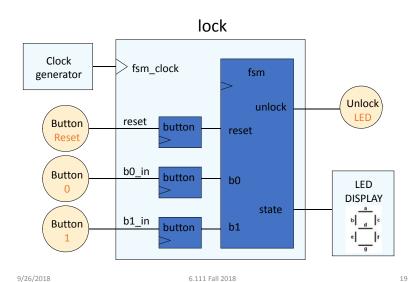

#### FSM Example

#### **GOAL**:

Build an electronic combination lock with a reset button, two number buttons (0 and 1), and an unlock output. The combination should be 01011.

#### STEPS:

- 1. Design lock FSM (block diagram, state transitions)

- 2. Write Verilog module(s) for FSM

9/26/2018 6.111 Fall 2018

# Step 1A: Block Diagram

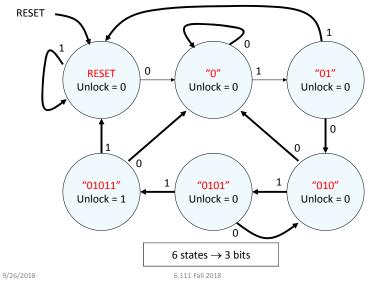

### Step 1B: State transition diagram

#### Step 2: Write Verilog

9/26/2018 6.111 Fall 2018

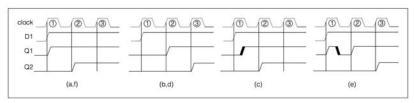

#### Step 2A: Synchronize buttons

```

// push button synchronizer and level-to-pulse converter

// OUT goes high for one cycle of CLK whenever IN makes a

// low-to-high transition.

module button(

input clk, in,

output out

reg r1, r2, r3;

always @(posedge clk)

synchronizer

state

begin

r1 <= in; // first reg in synchronizer

r2 <= r1; // second reg in synchronizer, output is in sync!

r3 <= r2; // remembers previous state of button

end

// rising edge = old value is 0, new value is 1

assign out = \simr3 & r2:

endmodule

9/26/2018

6.111 Fall 2018

```

### Step 2B: state transition diagram

```

parameter S_RESET = 0; // state assignments

parameter S_0 = 1;

parameter S_01 = 2;

parameter S_010 = 3;

parameter S_0101 = 4;

parameter S_01011 = 5;

reg [2:0] state, next_state;

always @(*) begin

// implement state transition diagram

if (reset) next_state = S_RESET;

else case (state)

S RESET: next state = b0 ? S 0 : b1 ? S RESET : state:

S_0:

next_state = b0 ? S_0 : b1 ? S_01

S 01:

next_state = b0 ? S_010 : b1 ? S_RESET : state;

S_010: next_state = b0 ? S_0 : b1 ? S_0101 : state;

S_0101: next_state = b0 ? S_010 : b1 ? S_01011 : state;

S_01011: next_state = b0 ? S_0 : b1 ? S_RESET : state;

default: next_state = S_RESET; // handle unused states

endcase

end

always @(posedge clk) state <= next_state;</pre>

6 111 Fall 2018

23

```

#### Step 2C: generate output

```

// it's a Moore machine! Output only depends on current state

assign out = (state == S_01011);

```

#### Inevitable Step 2D: debugging?

```

// hmmm. What would be useful to know? Current state?

// hex_display on labkit shows 16 four bit values

assign hex_display = {60'b0, 1'b0, state[2:0]};

```

9/26/2018 6.111 Fall 2018

# Real FSM Security System

9/26/2018 6.111 Fall 2018 25

# Step 2: final Verilog implementation

```

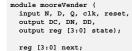

module lock(input clk,reset_in,b0_in,b1_in,

output out, output [3:0] hex_display);

wire reset, b0, b1; // synchronize push buttons, convert to pulses

button b_reset(clk,reset_in,reset);

button b_0(clk,b0_in,b0);

button b_1(clk,b1_in,b1);

parameter S_RESET = 0; parameter S_0 = 1; // state assignments

parameter S_01 = 2; parameter S_010 = 3;

parameter S_0101 = 4; parameter S_01011 = 5;

reg [2:0] state,next_state;

always @(*) begin

// implement state transition diagram

if (reset) next_state = S_RESET;

else case (state)

S_RESET: next_state = b0 ? S_0 : b1 ? S_RESET : state;

S_0: next_state = b0 ? S_0 : b1 ? S_01 : state;

S_01: next_state = b0 ? S_010: b1 ? S_RESET: state;

S_010: next_state = b0 ? S_0 : b1 ? S_0101 : state;

S_0101: next_state = b0 ? S_010 : b1 ? S_01011 : state;

S_01011: next_state = b0 ? S_0 : b1 ? S_RESET : state;

default: next_state = S_RESET;

// handle unused states

always @ (posedge clk) state <= next_state;

assign out = (state == S_01011);

// assign output: Moore machine

assign hex_display = {1'b0,state};

// debugging

endmodule

```

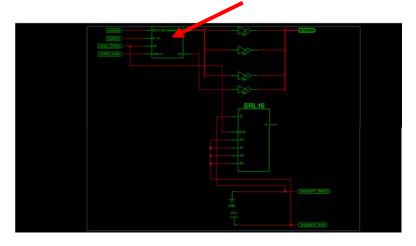

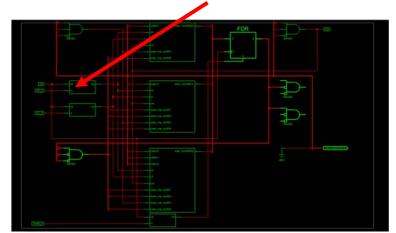

#### Does it Work?

Should have debounced inputs :/

#### Does it Work?

Double-click on Primary Module

Select

"View RTL Schematic"

9/26/2018 6.111 Fall 2018 27 9/26/2018 6.111 Fall 2018 28

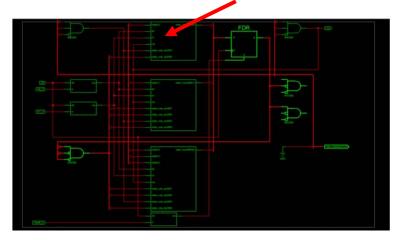

# Does it Work?

Double-click on Actual Stuff I wrote Module

9/26/2018 6.111 Fall 2018 2

Does it Work? Double-click on Actual Stuff I wrote Module

9/26/2018 6.111 Fall 2018 30

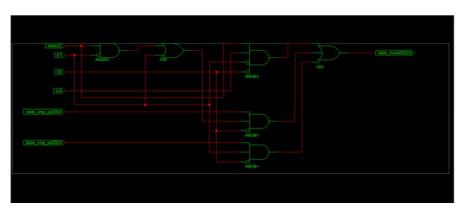

# Does it Work?

At the lowest level of my design

Does it Work? One of the button synchronizers

9/26/2018 6.111 Fall 2018 31 9/26/2018 6.111 Fall 2018 32

#### Does it Work?

```

// button

// push button synchronizer and level-to-pulse converter

// OUT goes high for one cycle of CLK whenever IN makes a

One of the button synchronizers!!!

// low-to-high transition.

module button(

input clk, in,

output out

reg r1, r2, r3;

always @(posedge clk)

begin

r1 <= in; // first reg in synchronizer

r2 <= r1; // second reg in synchronizer, output is in sync!

// remembers previous state of button

r3 <= r2:

end

// rising edge = old value is 0, new value is 1

assign out = \simr3 & r2:

endmodule

9/26/2018

6.111 Fall 2018

```

#### Example: Intersection Traffic Lights

- Design a controller for the traffic lights at the intersection of two streets – two sets of traffic lights, one for each of the streets.

- Step 1: Draw starting state transition diagram. Just handle the usual green-yellow-red cycle for both streets. How many states? Well, how many different combinations of the two sets of lights are needed?

- Step 2: add support for a walk button and walk lights to your state transition diagram.

- Step 3: add support for a traffic sensor for each of the streets – when the sensor detects traffic the green cycle for that street is extended.

Example to be worked collaboratively on the board...

**Encode all information in states!!!!!**

9/26/2018 6.111 Fall 2018

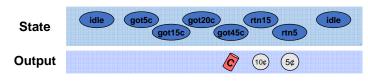

#### The 6.111 Vending Machine

- · Lab assistants demand a new soda machine for the 6.111 lab. You design the FSM controller.

- All selections are \$0.30.

- The machine makes change. (Dimes and nickels only.)

- Inputs: limit 1 per clock

- · Q quarter inserted

- . D dime inserted

- N nickel inserted

- Outputs: limit 1 per clock

- - DC dispense can

- DD dispense dime

- · DN dispense nickel

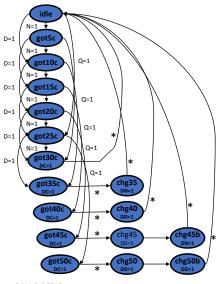

#### What States are in the System?

• A starting (idle) state:

• A state for each possible amount of money captured:

• What's the maximum amount of money captured before purchase? 25 cents (just shy of a purchase) + one quarter (largest coin)

• States to dispense change (one per coin dispensed):

9/26/2018 6.111 Fall 2018 9/26/2018 6.111 Fall 2018

#### A Moore Vender

Here's a first cut at the state transition diagram.

9/26/2018 6.111 Fall 2018

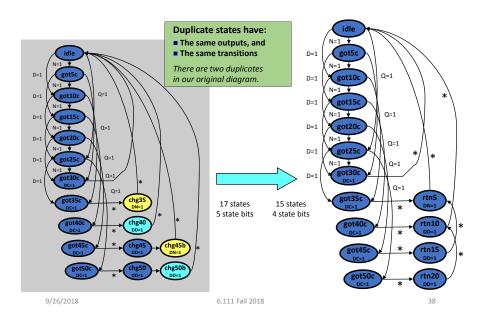

#### State Reduction

# Verilog for the Moore Vender

#### FSMs are easy in Verilog. Simply write one of each:

- State register So triggered on posedge clock

- Next-state combinational logic (comb. always block with case)

- Output combinational logic block (comb. always block or assign statements)

9/26/2018

#### States defined with parameter keyword

```

parameter IDLE = 0;

parameter GOT_5c = 1;

parameter GOT_10c = 2;

parameter GOT_15c = 3;

parameter GOT_25c = 4;

parameter GOT_25c = 5;

parameter GOT_35c = 6;

parameter GOT_35c = 7;

parameter GOT_40c = 8;

parameter GOT_50c = 10;

parameter GOT_5c = 10;

parameter GOT_5c = 11;

parameter RETURN_15c = 12;

parameter RETURN_15c = 12;

parameter RETURN_10c = 13;

parameter RETURN_5c = 14;

```

### State register defined with sequential always block

### Verilog for the Moore Vender

```

GOT_25c: if (Q) next = GOT_50c;

else if (D) next = GOT_35c;

else if (N) next = GOT_30c;

Next-state logic within a

combinational always block

else next = GOT 25c;

GOT_30c: next = IDLE;

always @ (state or N or D or Q) begin

GOT_35c: next = RETURN_5c;

GOT 40c: next = RETURN 10c;

case (state)

GOT 45c: next = RETURN 15c;

if (0) next = GOT 25c:

GOT_50c: next = RETURN_20c;

else if (D) next = GOT 10c:

else if (N) next = GOT 5c;

RETURN_20c: next = RETURN_10c;

else next = IDLE;

RETURN 15c: next = RETURN 5c;

RETURN 10c: next = IDLE;

GOT 5c: if (0) next = GOT 30c;

RETURN 5c: next = IDLE:

else if (D) next - GOT 15c.

else if (N) next = GOT 10c;

default: next = IDLE;

else next = GOT 5c;

endcase

GOT_10c: if (Q) next = GOT_35c;

else if (D) next = GOT_20c;

else if (N) next = GOT_15c;

Combinational output assignment

else next = GOT 10c;

GOT_15c: if (Q) next = GOT_40c;

assign DC = (state == GOT_30c || state == GOT_35c |

else if (D) next = GOT 25c;

state == GOT 40c | state == GOT 45c |

else if (N) next = GOT_20c;

state == GOT 50c);

assign DN = (state == RETURN_5c);

else next = GOT 15c;

assign DD = (state == RETURN_20c || state == RETURN_15c ||

GOT 20c: if (Q) next = GOT 45c;

state == RETURN 10c);

else if (D) next = GOT 30c;

else if (N) next = GOT_25c;

else next = GOT_20c;

```

6.111 Faii 2010 39 9/26/2018 6.111 Fall 2018 40

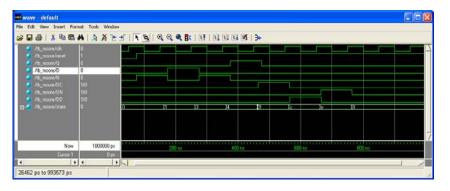

#### Simulation of Moore Vender

9/26/2018 6.111 Fall 2018

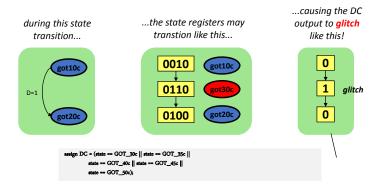

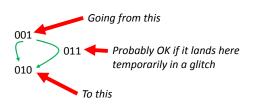

#### FSM Output Glitching

- FSM state bits may not transition at precisely the same time

- Combinational logic for outputs may contain hazards

- Result: your FSM outputs may glitch!

If the soda dispenser is glitch-sensitive, your customers can get a 20-cent soda!

9/26/2018 6.111 Fall 2018 42

# One way to fix Glitches:

- Don't have to have state 3 (3'b011) go into state 4 (3'b100). Use different state naming/use different numbers!!! A rose by any other name would smell as sweet

- Perhaps a Gray code (??):

- Count up like: 000, 001, 011, 010, 110, 111, 101, 100, ...

- Have the really important/glitch-sensitive states only require transistions of one bit

- One-hot encoding:

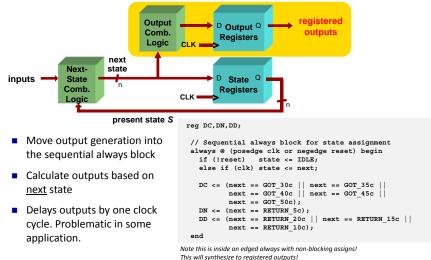

#### Another Solution: Registered FSM Outputs are Glitch-Free

44

9/26/2018 6.111 Fall 2018 43 9/26/2018 6.111 Fall 2018

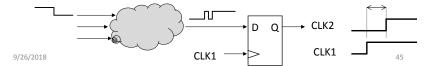

#### Where should CLK come from?

- Option 1: external crystal

- Stable, known frequency, typically 50% duty cycle

- Option 2: internal signals

- Option 2A: output of combinational logic

- No! If inputs to logic change, output may make several transitions before settling to final value → several rising edges, not just one! Hard to design away output glitches...

- Option 2B: output of a register

- Okay, but timing of CLK2 won't line up with CLK1