## M A S S A C H U S E T T S I N S T I T U T E O F T E C H N O L O G Y DEPARTMENT OF ELECTRICAL ENGINEERING AND COMPUTER SCIENCE

## 6.111 Introductory Digital Systems Laboratory

Fall 2018 Lecture PSet #6 of 8 Due: Wed 10/3/2018 upload by 23:59

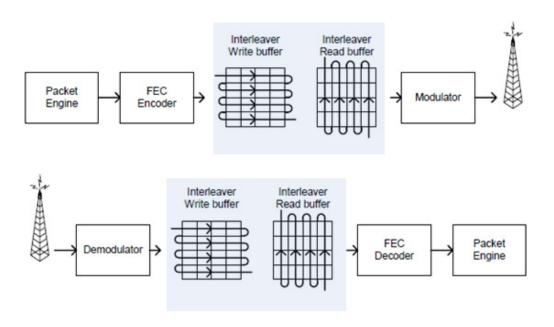

This LPset is the second part of a 4 part LPset designing and implementing a digital communications system. It is based on an actual FPGA implementation for a low power wireless ECG monitor attached to a patient and transmitting to a receiver at a nurse base station. The Interleaver module was the first part. This problem is focused on the Cyclic Redundancy Check (CRC) algorithm that is the front end of the FEC (Forward Error Correction) encoder. This LPset requires ISE.

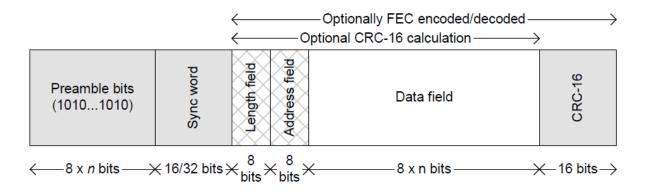

A typical transmitted data packet is show below.

The preamble bits and sync word are used by the receiver for synchronization. For this problem, you will only be concerned with the three blocks of data consisting of the Length Field, Address Field and Data Field. FEC, forward error correction, is a technique that allows a receiver to correct errors in a received packet by convolving the data and sending the parity bits. More on FEC in Lpset #7.

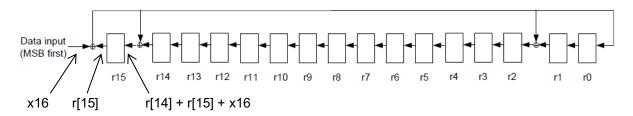

Cyclic Redundancy Check (CRC) is used to detect errors in data transmission and is capable of detecting all single and double errors and many multiple errors with a small number of bits. CRC is generated by a modulo 2 division with a generator polynomial. The remainder is the CRC. For our application, the generator polynomial is CRC16 (x16 + x15 + x2 + 1) with the CRC register initialized to all 1's prior to calculating the CRC. [CRC16 is the generator polynomial for data packets in the USB: <a href="https://www.usb.org/sites/default/files/crcdes.pdf">https://www.usb.org/sites/default/files/crcdes.pdf</a>.] Initializing to all 1's ensures that leading 0s in front of a packet are protected by the CRC. The figure below shows the shift register implementation for the CRC.

In the shift register implementation, each "r" is a register, all clocked with a common clock. The common clock is NOT shown. The small round circles with the plus sign in the diagram are adders implemented with XOR gates. As shown, for register r15, the input is the sum of r[14], r[15] and data input x16; and the output is r[15].

You can see from the location of the XOR gates (input to r15, r2 and r0, equivalent to a generator polynomial 0x8005) in the shift register configuration how CRC16 (x16 + x15 + x2 + 1) is implemented. The data input is x16 with the most significant *bit* (MSB) shifted in first. With each clock pulse, the next data bit is provided to x16. Using this hardware will give the following result:

Input: [4 bytes] **03 01 02 03**Appended with CRC: [6 bytes] **03 01 02 03 30 3A**

In this example the first six data bits sent to x16 are six zero followed by two ones [03]. After 32 bits are shifted in, the value in r[15:0] is the CRC [30 3A].

The CRC calculation is such that sending the data and appended CRC (6 bytes) through the same hardware used to generate the CRC will give a CRC of [00]. (Engineers are clever!)

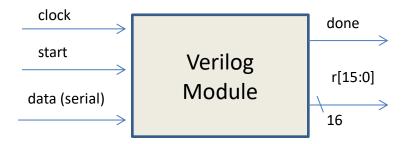

**Problem:** Write a Verilog module that takes the data, run it through the CRC generator and calculates the CRC. Be sure to name the module lpset6.v. – it's the name the testbench is expecting. The input **start** pulses high for one clock cycle when data is available. When CRC calculation is completed, done is asserted with r[15:0] containing the CRC for the incoming data. Since the data input has the CRC appended, the resultant CRC is [00]. Be sure to initialize

r[15:0] to 16'hFFFF at the start. For performance, done must be assert as soon as the all 48 bits are processed (i.e. same clock edge).

data input 48'h03 01 02 03 30 3A

## Getting started:

**Step 1:** Using ISE, create a new Verilog module with inputs and outputs as shown above.

**Step 2:** The Verilog module: when **start** is asserted (one clock pulse wide), reset your FSM; reset counters and other registers; and load any initial values. With each following clock pulse, begin the CRC calculation. Assert **done** when 48 bits are processed. The module should use only one clock domain always @(posedge clock).

**Step 3:** Using ISE and the attached test bench (also posted on the course website) verify your design with a simulation using the process outlined in Lab 2 exercise 1(b). The test bench includes a 5ns clock. Note the syntax [@posedge] for a test bench is slightly different than a Verilog module. The input data is 48'h03\_01\_02\_03\_30\_3A and sent one bit at time. The first eight bits sent to the Verilog module are six zero followed by two ones corresponding to hex [03]. You may modify the test bench if needed for your implementation (generally not the case). In the actual FPGA ECG implementation, the data length is variable and processed one byte at a time.

**Step 4:** Take a screen shot showing r[15:0] after 32 bits are shifted in and a screen shot showing r[15:0] when **done** is asserted. Use hex radix for r[15:0]. Include the Verilog and screen shots in one pdf file. Upload to the course website.

Lpset grading rubric

| Grading |                                                                        |

|---------|------------------------------------------------------------------------|

| 1       | Easy to read & formatted Verilog (See "Verilog Editors" tab for help.) |

| 1       | Correct use of blocking/non-blocking assignments                       |

| 1       | Comments in Verilog when needed                                        |

| 3       | Functional Verilog & test bench                                        |

| 2       | Screen Shot 1 r[15:0] after 32 bits are shifted in                     |

| 2       | Screen Shot 2 r[15:0] when <b>done</b> is asserted                     |

| 10      | Total Grade                                                            |

In simulation, state values are unknown unless explicitly set. (Unknown values are shown in red during simulation. Outputs not defined are shown in blue.) For a simulation to run correctly, state variables must be initialized or set to some value at some point in the simulation. This can be accomplished by using a reset (recommended) or other input. For the CRC you can use the **start** pulse to initialize the CRC:

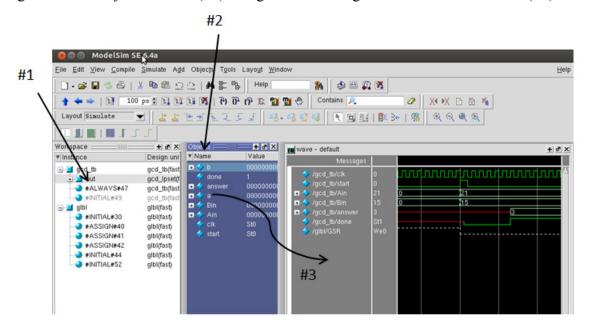

In simulation, by default, only inputs and outputs from the unit under test are displayed in the Wave window. It may be useful to display internal wires in your module that are not inputs nor outputs, for example, a bit counter. After running the initial simulation, to display the internal wires, click "uut" (unit under test) in the Workspace window (#1). This will display the internal signals in the Object window (#2). Drag the desired signals to the Wave window (#3).

To display the additional signals, rerun the simulation. In the Transcript window, type

```

restart -f

// force a restart

run 2000ns

// run simulation for 2000ns (longer if needed)

`timescale 1ns / 1ps

// lpset CRC test bench 9/29/2017

module crc tf;

// Inputs

reg clock;

reg data clk;

reg start;

reg data;

// Outputs

wire done;

wire [15:0] r;

// Instantiate the Unit Under Test (UUT)

lpset6 uut (

.clock(clock),

.start(start),

.data(data),

.done(done),

.r(r)

);

```

```

// this is the input data

reg [47:0] input data = 48'h03 01 02 03 30 3A;

integer i;  // required for "for" loop

initial begin // system clock

forever #5 clock = !clock;

end

initial begin // data clk, ensures setup time met

forever #5 data clk = !data clk;

end

initial begin

// Initialize Inputs

clock = 0;

data clk = 0;

start = 0;

data = 0;

// Wait 100 ns for global reset to finish

#100;

// Add stimulus here

start=1;

#10 start = 0;

#5; // change if necessary for your design

//forever #5 data clk = !data clk;

for (i=0; i<48; \overline{i}=i+1)

begin

data = input data[47];

// at each clock, left shift the data

// note syntax for test bench "for" loop - no "always"

// note the blocking assignment (immediate)

@(posedge data clk) input data = {input data[46:0],1'b0};

end

$stop; // Pause simulation

end

endmodule

```

A link to the test bench is posted on the course website.

You can verify your design with different inputs by comparing your results with a CRC calculator website <a href="http://www.sunshine2k.de/coding/javascript/crc/crc">http://www.sunshine2k.de/coding/javascript/crc/crc</a> js.html.

```

Select CRC-16, use custom CRC parameterization:

Uncheck "Input reflected", uncheck "Result reflected"

Polynomial 0x8005

Initial value 0xFFFF

Final XOR value 0x0000

CRC input data (bytes) 0x03 0x01 0x02 0x03 0x30 0x3a

```