# **FPGA Neural Networks**

Hardware Neural Net Entertainment System (HNES)

Sebastian Bartlett, Josh Noel

### **Project Overview**

Motivation: Applications of ML on FPGA is an active area of research

Inference on Feed-Forward network topology

Interface to PC for network inputs & outputs

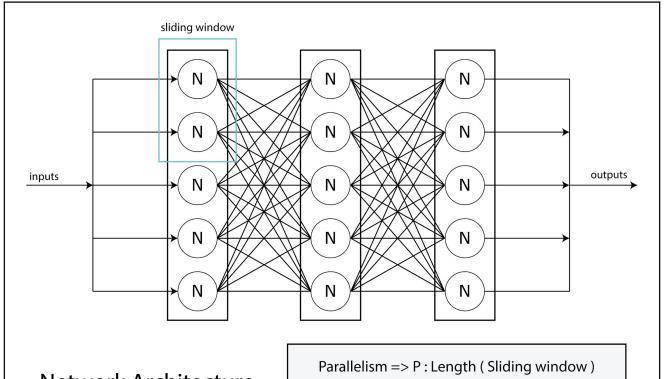

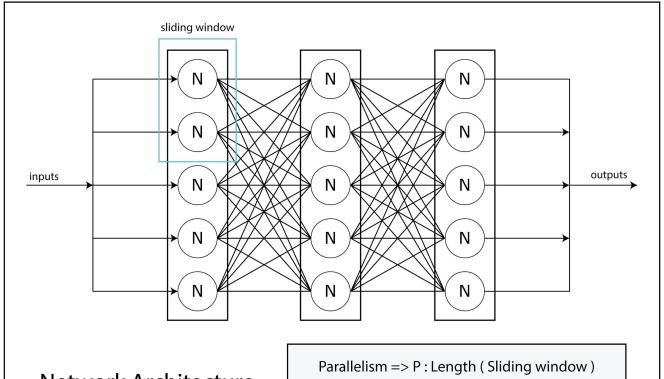

Network Architecture (conceptual, not module)

Network Depth => D : Length ( Layers )

Network Width => W : Length ( Nodes Per Layer )

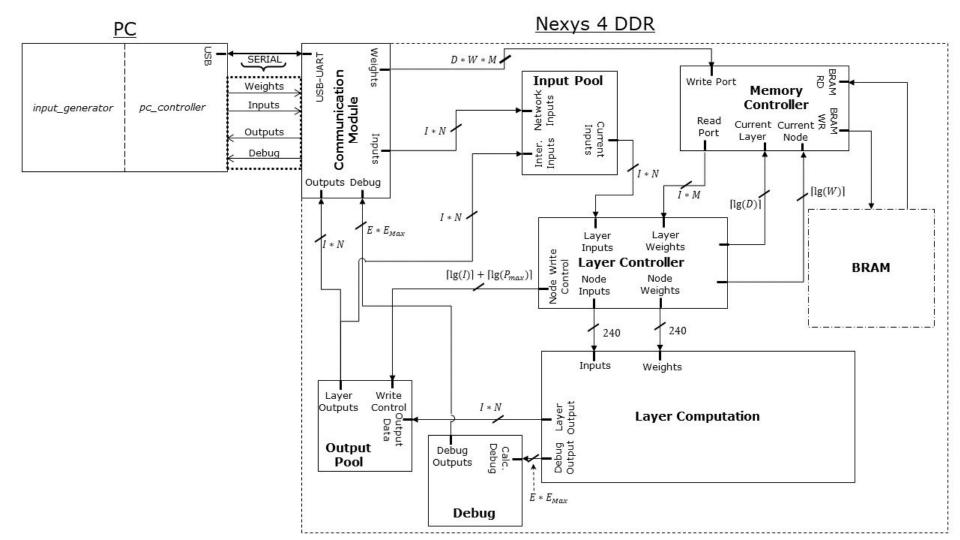

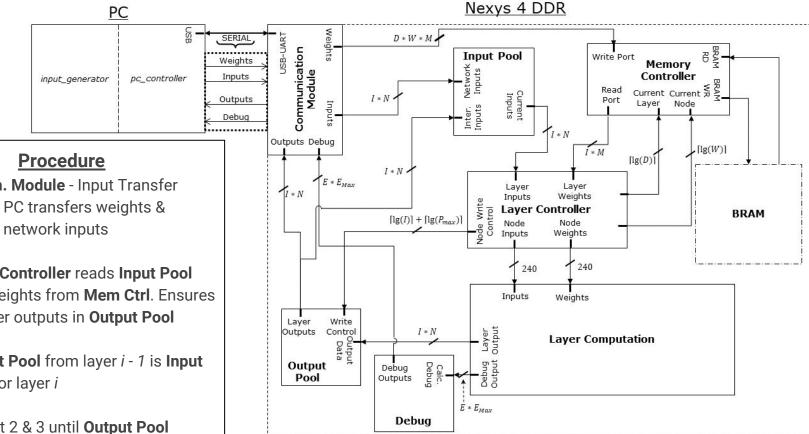

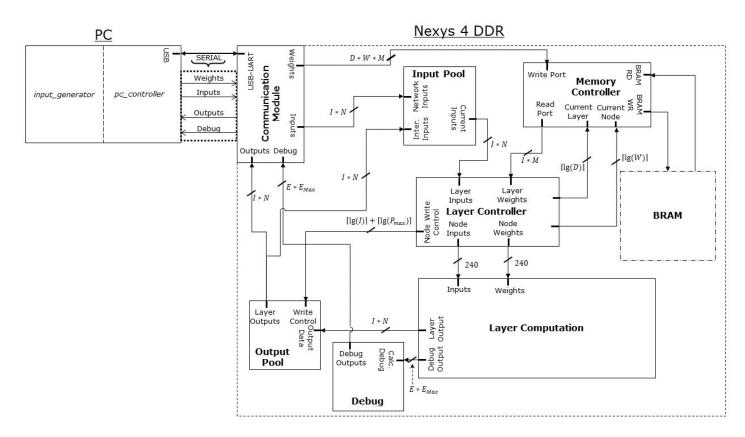

#### Implementation Overview

#### **Procedure**

- **Comm. Module** Input Transfer

- network inputs

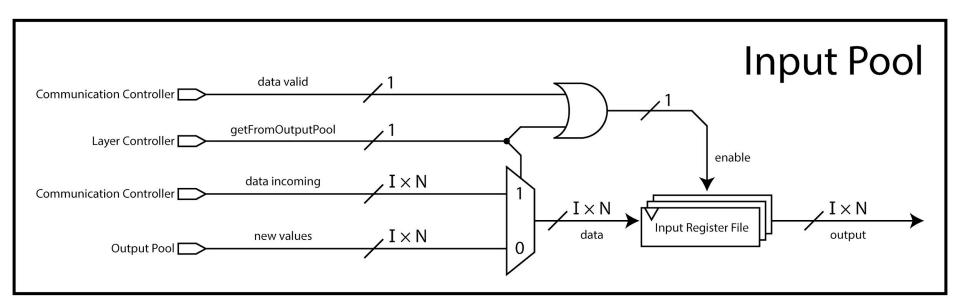

- **Layer Controller reads Input Pool** and weights from Mem Ctrl. Ensures all layer outputs in **Output Pool**

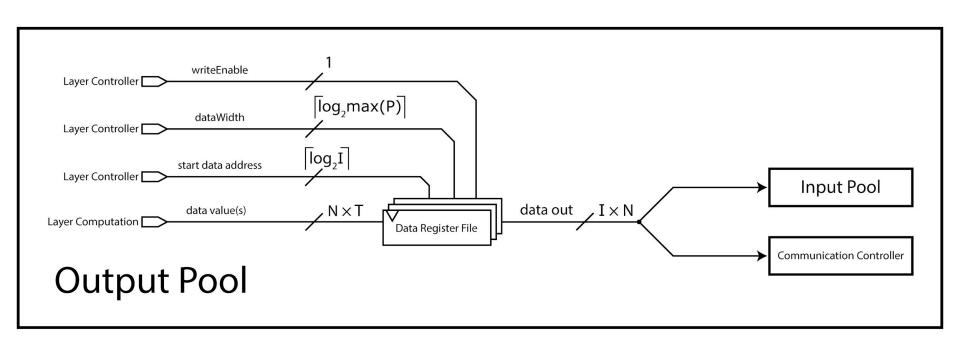

- **Output Pool** from layer *i* 1 is **Input Pool** for layer *i*

- Repeat 2 & 3 until **Output Pool** contains network outputs

- 5. Comm. Module - Output Transfer

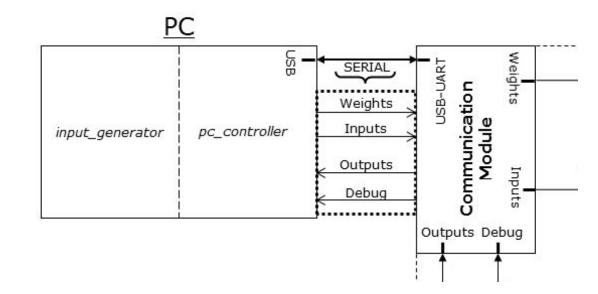

# Communication Module

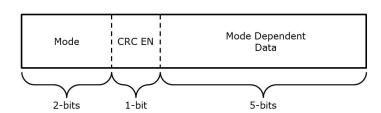

Communication over USB-UART - 10 bit data packets

Packet Stream: [Header, 9 data packets]

Header defines data packet type

Must divide data across multiple packets

#### Packet Stream Header

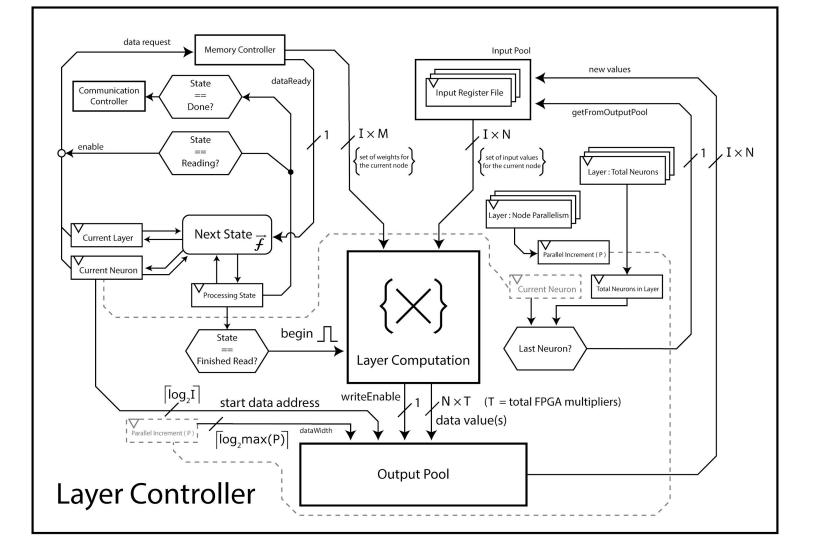

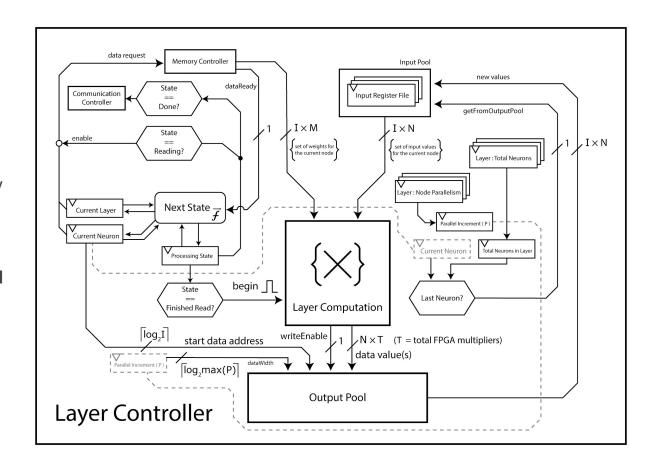

#### Layer Controller

Controls all state transfers

Routes input pool & weight memory reads to **Layer Computation**

Routes **Layer Computation** output to correct addresses in **Output Pool**

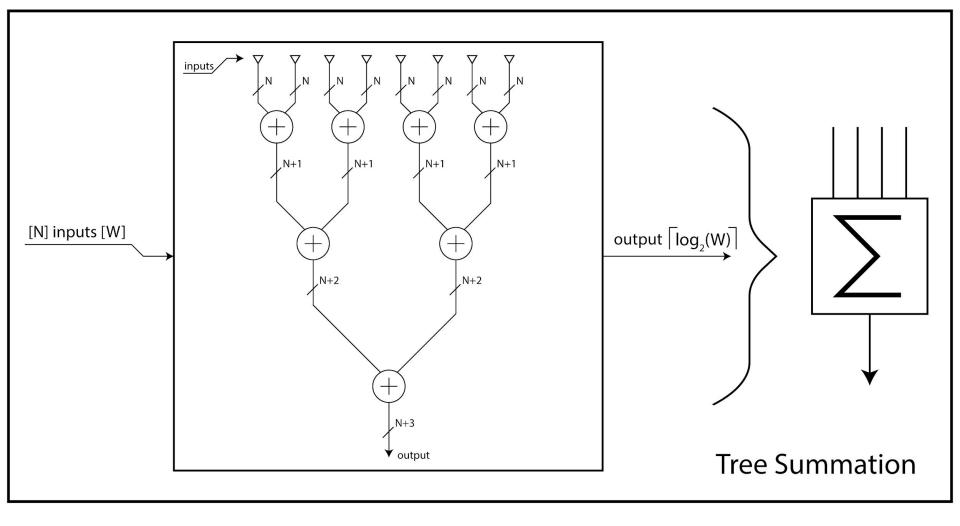

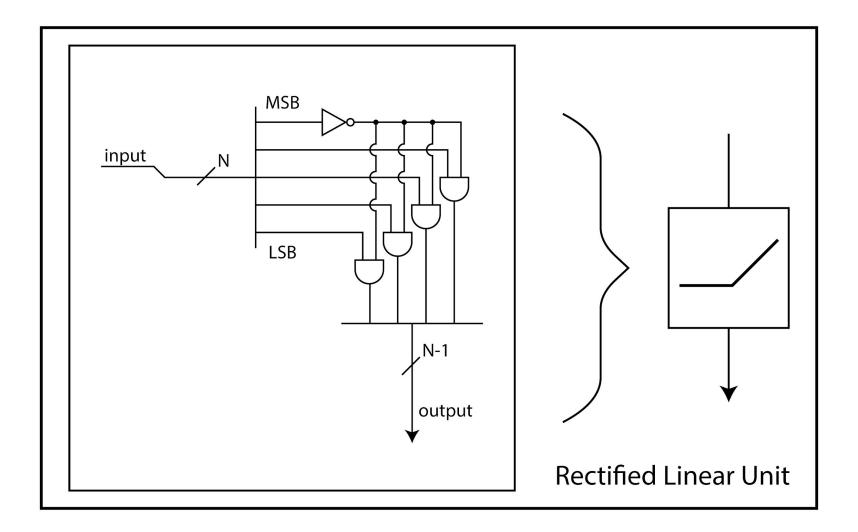

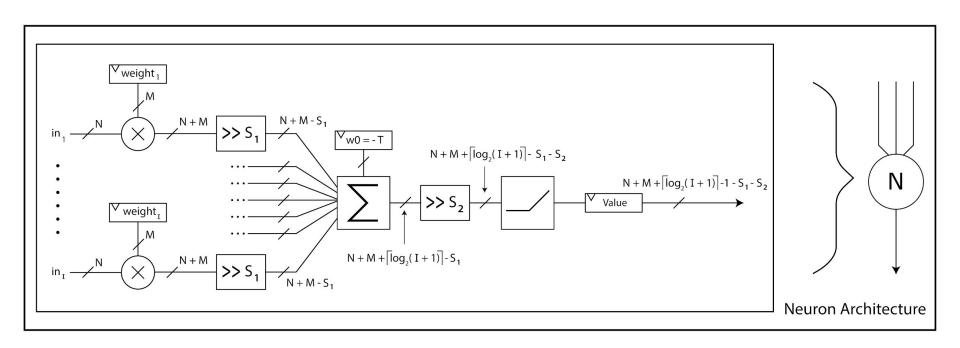

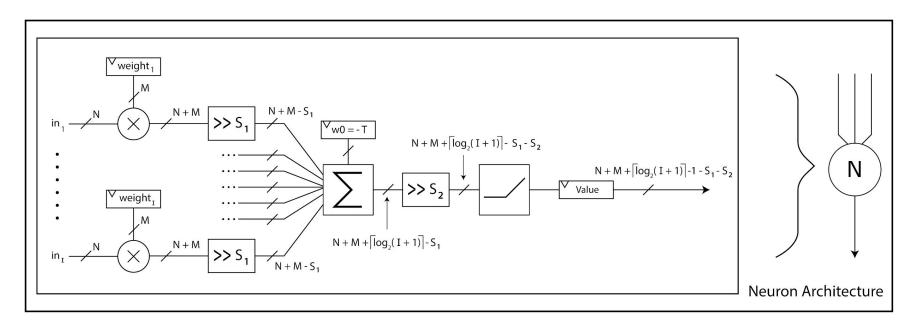

### **Layer Computation Module**

# of neurons calculated at once (parallelism) is bounded by DSP slices

Network Architecture (conceptual, not module)

Network Depth => D : Length ( Layers )

Network Width => W : Length ( Nodes Per Layer )

#### Timeline

- 11/16 Module Implementation

- 11/30 Module Debugging, Integration Testing

- 12/10 Neural Network Application and Implementation

- Base Goals

- Calculate single layer outputs based off PC inputs

- FPGA behaves as a hardware matrix multiplier

- Calculate output layer of multilayer feed-forward network

- This requires calculating intermediate (hidden) layers

- This enables inference to be performed

- More complex topologies can be interfaced on PC-side

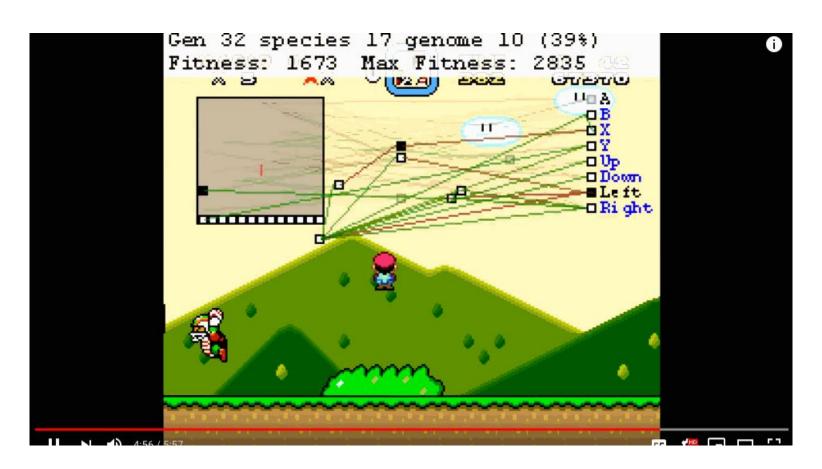

- Stretch Goal

- Interface with NES emulator to play Super Mario

Mar I/O by "SethBling" (YouTube)

#### Questions?

## (Reference Slides)

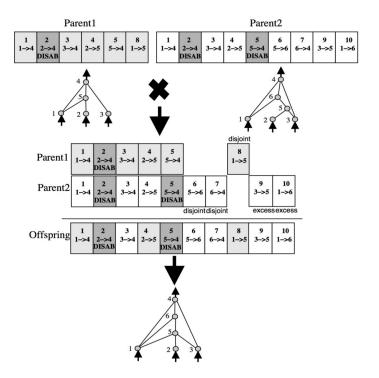

#### Source: Evolving Neural Networks through Augmenting Topologies

Kenneth O. Stanley kstanley@cs.utexas.edu Department of Computer Sciences, The University of Texas at Austin, Austin, TX 78712, USA

Risto Miikkulainen risto@cs.utexas.edu Department of Computer Sciences, The University of Texas at Austin, Austin, TX 78712, USA