# Logic Synthesis

- Primitive logic gates, universal gates

- Truth tables and sum-of-products

- Logic simplification

- Karnaugh Maps, Quine-McCluskey

- General implementation techniques: muxes and look-up tables (LUTs)

Reminder: Lab #1 due this Thursday!

6.111 Fall 2016

Lecture 2

6 111 Fc

#### Late Policies

- Lab 1 check-offs sign-up on checkoff queue in lab FIFO during staffed lab hours.

- Please don't assume that you can wait until the last minute!

- No check-offs on Friday or Saturday

- Lab grade = Checkoff + Verilog grade (equal weighting)

- On-time check-off:

- 20%/day late penalty (no penalty for Friday or Saturday)

- Max penalty 80% reduction.

- All labs must be checked off before you can start your final project. We've learned that if you're struggling with the labs, the final project won't go very well.

- · Lpset must be submitted on time.

6.111 Fall 2016 Lecture 2 2

# Schematics & Wiring

- IC power supply connections generally not drawn. All integrated circuits need power!

- Use standard color coded wires to avoid confusion.

- -red: positive

- -black: ground or common reference point

- -Other colors: signals

- · Circuit flow, signal flow left to right

- Higher voltage on top, ground negative voltage on bottom

- Neat wiring helps in debugging!

# Wire Gauge

- Wire gauge: diameter is inversely proportional to the wire gauge number.

Diameter increases as the wire gauge decreases. 2, 1, 0, 00, 000(3/0) up to 7/0.

- Resistance

- -22 gauge .0254 in 16 ohm/1000 feet

- -12 gauge .08 in 1.5 ohm/1000 feet

- -High voltage AC used to reduce loss

- 1 cm cube of copper has a resistance of 1.68 micro ohm (resistance of copper wire scales linearly: length/area)

6.111 Fall 2016 3 6.111 Fall 2016 4

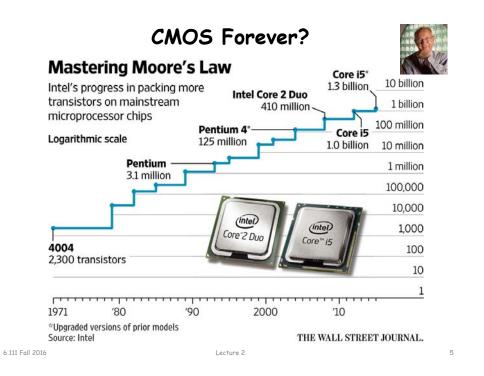

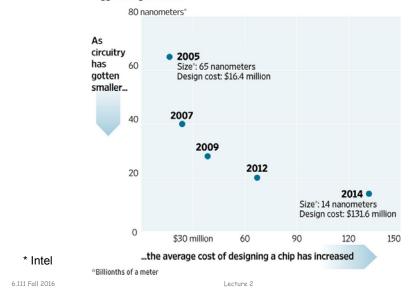

#### Diminishing Returns \*

Creating smaller circuitry has placed more transistors on chips but triggered higher costs.

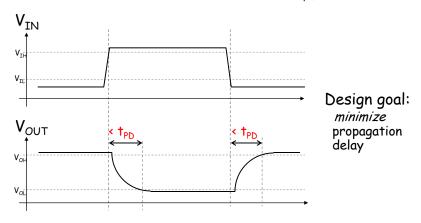

# Timing Specifications

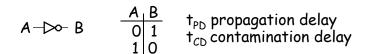

Propagation delay (t<sub>PD</sub>): An <u>upper bound</u> on the delay from valid inputs to valid outputs (aka "t<sub>PD.MAX</sub>")

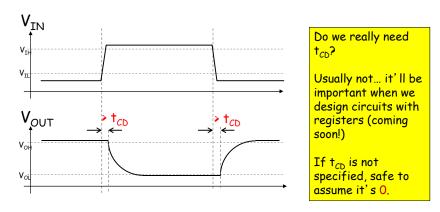

# Contamination Delay

an optional, additional timing spec

Contamination delay( $t_{CD}$ ): A <u>lower bound</u> on the delay from invalid inputs to invalid outputs (aka " $t_{PD,MIN}$ ")

6.111 Fall 2016 Lecture 2 7 6.111 Fall 2016 Lecture 2

## The Combinational Contract

- 1. No Promises during XXXXX

- 2. Default (conservative) spec:  $t_{CD} = 0$

6.111 Fall 2016 Lecture 2

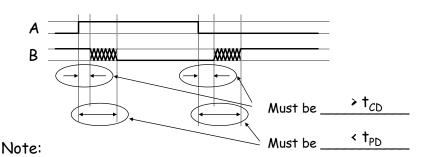

# Functional Specifications

| Α | В | С | У |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

|   |   |   |   |

3 binary inputs so  $2^3 = 8$  rows in our truth table

An concise, unambiguous technique for giving the functional specification of a combinational device is to use a *truth table* to specify the output value for each possible combination of input values (N binary inputs ->  $2^N$  possible combinations of input values).

6.111 Fall 2016 Lecture 2 10

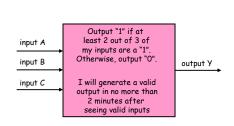

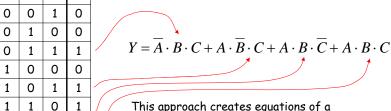

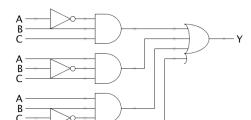

# Here's a Design Approach

- Write out our functional spec as a truth table

- 2. Write down a Boolean expression with terms covering each '1' in the output:

This approach creates equations of a particular form called

#### SUM-OF-PRODUCTS

$A \mid B \mid C \mid Y$

0 0

Sum (+): ORs

Products (•): ANDs

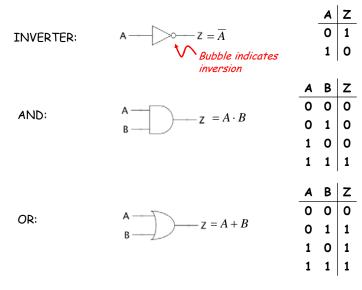

# S-O-P Building Blocks

# Straightforward Synthesis

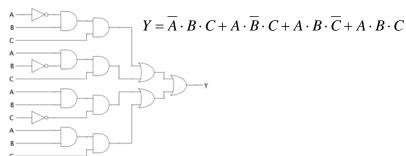

$Y = \overline{A} \cdot B \cdot C + A \cdot \overline{B} \cdot C + A \cdot B \cdot \overline{C} + A \cdot B \cdot C$

We can use

SUM-OF-PRODUCTS to implement *any* logic function.

Only need 3 gate types: INVERTER, AND, OR

Propagation delay:

No more than 3 gate delays assuming gates with an arbitrary number of inputs. But, in general, we'll only be able to use gates with a bounded number of inputs (bound is ~4 for most logic families).

6.111 Fall 2016 Lecture 2 13

# SOP w/ 2-input gates

Previous example restricted to 2-input gates:

Lecture 2

|                 | INV         | AND2 | OR2  |

|-----------------|-------------|------|------|

| † <sub>PD</sub> | 8p <i>s</i> | 15ps | 18ps |

| † <sub>C</sub>  | 1ps         | 3ps  | 3ps  |

6,111 Fall 2016

Using the timing specs given to the left, what are  $t_{PD}$  and  $t_{CD}$  for this combinational circuit?

Hint: to find overall  $t_{PD}$  we need to find max  $t_{PD}$  considering all paths from inputs to outputs.

## ANDs and ORs with > 2 inputs

# More Building Blocks

| NAND (not AND)                                                                                              | A | В | z | NOR (not OR)           | A | В | Z |

|-------------------------------------------------------------------------------------------------------------|---|---|---|------------------------|---|---|---|

|                                                                                                             | 0 | 0 | 1 | NOR (NOT OR)           |   | 0 | 1 |

| A —                                                                                                         | 0 | 1 | 1 | A                      | 0 | 1 | 0 |

| $\begin{array}{c} A \\ B \end{array} \longrightarrow \begin{array}{c} Z = \overline{A \cdot B} \end{array}$ | 1 | 0 | 1 | $z = \overline{A + B}$ | 1 | 0 | 0 |

|                                                                                                             | 1 | 1 | 0 |                        | 1 | 1 | 0 |

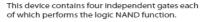

CMOS gates are naturally inverting so we want to use NANDs and NORs in CMOS designs...

| XOR (exclusive OR)   | A | В | Z | XOR is very useful when implementing                                         |

|----------------------|---|---|---|------------------------------------------------------------------------------|

|                      | 0 | 0 | 0 | parity and arithmetic logic. Also used as a "programmable inverter": if A=0, |

| $A = Z = A \oplus B$ | 0 | 1 | 1 | Z=B; if A=1, Z=~B                                                            |

| B //                 | 1 | 0 | 1 | Wide for in VODs can be asseted with                                         |

|                      | 1 | 1 | 0 | Wide fan-in XORs can be created with chains or trees of 2-input XORs.        |

15 6.111 Fall 2016 Lecture 2 16

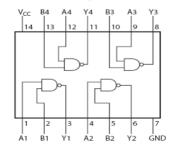

## NAND - NOR Internals

#### Dual-In-Line Package

#### 6.111 Fall 2016 Lecture 2 17

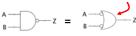

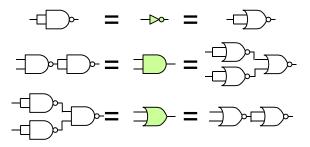

## SOP with NAND/NOR

When designing with NANDs and NORs one often makes use of De Morgan's laws:

NAND form:  $\overline{A \cdot B} = \overline{A} + \overline{B}$

NOR form:  $\overline{A+B} = \overline{A} \cdot \overline{B}$

So the following "SOP" circuits are all equivalent (note the use of De Morgan-ized symbols to make the inversions less confusing):

NAND/NAND form

This will be handy in Lab 1.

This will be handy in Lab 1 since you'll be able to use just 7400's to implement your circuit!

#### NOR/NOR form

All these "extra" inverters may seem less than ideal but often the buffering they provide will reduce the capacitive load on the inputs and increase the output drive.

## Universal Building Blocks

NANDs and NORs are universal:

Any logic function can be implemented using only NANDs (or, equivalently, NORs). Note that chaining/treeing technique doesn't work directly for creating wide fan-in NAND or NOR gates. But wide fan-in gates can be created with trees involving both NANDs, NORs and inverters.

#### 6.111 Fall 2016 Lecture 2

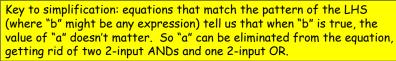

# Logic Simplification

- Can we implement the same function with fewer gates? Before trying we'll add a few more tricks in our bag.

- BOOLEAN ALGEBRA:

OR rules: a+1=1 a+0=a a+a=aAND rules:  $a\cdot 1=a$   $a\cdot 0=0$   $a\cdot a=a$ Commutative: a+b=b+a  $a\cdot b=b\cdot a$

Associative: (a+b)+c=a+(b+c)  $(a\cdot b)\cdot c=a\cdot (b\cdot c)$ Distributive:  $a\cdot (b+c)=a\cdot b+a\cdot c$   $a+b\cdot c=(a+b)\cdot (a+c)$

Complements:  $a + \overline{a} = 1$   $a \cdot \overline{a} = 0$

**Absorption:**  $a+a\cdot b=a$   $a+\overline{a}\cdot b=a+b$   $a\cdot (a+b)=a$   $a\cdot (\overline{a}+b)=a\cdot b$

De Morgan's Law:  $\overline{a \cdot b} = \overline{a} + \overline{b}$   $\overline{a + b} = \overline{a} \cdot \overline{b}$ Reduction:  $\overline{a \cdot b + \overline{a} \cdot b = b}$   $(a + b) \cdot (\overline{a} + b) = b$

## **Boolean Minimization:**

An Algebraic Approach

Lets simplify the equation from slide #3:

$$Y = \overline{A} \cdot B \cdot C + A \cdot \overline{B} \cdot C + A \cdot B \cdot \overline{C} + A \cdot B \cdot C$$

Using the identity

$$\alpha A + \alpha \overline{A} = \alpha$$

For any expression  $\alpha$  and variable A:

$$Y = \overline{A} \cdot B \cdot C + A \cdot \overline{B} \cdot C + A \cdot B \cdot \overline{C} + A \cdot B \cdot C$$

$$Y = B \cdot C + A \cdot C + A \cdot B$$

The tricky part: some terms participate in more than one reduction so can't do the algebraic steps one at a time!

6.111 Fall 2016

Lecture 2

21

23

6.111 Fall 2016

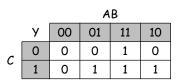

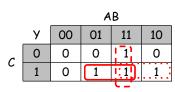

#### Karnaugh Maps: A Geometric Approach

K-Map: a truth table arranged so that terms which differ by exactly one variable are adjacent to one another so we can see potential reductions easily.

| Α | В | С | У |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

Here's the layout of a 3-variable K-map filled in with the values from our truth table:

Why did hishade that row Gray?

It's cyclic. The left edge is adjacent to the right edge. It's really just a flattened out cube.

6,111 Fall 2016 Lecture 2

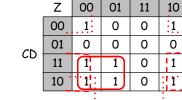

# On to Hyperspace

Here's a 4-variable K-map:

|    |    | AB |    |    |    |  |

|----|----|----|----|----|----|--|

|    | Z  | 00 | 01 | 11 | 10 |  |

|    | 00 | 1  | 0  | 0  | 1  |  |

| CD | 01 | 0  | 0  | 0  | 0  |  |

|    | 11 | 1  | 1  | 0  | 1  |  |

|    | 10 | 1  | 1  | 0  | 1  |  |

Again it's cyclic. The left edge is adjacent to the right edge, and the top is adjacent to the bottom.

We run out of steam at 4 variables - K-maps are hard to draw and use in three dimensions (5 or 6 variables) and we're not equipped to use higher dimensions (> 6 variables)!

# Finding Subcubes

We can identify clusters of "irrelevent" variables by circling adjacent subcubes of 1s. A subcube is just a lower dimensional cube.

Three 2x1 subcubes

Three 2x2 subcubes

The best strategy is generally a greedy one.

- Circle the largest N-dimensional subcube ( $2^N$  adjacent 1's)

4x4, 4x2, 4x1, 2x2, 2x1, 1x1

- Continue circling the largest remaining subcubes (even if they overlap previous ones)

- Circle smaller and smaller subcubes until no 1s are left.

6.111 Fall 2016 Lecture 2

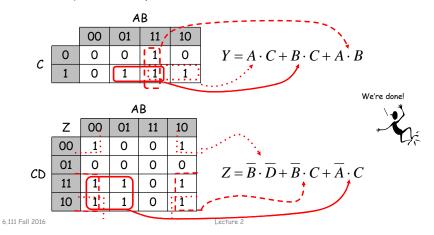

# Write Down Equations

Write down a product term for the portion of each cluster/subcube that is invariant. You only need to include enough terms so that all the 1's are covered. Result: a minimal sum of products expression for the truth table.

#### Two-Level Boolean Minimization

Two-level Boolean minimization is used to find a sum-of-products representation for a multiple-output Boolean function that is optimum according to a given cost function. The typical cost functions used are the number of product terms in a two-level realization, the number of literals, or a combination of both. The two steps in two-level Boolean minimization are:

•Generation of the set of prime product-terms for a given function.

•<u>Selection</u> of a minimum set of prime terms to implement the function.

We will briefly describe the Quine-McCluskey method which was the first algorithmic method proposed for two-level minimization and which follows the two steps outlined above. State-of-the-art logic minimization algorithms are all based on the Quine-McCluskey method and also follow the two steps above.

6.111 Fall 2016 Lecture 2 26

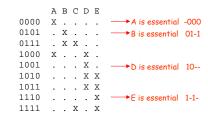

#### Prime Term Generation

Start by expressing your Boolean function using 0-terms (product terms with no don't care care entries). For compactness the table for example 4-input, 1-output function F(w,x,y,z) shown to the right includes only entries where the output of the function is 1 and we've labeled each entry with it's decimal equivalent.

27

Look for pairs of 0-terms that differ in only one bit position and merge them in a 1-term (i.e., a term that has exactly one '-' entry). Next 1-terms are examined in pairs to see if the can be merged into 2-terms, etc. Mark k-terms that get merged into (k+1) terms so we can discard them later.

| 1-terms:                        | 5, 7                   | -000 [A]<br>01-1 [B]<br>-111 [C] | <b>2-terms:</b> 8, 9,10,11 10[D] 10,11,14,15 1-1-[E] |

|---------------------------------|------------------------|----------------------------------|------------------------------------------------------|

|                                 | 8,10                   | 100-<br>10-0                     | 3-terms: none!                                       |

| Example due to<br>Srini Devadas | 9,11<br>10,11<br>10,14 |                                  | Label unmerged terms:<br>these terms are prime!      |

| 6.111 Fall 2016                 | 11,15<br>14,15         |                                  | Lecture 2                                            |

#### Prime Term Table

An "X" in the prime term table in row R and column K signifies that the 0-term corresponding to row R is contained by the prime corresponding to column K.

Goal: select the minimum set of primes (columns) such that there is at least one "X" in every row. This is the classical minimum covering problem.

28

Each row with a single X signifies an essential prime term since any prime implementation will have to include that prime term because the corresponding 0-term is not contained in any other prime.

In this example the essential primes "cover" all the 0-terms.

$$F = f(W,X,Y,Z) = \overline{X}\overline{Y}\overline{Z} + \overline{W}XZ + W\overline{X} + W\overline{Y}$$

6.111 Fall 2016 Lecture 2

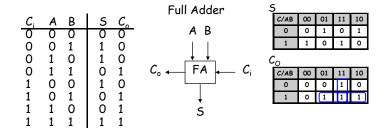

## Logic that defies SOP simplification

$$S = \overline{A} \cdot B \cdot \overline{C} + A \cdot \overline{B} \cdot \overline{C} + \overline{A} \cdot \overline{B} \cdot C + A \cdot B \cdot C = A \oplus B \oplus C_{i}$$

$$C_{O} = A \cdot C + B \cdot C + A \cdot B$$

The sum S doesn't have a simple sum-of-products implementation even though it can be implemented using only two 2-input XOR gates.

6.111 Fall 2016 Lecture 2 29

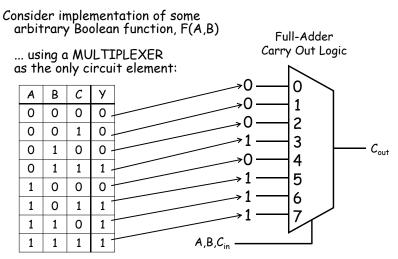

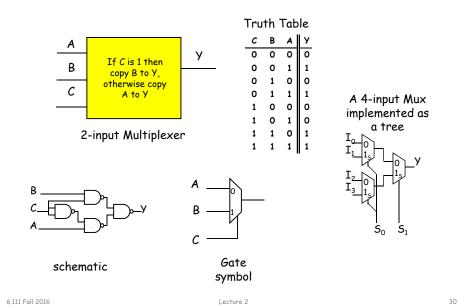

# Systematic Implementation of Combinational Logic

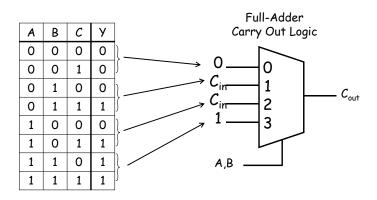

# Logic Synthesis Using MUXes

# Systematic Implementation of Combinational Logic

Same function as on previous slide, but this time let's use a 4-input mux

32

6.111 Fall 2016 Lecture 2 31 6.111 Fall 2016 Lecture 2

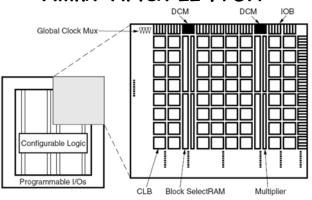

## Xilinx Virtex II FPGA

Virtex-II Architecture Overview

#### XC2V6000:

6,111 Fall 2016

- 957 pins, 684 IOBs

- CLB array: 88 cols x 96/col = 8448 CLBs

- 18Kbit BRAMs = 6 cols x 24/col = 144 BRAMs = 2.5Mbits

- $18 \times 18$  multipliers = 6 cols  $\times$  24/col = 144 multipliers

Figures from Xilinx Virtex II datasheet 6.111 Fall 2016 Lecture 2

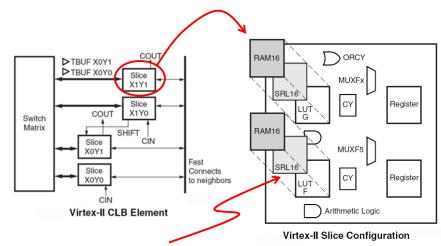

#### Virtex II CLB

16 bits of RAM which can be configured as a 16x1 single- or dual-port RAM, a 16-bit shift register, or a 16-location lookup table

Figures from Xilinx Virtex II datasheet

6.111 Fall 2016 Lecture 2 34

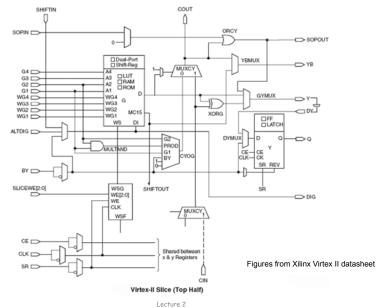

# Virtex II Slice Schematic

35

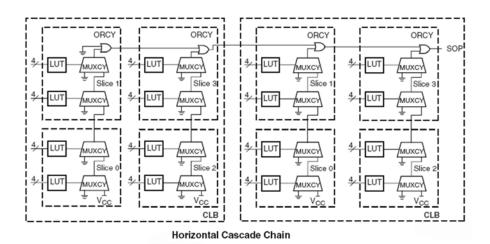

# Virtex II Sum-of-products

Figures from Xilinx Virtex II datasheet

36

6,111 Fall 2016 Lecture 2

# Spartan 6 FPGA

Figure 31: XC6SLX45T Floorplan View in PlanAhead

6.111 Fall 2016 Lecture 2 37

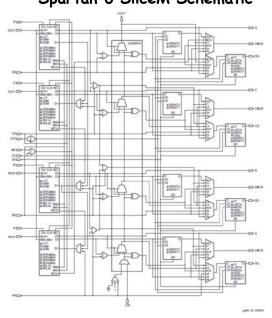

#### Spartan 6 SliceM Schematic

Figures from Xilinx Spartan 6 CLB datasheet

6.111 Fall 2016 Lecture 2 38

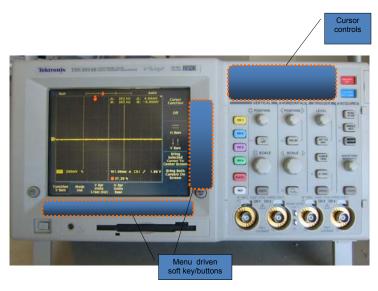

# Oscilloscope

# Oscilloscope Controls

- Auto Set, soft menu keys

- Trigger

- channel,

- slope,

- Level

- Input

- AC, DC coupling,

- 10x probe,

- 1khz calibration source,

- probe calibration,

- bandwidth filter

- Signal measurement

- time,

- frequency,

- voltage

- cursors

- single sweep

- · Image capture

6.111 Fall 2016 39 6.111 Fall 2016 40