# Pipelining & Verilog

- Division

- Latency & Throughput

- Pipelining to increase throughput

- Retiming

- Verilog Math Functions

6 111 Fall 2016 Lecture 9

# Verilog divider.v

```

// The divider module divides one number by another. It

always @( posedge clk ) begin

// produces a signal named "ready" when the quotient output

del_ready <= !bit;

// is ready, and takes a signal named "start" to indicate

if( start ) begin

// the the input dividend and divider is ready.

bit = WIDTH;

// sign -- 0 for unsigned, 1 for twos complement

quotient = 0;

// It uses a simple restoring divide algorithm.

quotient_temp = 0;

// http://en.wikipedia.org/wiki/Division_(digital)#Restoring_division

dividend_copy = (!sign | | !dividend[WIDTH-1]) ?

{1'b0.zeros.dividend}

module divider \#(parameter WIDTH = 8)

{1'b0 zeros ~dividend + 1'b1}

\label{eq:divider_copy} \texttt{divider}[\texttt{WIDTH-1}]) \ ?

(input clk, sign, start,

input [WIDTH-1:0] dividend.

{1'b0.divider.zeros}

input [WIDTH-1:0] divider,

{1'b0,~divider + 1'b1,zeros};

output reg [WIDTH-1:0] quotient

output [WIDTH-1:0] remainder:

negative_output = sign &&

output ready);

((divider[WIDTH-1] && !dividend[WIDTH-1])

| | (!divider[WIDTH-1] && dividend[WIDTH-1]));

reg [WIDTH-1:0] quotient_temp;

reg [WIDTH*2-1:0] dividend_copy, divider_copy, diff;

else if ( bit > 0 ) begin

diff = dividend_copy - divider_copy;

reg negative_output;

quotient_temp = quotient_temp << 1;

wire [WIDTH-1:0] remainder = (!negative_output) ?

if(!diff[WIDTH*2-1]) begin

dividend_copy[WIDTH-1:0] : ~dividend_copy[WIDTH-1:0] + 1'b1;

dividend copy = diff:

quotient_temp[0] = 1'd1;

reg [5:0] bit:

reg del ready = 1:

quotient = (!negative_output) ?

wire ready = (!bit) & ~del_ready;

quotient_temp :

~quotient_temp + 1'b1;

wire [WIDTH-2:0] zeros = 0:

divider\_copy = divider\_copy >> 1;

initial bit = 0;

bit = bit - 1'b1;

initial negative_output = 0;

end

endmodule

```

Lecture 9

6,111 Fall 2016

L. Williams MIT '13

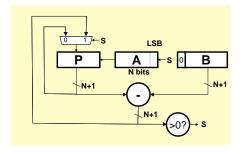

## Sequential Divider

Assume the Dividend (A) and the divisor (B) have N bits. If we only want to invest in a single N-bit adder, we can build a sequential circuit that processes a single subtraction at a time and then cycle the circuit N times. This circuit works on unsigned operands; for signed operands one can remember the signs, make operands positive, then correct sign of result.

6 111 Fall 2016

```

Init: P \leftarrow 0, load A and B

Repeat N times {

shift P/A left one bit

temp = P-B

if (temp > 0)

\{P\leftarrow temp, A_{LSB}\leftarrow 1\}

else A_{LSB} \leftarrow 0

Done: Q in A, R in P

```

Lecture 9

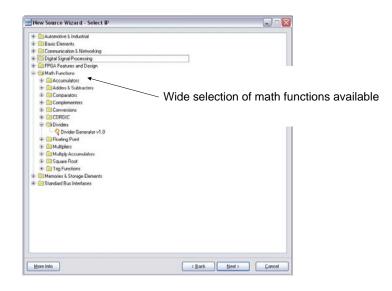

## Math Functions in Coregen

6,111 Fall 2016 Lecture 9

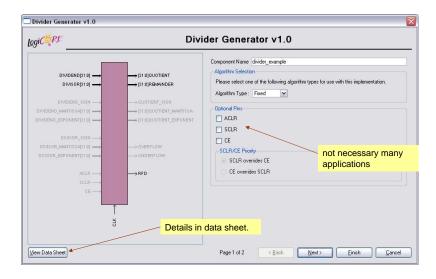

## Coregen Divider

6.111 Fall 2016 Lecture 9 5

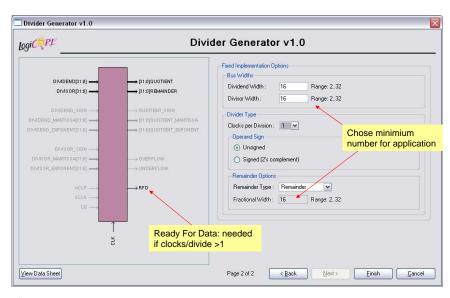

## Coregen Divider

6.111 Fall 2016 Lecture 9

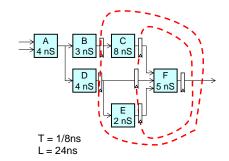

## Performance Metrics for Circuits

Circuit Latency (L): time between arrival of new input and generation of corresponding output.

For combinational circuits this is just  $t_{PD}$ .

Circuit Throughput (T): Rate at which new outputs appear.

For combinational circuits this is just  $1/t_{PD}$  or 1/L.

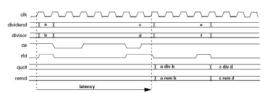

## Coregen Divider Latency

Figure 2: Latency Example (Clocks per Division = 4)

Table 4: Latency of Fixed-point Solution Based on Divider Parameters

| Signed | Fractional | Clks/Div | Latency |  |

|--------|------------|----------|---------|--|

| False  | False      | 1        | M+2     |  |

| False  | False      | >1       | M+3     |  |

| False  | True       | 1        | M+F+2   |  |

| False  | True       | >1       | M+F+3   |  |

| True   | False      | 1        | M+4     |  |

| True   | False      | >1       | M+5     |  |

| True   | True       | 1        | M+F+4   |  |

| True   | True       | >1       | M+F+5   |  |

|        |            |          |         |  |

Latency dependent on dividend width + fractioanl reminder width

Note: M=dividend width, F=fractional remainder width.

The divclk\_sel parameter allows a range of choices of throughput versus area. With divclk\_sel = 1, the core is fully pipelined, so it will have maximal throughput of one division per clock cycle, but will occupy the most area. The divclk\_sel selections of 2, 4 and 8 reduce the throughput by those respective factors for smaller core sizes.

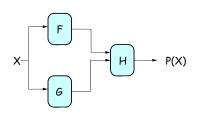

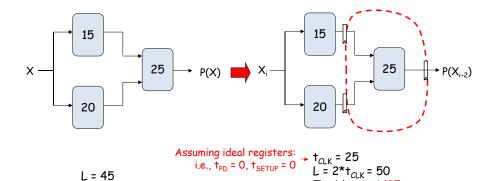

### Performance of Combinational Circuits

For combinational logic:

$$L = t_{PD},$$

$$T = 1/t_{PD}.$$

We can't get the answer faster, but are we making effective use of our hardware at all times?

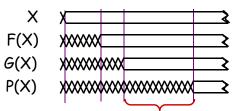

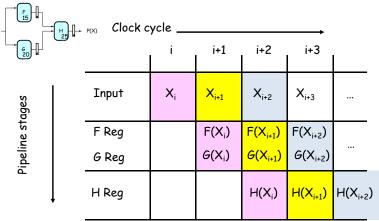

$T = 1/t_{CLK} = 1/25$

F & G are "idle", just holding their outputs stable while H performs its computation

6.111 Fall 2016 Lecture 9

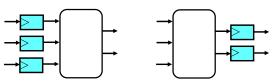

## Retiming: A very useful transform

### Retiming is the action of moving registers around in the system

Registers have to be moved from ALL inputs to ALL outputs or vice versa

Cutset retiming: A cutset intersects the edges, such that this would result in two disjoint partitions of the edges being cut. To retime, delays are moved from the ingoing to the outgoing edges or vice versa.

#### Benefits of retiming:

- Modify critical path delay

- Reduce total number of registers

6.111 Fall 2016 Lecture 9

## Retiming Combinational Circuits aka "Pipelining"

L = 45

T = 1/45

# Pipeline diagrams

The results associated with a particular set of input data moves diagonally through the diagram, progressing through one pipeline stage each clock cycle.

## Pipeline Conventions

#### **DEFINITION:**

a K-Stage Pipeline ("K-pipeline") is an acyclic circuit having exactly K registers on every path from an input to an output.

a COMBINATIONAL CIRCUIT is thus an 0-stage pipeline.

#### CONVENTION:

Every pipeline stage, hence every K-Stage pipeline, has a register on its OUTPUT (not on its input).

#### ALWAYS:

The CLOCK common to all registers must have a period sufficient to cover propagation over combinational paths PLUS (input) register tph PLUS (output) register t<sub>SETUP</sub>.

> The LATENCY of a K-pipeline is K times the period of the clock common to all registers.

> The THROUGHPUT of a K-pipeline is the frequency of the clock.

6.111 Fall 2016 Lecture 9 13

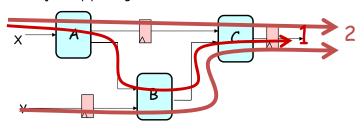

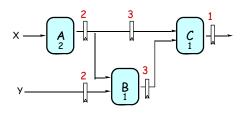

## Ill-formed pipelines

Consider a BAD job of pipelining:

For what value of K is the following circuit a K-Pipeline? \_\_\_\_\_ none

#### Problem:

Successive inputs get mixed: e.g.,  $B(A(X_{i+1}), Y_i)$ . This happened because some paths from inputs to outputs have 2 registers, and some have only 1!

This CAN'T HAPPEN on a well-formed K pipeline!

6.111 Fall 2016 Lecture 9

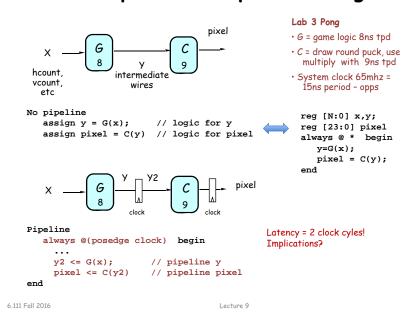

## A pipelining methodology

### Step 1:

Add a register on each output.

### Step 2:

Add another register on each output. Draw a cut-set contour that includes all the new registers and some part of the circuit. Retime by moving regs from all outputs to all inputs of cut-set.

Repeat until satisfied with T.

#### STRATEGY:

Focus your attention on placing pipelining registers around the slowest circuit elements (BOTTLENECKS).

## Pipeline Example

|         | LATENCY | THROUGHPU |

|---------|---------|-----------|

| 0-pipe: | 4       | 1/4       |

| 1-pipe: | 4       | 1/4       |

| 2-pipe: | 4       | 1/2       |

| 3-pipe: | 6       | 1/2       |

- **OBSERVATIONS:**

- 1-pipeline improves neither L or T.

- T improved by breaking long combinational paths, allowing faster clock.

- Too many stages cost L. don't improve T.

- Back-to-back registers are often required to keep pipeline wellformed.

6,111 Fall 2016 6,111 Fall 2016 16 Lecture 9 Lecture 9

## Pipeline Example - Verilog

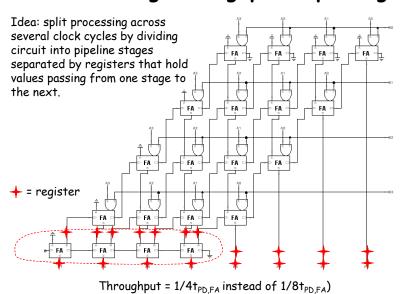

## Increasing Throughput: Pipelining

6.111 Fall 2016 Lecture 9

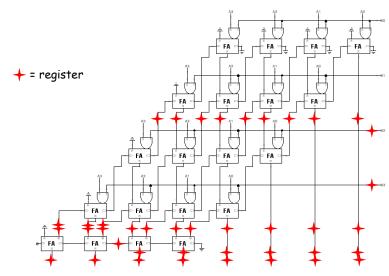

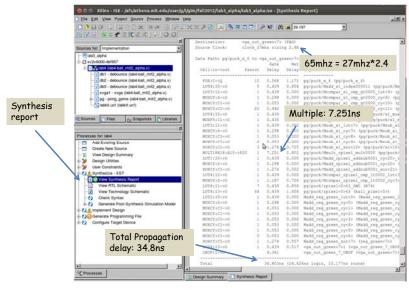

# How about $t_{PD} = 1/2t_{PD,FA}$ ?

## Timing Reports

6.111 Fall 2016 Lecture 9 19 6.111 Fall 2016 Lecture 9 20

17

## History of Computational Fabrics

- Discrete devices: relays, transistors (1940s-50s)

- Discrete logic gates (1950s-60s)

- Integrated circuits (1960s-70s)

- □ e.g. TTL packages: Data Book for 100's of different parts

- Gate Arrays (IBM 1970s)

- ☐ Transistors are pre-placed on the chip & Place and Route software puts the chip together automatically – only program the interconnect (mask programming)

- Software Based Schemes (1970's- present)

- Run instructions on a general purpose core

- Programmable Logic (1980's to present)

- ☐ A chip that be reprogrammed after it has been fabricated

- □ Examples: PALs, EPROM, EEPROM, PLDs, FPGAs

- □ Excellent support for mapping from Verilog

- ASIC Design (1980's to present)

- □ Turn Verilog directly into layout using a library of standard cells

- ☐ Effective for high-volume and efficient use of silicon area

6.111 Fall 2016 21 Lecture 9

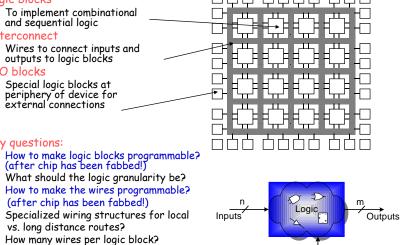

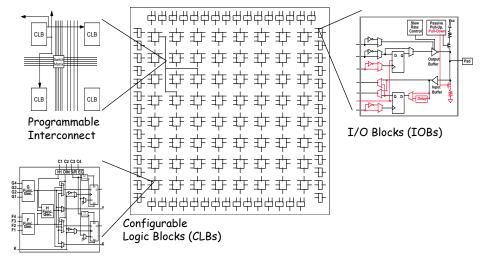

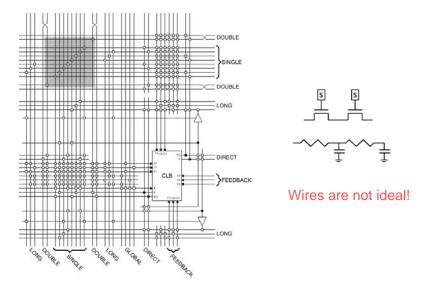

- What should the logic granularity be? - How to make the wires programmable? (after chip has been fabbed!)

(after chip has been fabbed!)

- Specialized wiring structures for local vs. long distance routes?

- How many wires per logic block?

Logic blocks

Interconnect

I/O blocks

Key questions:

To implement combinational and sequential logic

Wires to connect inputs and outputs to logic blocks

- Special logic blocks at

periphery of device for

external connections

Configuration

24

6.111 Fall 2016 22 Lecture 9

Reconfigurable Logic

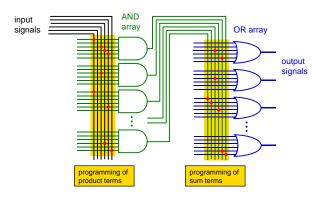

## Programmable Array Logic (PAL)

- Based on the fact that any combinational logic can be realized as a sum-of-products

- PALs feature an array of AND-OR gates with programmable interconnect

## RAM Based Field Programmable Logic - Xilinx

6,111 Fall 2016 23 6.111 Fall 2016 Lecture 9 Lecture 9

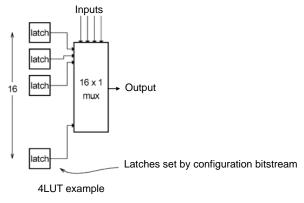

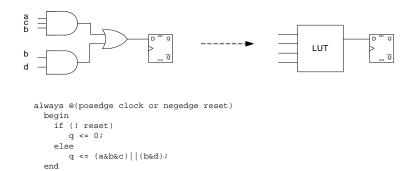

## LUT Mapping

- N-LUT direct implementation of a truth table: any function of n-inputs.

- N-LUT requires 2<sup>N</sup> storage elements (latches)

- N-inputs select one latch location (like a memory)

6.111 Fall 2016 Lecture 9 25

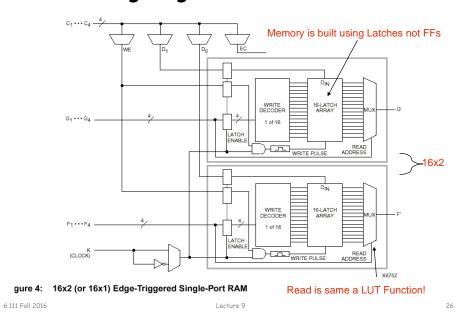

## Configuring the CLB as a RAM

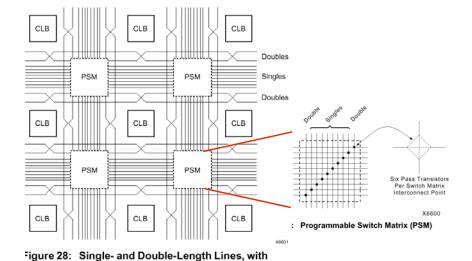

### Xilinx 4000 Interconnect

Programmable Switch Matrices (PSMs)

### Xilinx 4000 Interconnect Details

28

6.111 Fall 2016 Lecture 9 27 6.111 Fall 2016 Lecture 9

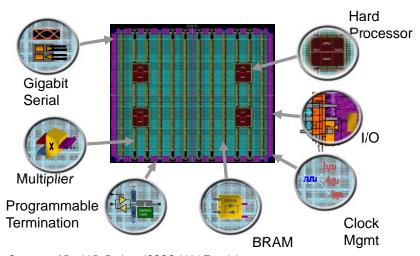

### Add Bells & Whistles

Courtesy of David B. Parlour, ISSCC 2004 Tutorial, "The Reality and Promise of Reconfigurable Computing in Digital Signal Processing"

6.111 Fall 2016 Lecture 9 29

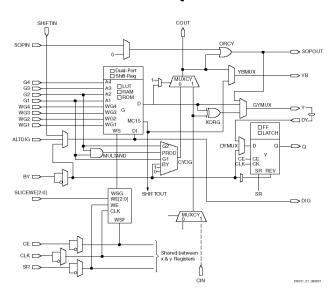

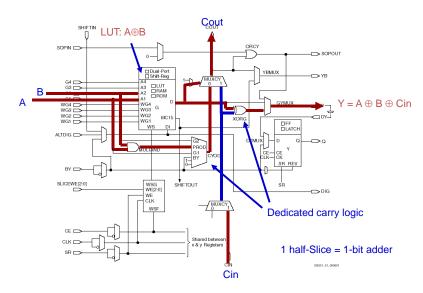

## The Virtex II CLB (Half Slice Shown)

6.111 Fall 2016 Lecture 9 30

## Adder Implementation

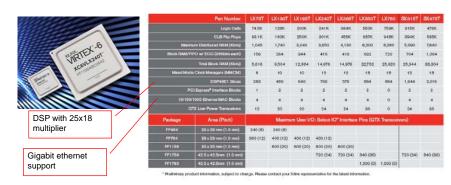

### FPGA's

|              | CLB     | Dist RAM   | Block RAM   | Multipliers   |

|--------------|---------|------------|-------------|---------------|

| Virtex 2     | 8,448   | 1,056 kbit | 2,592 kbit  | 144 (18x18)   |

| Virtex 6     | 667,000 | 6,200 kbit | 22,752 kbit | 1,344 (25x18) |

| Spartan 3E   | 240     | 15 kbit    | 72 kbit     | 4 (18x18)     |

| Artix-7 A100 | 7,925   | 1,188 kbit | 4,860 kbit  | 240 (25x18)   |

6.111 Fall 2016 Lecture 9 31 6.111 Fall 2016 Lecture 9 32

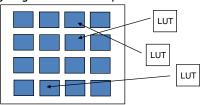

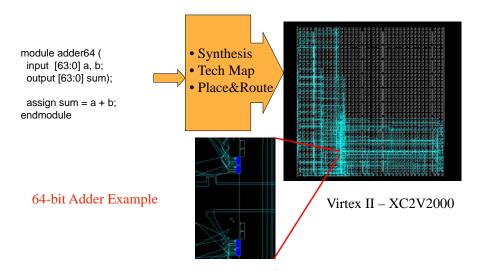

## Design Flow - Mapping

- Technology Mapping: Schematic/HDL to Physical Logic units

- Compile functions into basic LUT-based groups (function of target architecture)

6.111 Fall 2016 Lecture 9 33

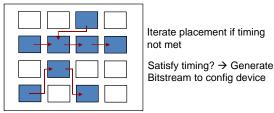

## Design Flow - Placement & Route

• Placement - assign logic location on a particular device

Routing – iterative process to connect CLB inputs/outputs and IOBs. Optimizes critical path delay – can take hours or days for large, dense designs

Challenge! Cannot use full chip for reasonable speeds (wires are not ideal).

Typically no more than 50% utilization.

Lecture 9

34

## Example: Verilog to FPGA

### How are FPGAs Used?

### Logic Emulation

FPGA-based Emulator (courtesy of IKOS)

#### Prototyping

- Ensemble of gate arrays used to emulate a circuit to be manufactured

- Get more/better/faster debugging done than with simulation

- Reconfigurable hardware

- One hardware block used to implement more than one function

- Special-purpose computation engines

- □ Hardware dedicated to solving one problem (or class of problems)

- Accelerators attached to general-purpose computers (e.g., in a cell phone!)

6.111 Fall 2016 Lecture 9 35 6.111 Fall 2016 Lecture 9 36

### Summary

- FPGA provide a flexible platform for implementing digital computing

- A rich set of macros and I/Os supported (multipliers, block RAMS, ROMS, high-speed I/O)

- A wide range of applications from prototyping (to validate a design before ASIC mapping) to high-performance spatial computing

- Interconnects are a major bottleneck (physical design and locality are important considerations)

#### Test Bench

```

module sample_tf;

module sample(

// Inputs

input bit_in,

reg bit_in;

input [3:0] bus_in,

reg [3:0] bus_in;

// Outputs

output out_bit,

wire out_bit;

output [7:0] out_bus

wire [7:0] out_bus;

. . . Verilog . . .

// Instantiate the Unit Under Test (UUT)

endmodule

sample uut (

.bit_in(bit_in),

.bus_in(bus_in),

.out_bit(out_bit),

.out_bus(out_bus)

initial begin

// Initialize Inputs

bit_in = 0;

bus_in = 0;

// Wait 100 ns for global reset to finish

#100;

// Add stimulus here

end

endmodule

```

6.111 Fall 2016 Lecture 9 37

6.111 Fall 2016 Lecture 9