# Analog Building Blocks

- · Sampling theorem

- · Undersampling, antialiasing

- · FIR digital filters

- · Quantization noise, oversampling

- OpAmps, DACs, ADCs

Thu: Lab 4 Checkoff

6.111 Fall 2016 Lecture 10

# Digital Representations of Analog Waveforms

Continuous time Continuous values

Discrete time Discrete values

6.111 Fall 2016 Lecture 10

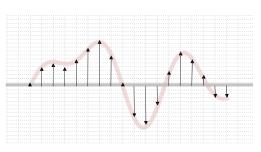

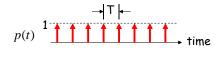

#### Discrete Time

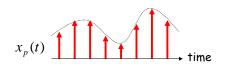

Let's use an impulse train to sample a continuous-time function at a regular interval T:

Lecture 10

$\delta(x)$  is a narrow impulse at x=0, where  $\int_{-a}^{a} f(t)\delta(t-a)dt = f(a)$

#### Reconstruction

Is it possible to reconstruct the original waveform using only the discrete time samples?

$X(j\omega)$

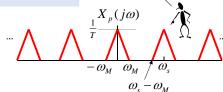

Looks like modulation by

$w_s$  and its harmonics

Frequency Domain

$P(j\omega)$  $-2\omega_{\rm s}$  $-\omega_{\rm c}$  $2\omega_{\rm s}$

So, if  $\omega_m < \omega_s - \omega_m$ , we can recover the original waveform with a lowpass filter!

6.111 Fall 2016

6.111 Fall 2016

Lecture 10

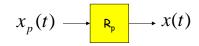

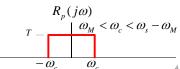

#### Sampling Theorem

Let x(t) be a band-limited signal, ie,  $X(j\omega)=0$  for  $|\omega| > \omega_M$ . Then x(t) is uniquely determined by its samples x(nT),  $n=0,\pm 1,\pm 2,\ldots,$  if

$\omega_s > 2\omega_M$

$2w_M$  is called the "Nyquist rate" and  $w_s/2$  the "Nyquist frequency"

where

$$\omega_s = \frac{2\pi}{T}$$

Given these samples, we can reconstruct x(t) by generating a periodic impulse train in which successive impulses have amplitudes that are successive sample values, then passing the train through an ideal LPF with gain T and a cutoff frequency greater than  $\omega_{\text{M}}$  and less than  $\omega_{\text{s}}\text{-}\omega_{\text{M}}.$

6.111 Fall 2016 Lecture 10 5

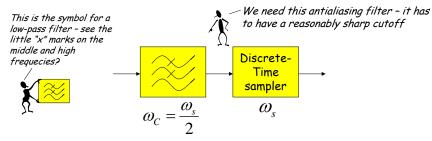

#### Antialias Filters

If we wish to create samples at some fixed frequency  $w_s$ , then to avoid aliasing we need to use a low-pass filter on the original waveform to remove any frequency content  $\geq w_s/2$ .

The frequency response of human ears essentially drops to zero above 20kHz. So the "Red Book" standard for CD Audio chose a 44.1kHz sampling rate, yielding a Nyquist frequency of 22.05kHz. The 2kHz of elbow room is needed because practical antialiasing filters have finite slope...

fs = (3 samples/line)(490 lines/frame)(30 frames/s) = 44.1 kHz

More info: http://www.cs.columbia.edu/~hgs/audio/44.1.html

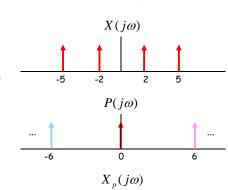

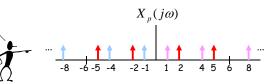

#### Undersampling $\rightarrow$ Aliasing

If  $w_s \le 2w_M$  there's an overlap of frequencies between one image and its neighbors and we discover that those overlaps introduce additional frequency content in the sampled signal, a phenomenon called aliasing.

$\omega_{\rm M}=5, \omega_{\rm s}=6$

There are now tones at 1 (= 6 - 5) and 4 (= 6 - 2) in addition to the original tones at 2 and 5.

6.111 Fall 2016 Lecture 10 6

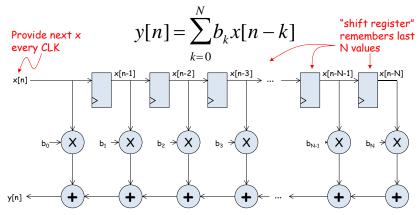

## Digital Filters

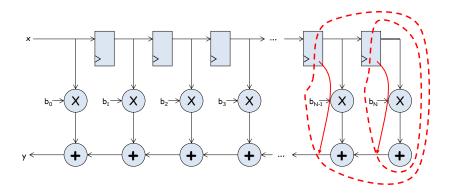

Equation for an N-tap finite impulse response (FIR) filter:

What components are part of the  $t_{PD}$  of this circuit? How does  $t_{PD}$  grow as N gets larger?

#### Filter coefficients

- Use Matlab command: b = fir1(N, $\omega_c$ /( $\omega_s$ /2))

- N is the number of taps (we'll get N+1 coefficients). Larger N gives sharper roll-off in filter response; usually want N to be as large as reasonably possible.

- $\omega_c$  is the cutoff frequency (3kHz in Lab 5)

- $\omega_s$  is the sample frequency (48kHz in Lab 5)

- The second argument to the fir1 command is the cutoff frequency as a fraction of the Nyquist frequency (i.e., half the sample rate).

- By default you get a lowpass filter, but can also ask for a highpass, bandpass, bandstop.

- The b coefficients are real numbers between 0 and 1. But since we don't want to do floating point arithmetic, we usually scale them by some power of two and then round to integers.

- Since coefficients are scaled by 2<sup>s</sup>, we'll have to re-scale the answer by dividing by 25. But this is easy - just get rid of the bottom S bits!

Retiming the FIR circuit

Apply the cut-set retiming transformation repeatedly...

6.111 Fall 2016 Lecture 10 6.111 Fall 2016 Lecture 10

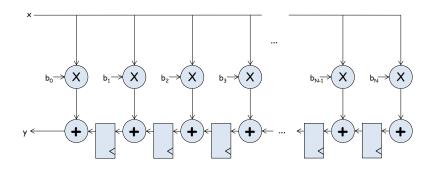

## Retimed FIR filter circuit

"Transposed Form" of a FIR filter

What components are part of the tpD of this circuit? How does top grow as N gets larger?

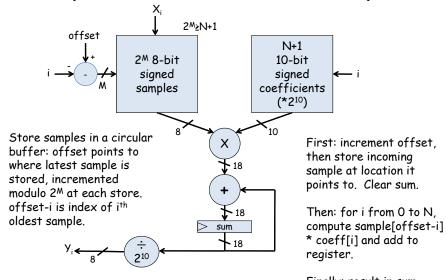

## N-tap FIR: less hardware, N+1 cycles...

Finally: result in sum

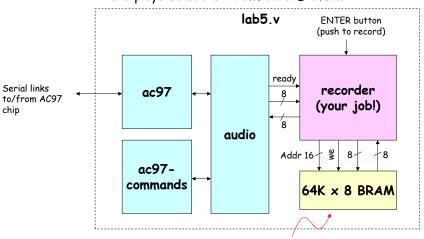

#### Lab 5A overview

Assignment: build a voice recorder that records and plays back 8-bit PCM data @ 6KHz

About 11 seconds of speech @ 6KHz

6.111 Fall 2016 Lecture 10

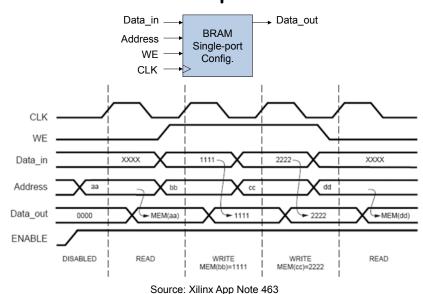

#### **BRAM** Operation

6.111 Fall 2016 Lecture 10

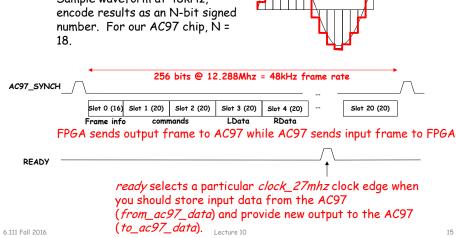

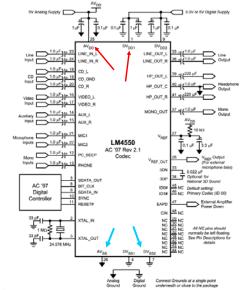

#### AC97: PCM data

PCM = pulse code modulation

Sample waveform at 48kHz, encode results as an N-bit signed number. For our AC97 chip, N =18.

13

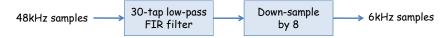

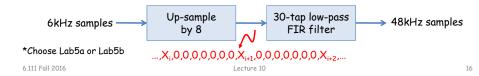

#### Lab 5a\* w/ FIR filter

• Since we're down-sampling by a factor of 8, to avoid aliasing (makes the recording sound "scratchy") we need to pass the incoming samples through a low-pass antialiasing filter to remove audio signal above 3kHz (Nyquist frequency of a 6kHz sample rate).

· We need a low-pass reconstruction filter (the same filter as for antialiasing!) when playing back the 6kHz samples. Actually we'll run it at 48kHz and achieve a 6kHz playback rate by feeding it a sample, 7 zeros, the next sample, 7 more zeros, etc.

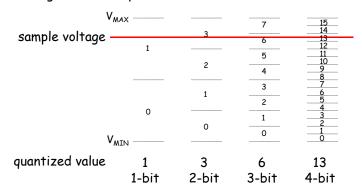

#### Discrete Values

If we use N bits to encode the magnitude of one of the discrete-time samples, we can capture  $2^N$  possible values.

So we'll divide up the range of possible sample values into  $2^N$  intervals and choose the index of the enclosing interval as the encoding for the sample value.

6.111 Fall 2016 Lecture 10 17

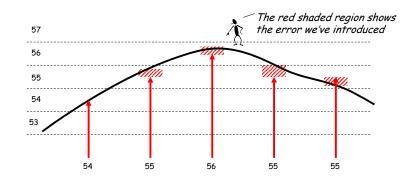

#### **Quantization Error**

Note that when we quantize the scaled sample values we may be off by up to  $\pm \frac{1}{2}$  step from the true sampled values.

6.111 Fall 2016 Lecture 10 18

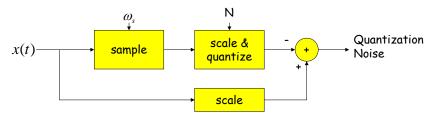

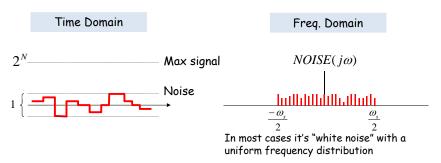

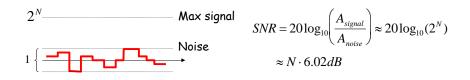

## Quantization Noise

## SNR: Signal-to-Noise Ratio

$$SNR = 10\log_{10}\left(\frac{P_{SIGNAL}}{P_{NOISE}}\right) = 10\log_{10}\left(\frac{A_{SIGNAL}^2}{A_{NOISE}^2}\right) = 20\log_{10}\left(\frac{A_{SIGNAL}}{A_{NOISE}}\right)$$

RMS amplitude

SNR is measured in decibels (dB). Note that it's a logarithmic scale: if SNR increases by 3dB the ratio has increased by a factor 2. When applied to audible sounds: the ratio of normal speech levels to the faintest audible sound is 60-70 dB.

6.111 Fall 2016 Lecture 10 19 6.111 Fall 2016 Lecture 10 20

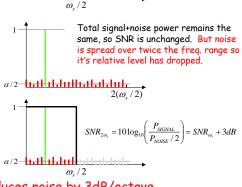

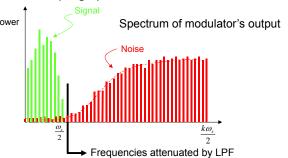

#### Oversampling

To avoid aliasing we know that  $w_c$  must be at least  $2w_M$ . Is there any advantage to oversampling, i.e.,  $w_s = K \cdot 2w_M$ ?

Suppose we look at the frequency spectrum of quantized samples of a sine wave: (sample freq. =  $w_s$ )

Let's double the sample frequency to  $2w_s$ .

Now let's use a low pass filter to eliminate half the noise! Note that we're not affecting the signal at all...

Oversampling+LPF reduces noise by 3dB/octave

6.111 Fall 2016

#### Lab 5b Overview

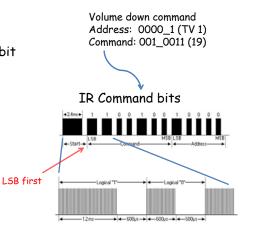

Assignment: build a digital system to "learn" four Sony Infrared Command (SIRC) and use it to control a Sony television.

· Data sent via 950nm IR modulated at 40khz.

Data width: 12, 15 or 20 bit protocol (use 12 bit).

· Start bit: 2400us High: 1200us Low: 600us

· Transmit FSM provided

· Learn/store remote commands

6.111 Fall 2016 Lecture 10

## Lab 5b Block Diagram

- IR receiver demodulates signal and provides input into labkit - powered by 5V from labkit.

- · 2N2222 BJT used to power IR transmitter (note bypass caps) - power from labkit

- · Command code and channel displayed on hex display

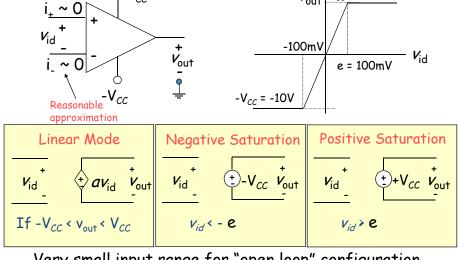

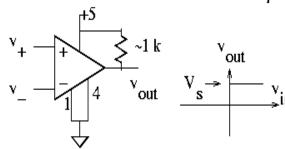

## Our Analog Building Block: OpAmp

Very small input range for "open loop" configuration

6.111 Fall 2016 Lecture 10 23 6.111 Fall 2016

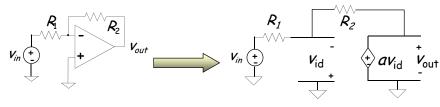

# The Power of (Negative) Feedback

$$\frac{v_{in} + v_{id}}{R_1} + \frac{v_{out} + v_{id}}{R_2} = 0 \qquad v_{id} = \frac{v_{out}}{a} \qquad \frac{v_{in}}{R_1} = -\frac{v_{out}}{a} \left[ \frac{1}{R_1} + \frac{a}{R_2} + \frac{1}{R_2} \right]$$

$$\frac{v_{out}}{v_{in}} = -\frac{R_2 a}{(1+a)R_1 + R_2} \approx -\frac{R_2}{R_1} (if \quad a >> 1)$$

- Overall (closed loop) gain does not depend on open loop gain

- Trade gain for robustness

- Easier analysis approach: "virtual short circuit approach" v<sub>1</sub> = v = 0 if OpAmp is linear

6.111 Fall 2016 Lecture 10 25

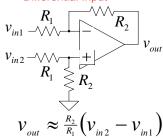

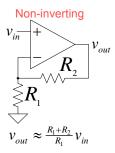

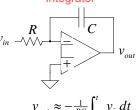

#### Basic OpAmp Circuits

#### Voltage Follower (buffer)

$$v_{out} \approx v_{in}$$

#### **Differential Input**

28

## OpAmp as a Comparator

#### Analog Comparator:

LM311 uses a

single supply

voltage

Is V+ > V-? The Output is a DIGITAL signal

Analog Comparator: Analog to TTL

LM 311 Needs Pull-Up

# Digital to Analog

- Common metrics:

- Conversion rate DC to ~500 MHz (video)

- # bits up to ~24

- Voltage reference source (internal / external; stability)

- Output drive (unipolar / bipolar / current) & settling time

- Interface parallel / serial

- Power dissipation

- Common applications:

- Real world control (motors, lights)

- Video signal generation

- Audio / RF "direct digital synthesis"

- Telecommunications (light modulation)

- Scientific & Medical (ultrasound, ...)

6.111 Fall 2016 Lecture 10 27 6,111 Fall 2016 Lecture 10

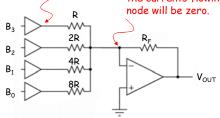

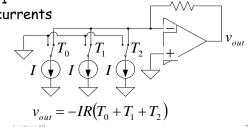

## DAC: digital to analog converter

How can we convert a N-bit binary number to a voltage?

OPAMP will vary V<sub>OUT</sub> to maintain this node at OV, i.e., the sum of the currents flowing into this

OKAY, this'll work, but the voltages produced by the drivers and various R's must be carefully matched in order to get equal steps.

$$\frac{V_{OUT}}{R_F} + \frac{B_3 V}{R} + \frac{B_2 V}{2R} + \frac{B_1 V}{4R} + \frac{B_0 V}{8R} = 0$$

$$V_{OUT} = -\frac{R_F}{R}V\left(B_3 + \frac{B_2}{2} + \frac{B_1}{4} + \frac{B_0}{8}\right)$$

6.111 Fall 2016

29

#### R-2R Ladder DAC Architecture

R-2R Ladder achieves large current division ratios with only two resistor values

6.111 Fall 2016 30 Lecture 10

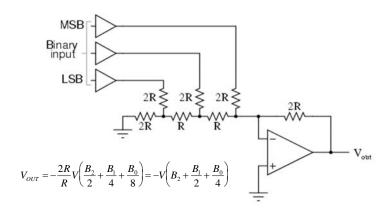

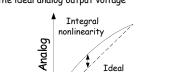

#### Non-idealities in Data Conversion

the output when the digital input is 0

Offset - a constant voltage offset that appears at Gain error - deviation of slope from ideal value of 1

Integral Nonlinearity - maximum deviation from the ideal analog output voltage

Binary code

Differential nonlinearity - the largest increment in analog output for a 1-bit change

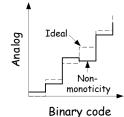

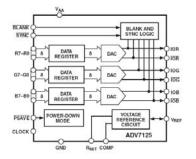

#### Labkit: ADV7125 Triple Out Video DAC

- Three 8-bit DACs

- Single Supply Op.: 3.3 to 5V

- · Internal bandgap voltage ref

- Output: 2-26 mA

- · 330 MSPS (million samples per second)

- Simple edge-triggered registerbased interface

6,111 Fall 2016 31 6,111 Fall 2016 32 Lecture 10 Lecture 10

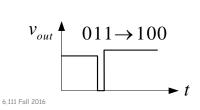

## Glitching and Thermometer D/A

- Glitching is caused when switching times in a D/A are not synchronized

- Example: Output changes from 011 to 100 - MSB switch is delayed

| Binary |   | Thermometer |   |   |

|--------|---|-------------|---|---|

| 0      | 0 | 0           | 0 | 0 |

| 0      | 1 | 0           | 0 | 1 |

| 1      | 0 | 0           | 1 | 1 |

| 1      | 1 | 1           | 1 | 1 |

R

- Filtering reduces glitch but increases the D/A settling time

- One solution is a thermometer code D/A - requires 2<sup>N</sup> - 1 switches but no ratioed currents

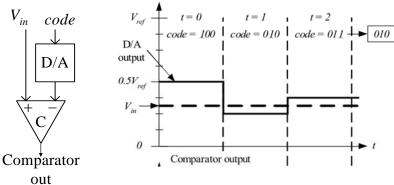

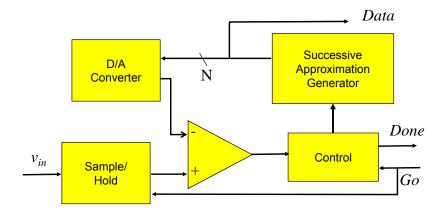

Successive-Approximation A/D

- D/A converters are typically compact and easier to design. Why not A/D convert using a D/A converter and a comparator?

- DAC generates analog voltage which is compared to the input voltage

- If DAC voltage > input voltage then set that bit; otherwise, reset that bit

- This type of ADC takes a fixed amount of time proportional to the bit length

Example: 3-bit A/D conversion, 2 LSB < Vin < 3 LSB

6.111 Fall 2016 Lecture 10 34

## Successive-Approximation A/D

Serial conversion takes a time equal to  $N(t_{D/A} + t_{comp})$

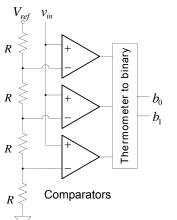

## Flash A/D Converter

- Brute-force A/D conversion

- Simultaneously compare the analog value with every possible reference value

- Fastest method of A/D conversion

- Size scales exponentially with precision (requires 2<sup>N</sup> comparators)

6.111 Fall 2016 Lecture 10 35 6.111 Fall 2016 Lecture 10

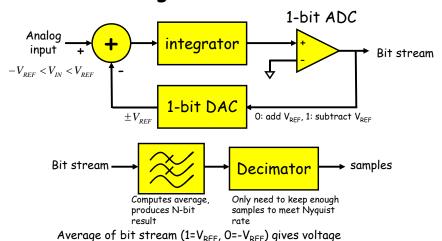

#### Sigma Delta ADC

With  $V_{REF}$ =1V:  $V_{IN}$ =0.5: 1110...,  $V_{IN}$ =-0.25: 00100101...,  $V_{IN}$ =0.6: 11110

http://designtools.analog.com/dt/sdtutorial/sdtutorial.html#instructions

6.111 Fall 2016 Lecture 10 37

# So, what's the big deal?

- Can be run at high sampling rates, oversampling by, say, 8 or 9 octaves for audio applications; low power implementations

- Feedback path through the integrator changes how the noise is spread across the sampling spectrum.

• Pushing noise power to higher frequencies means more noise is eliminated by LPF:  $N^{th}$  order  $\Sigma\Delta$  SNR = (3+N\*6)dB/octave

6.111 Fall 2016 Lecture 10 38

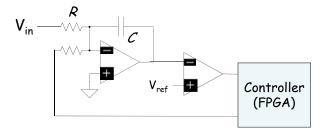

## Sigma Delta ADC

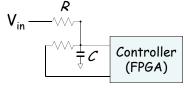

A simple ADC:

· Poor Man's ADC:

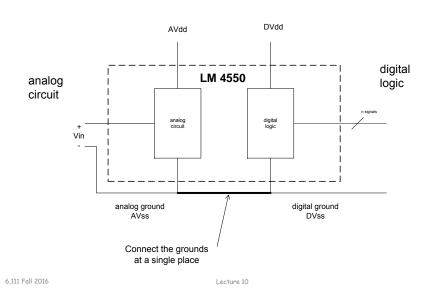

#### AD Supply Voltages Consideration

Noise caused by current spikes in fast switching digital circuits:

$$i_c = c \frac{dv}{dt}$$

- AV<sub>DD</sub> Positive Analog Supply Voltage

- · AV<sub>ss</sub> Analog Ground

- DV<sub>DD</sub> Positive Digital Supply Voltage

- DV<sub>ss</sub> Digital Ground

440

6.111 Fall 2016 Lecture 10 39 6.111 Fall 2016 Lecture 10

#### Digital/Analog Grounds

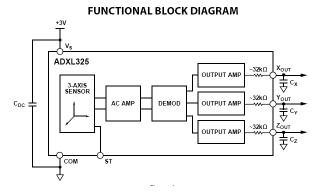

#### Sensors

native analog outputs: thermocouples, accelerometers, pressure gauge, ..

Many sensors have

3-axis

accelerometer

now used in cell

phones, games,

iPods, laptops,

6.111 projects

3 Axis 5G accelerometer

6.111 Fall 2016 Lecture 10

441

43

6,111 Fall 2016

#### Labkit Hardware

- Xilinx FPGA

- · Logic analyzer pods

- 4 banks/pods of 16 data lines

- (analyzerN\_clock) and a 16-bit data bus (analyzerN\_data[15:0]) N=1,2,3,4

- VGA video output

- · RS-232 Serial IO

- PS/2 keyboard and mouse input

- AC97 audio input/output

- Intel standard for PC audio systems

- codec's ADCs and DACs operate at a 48kHz sample rate, with 18 bits of precision

- 128Mbits Flash memory, (2) 512k x 36 ZBT SRAM

#### Labkit Hardware

- · Bidirectional user

- general purpose I/O, such as connecting to devices on the breadboards

- bidirectional (inout) signals user1[31:0] through user4[31:0]

- TV Video

- -- S video input/output

- \_ Audio input/output

- Composite video input/output

6.111 Fall 2016 Lecture 10

Lecture 10

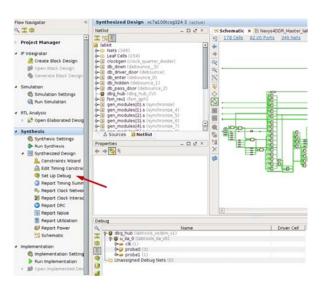

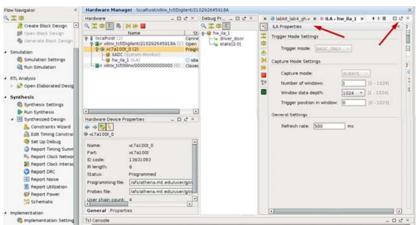

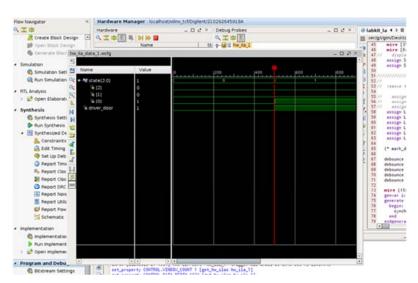

## Integrated Logic Analyzer ILA

- Allows user to view actual signals in design with a virtual logic analyzer.

- Useful for debugging designs that seem to work in simulation but not implementation.

- B sure change the divider clock from 25\_000\_000 to 3 or 4 clock cyles.

(count == (SW[14] ? 3 : 24\_999\_999)) count <= 0;</li>

- To view the signals, additional signals are place and routed but used internally to display the waveforms.

```

(* mark_debug = "true" *) wire [2:0] state; // virtual test probes

(* mark_debug = "true" *) wire driver_door; // virtual test

// more Verilog, etc...

```

6.111 Fall 2016 Lecture 10 45 6.111 Fall 2016 Lecture 10 45

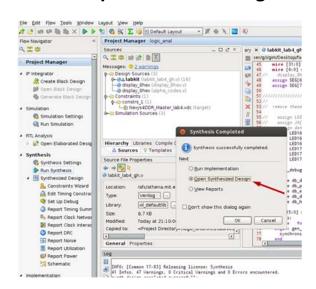

## Setup Debug

## Run Synthesized Design

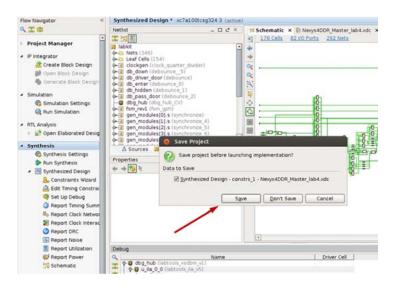

#### Save Constraints

48

6.111 Fall 2016 Lecture 10 47 6.111 Fall 2016 Lecture 10

## **Implementation**

Load the bit file to the FPGA. Undock ILA window. Set up the trigger for the ILA.

Set Trigger

Select and drag trigger (1,2)

Set trigger value (3)

Select trigger position (4)

Run (5)

- D t × Debug Pr... - D t Q 工 申 St 中 日 t (2) ILA - hw da 1 Run Simulatio \* ILA Properties @ Synthesis Set & Pun Synthesir ■ Synthesized C & Constraint Name | Compare Value | 1024 + [1-1024] A Edit Timin Set Up De @ Report Tim Report Clo O Report DR Report No Report Uti (C) Report Po 5 Schematic

6 111 Fall 2016 6.111 Fall 2016 Lecture 10 Lecture 10

# Waveform Display

## Upload Lab 4 Verilog

- · Submit by Monday

- Grading

- Proper use of blocking and non-blocking assignments

- Readable Code (reformatted) with comments and consistent indenting [use emacs or VIM]

- Use of default in case statement

- Use of parameter statements for symbolic name and constants (state==5 vs state==DATA\_READY)

- Parameterized modules when appropriate

- Readable logical flow, properly formatted (see "Verilog Editors")

- No long nested if statements.

- Score 1 to 3 (3 perfect); 1/2 point off for each occurrence.

6,111 Fall 2016 51 6,111 Fall 2016 Lecture 10 Lecture 10