## Logic Synthesis

- Primitive logic gates, universal gates

- Truth tables and sum-of-products

- · Logic simplification

- · Karnaugh Maps, Quine-McCluskey

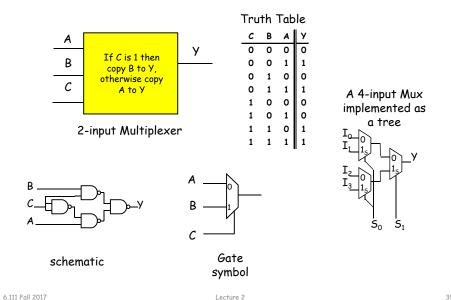

- General implementation techniques: muxes and look-up tables (LUTs)

Reminder: Lab #1 due this Thursday!

6.111 Fall 2017

Lecture 2

1

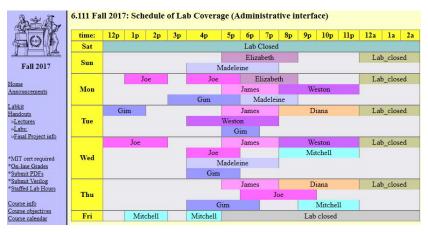

#### Lab Hours

Lab hours: eds.mit.edu/labs Sun 1-11:45p, M-R 9-11:45p, F 9-5p

6.111 Fall 2017 Lecture 2 2

#### Late Policies

- Lab 1 check-offs sign-up on checkoff queue in lab FIFO during staffed lab hours. Note bench number...

- Please don't assume that you can wait until the last minute!

- No check-offs Saturday

- · Checkoff must start no later than 9PM

- Lab grade = Checkoff + Verilog grade (equal weighting)

- · Late labs:

- 20%/day late penalty (no penalty for Saturday)

- · Max penalty 80% reduction.

- Penalty waived for first 5 slack days. This covers illness, interviews, overload, etc. without S^3 involvement.

- A missing lab will result in a failing grade. We've learned that if you're struggling with the labs, the final project won't go very well.

- Lpset must be submitted on time.

### **Conflicts**

6.111

presentation

Presentation

6.034

29%

| week |        |     | MIT calendar                                 | 6.111 | 6.034     | week |        |     | MIT calendar                                 |  |

|------|--------|-----|----------------------------------------------|-------|-----------|------|--------|-----|----------------------------------------------|--|

|      |        |     | students who are als<br>of 6.111 who are als |       | 100 100 E |      |        |     | students who are als<br>of 6.111 who are als |  |

|      | Oct 15 | Sun |                                              |       |           |      | Nov 05 | Sun |                                              |  |

| 7    | Oct 16 | Mon |                                              |       |           | 10   | Nov 06 |     |                                              |  |

|      | Oct 17 | Tue |                                              |       |           |      | Nov 07 | Tue |                                              |  |

|      | Oct 18 | Wed |                                              |       | Quiz 2    |      | Nov 08 | Wed |                                              |  |

|      | Oct 19 | Thu |                                              | Lab 5 |           |      |        |     |                                              |  |

|      |        |     |                                              |       |           |      | Nov 09 | Thu |                                              |  |

|      | Oct 20 | Fri |                                              |       |           |      | Nov 10 | Fri | No classes                                   |  |

|      | Oct 21 | Sat | Birth of                                     |       |           |      |        |     | (Veterans Day)                               |  |

|      |        |     | Baha'u'llah                                  |       |           |      | Nov 11 | Sat |                                              |  |

|      | Oct 22 | Sun |                                              |       |           |      | Nov 12 | Sun |                                              |  |

### Schematics & Wiring

- IC power supply connections generally not drawn. All integrated circuits need power!

- Use standard color coded wires to avoid confusion.

- -red: positive

- -black: ground or common reference point

- -Other colors: signals

- · Circuit flow, signal flow left to right

- Higher voltage on top, ground negative voltage on bottom

- Neat wiring helps in debugging!

6.111 Fall 2017 5

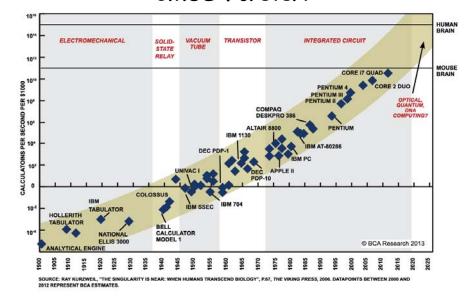

#### CMOS Forever? Mastering Moore's Law Core i5° 10 billion Intel's progress in packing more 1.3 billion Intel Core 2 Duo transistors on mainstream 1 billion 410 million microprocessor chips 100 million Pentium 4 Core i5 Logarithmic scale 125 million 1.0 billion 10 million Pentium 1 million 3.1 million 100,000 10,000 1,000 4004 100 2.300 transistors 10 2000 10 \*Upgraded versions of prior models THE WALL STREET JOURNAL. Source: Intel 6,111 Fall 2017 Lecture 2

### Wire Gauge

- Wire gauge: diameter is inversely proportional to the wire gauge number.

Diameter increases as the wire gauge decreases. 2, 1, 0, 00, 000(3/0) up to 7/0.

- Resistance

6.111 Fall 2017

- -22 gauge .0254 in 16 ohm/1000 feet

- -12 gauge .08 in 1.5 ohm/1000 feet

- -High voltage AC used to reduce loss

- 1 cm cube of copper has a resistance of 1.68 micro ohm (resistance of copper wire scales linearly: length/area)

#### CMOS Forever?

6.111 Fall 2017 Lecture 2

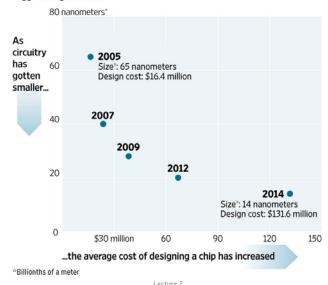

#### Diminishing Returns \*

\* Intel

6.111 Fall 2017

Creating smaller circuitry has placed more transistors on chips but triggered higher costs.

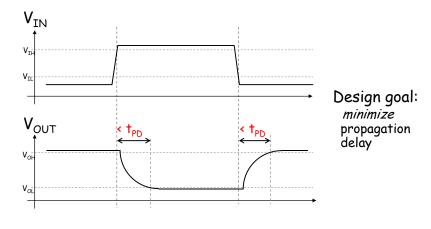

Timing Specifications

Propagation delay ( $t_{PD}$ ): An <u>upper bound</u> on the delay from valid inputs to valid outputs (aka " $t_{PD,MAX}$ ")

6.111 Fall 2017 Lecture 2

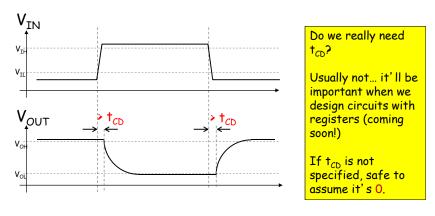

## Contamination Delay

an optional, additional timing spec

Contamination delay( $t_{CD}$ ): A <u>lower bound</u> on the delay from invalid inputs to invalid outputs (aka " $t_{PD,MIN}$ ")

### The Combinational Contract

A DO- B  $\frac{A}{0}$   $\frac{B}{1}$   $\frac{A}{1}$   $\frac{B}{1}$   $\frac{A}{1}$   $\frac{B}{1}$   $\frac{A}{1}$   $\frac{B}{1}$   $\frac{A}{1}$   $\frac{A}{1$

12

- 1. No Promises during XXXXX

- 2. Default (conservative) spec:  $t_{CD} = 0$

6.111 Fall 2017 Lecture 2 11 6.111 Fall 2017 Lecture 2

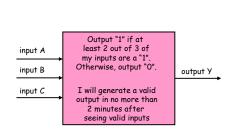

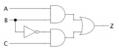

### **Functional Specifications**

| Α                 | В | С | У |  |  |  |  |

|-------------------|---|---|---|--|--|--|--|

| 0                 | 0 | 0 | 0 |  |  |  |  |

| 0                 | 0 | 1 | 0 |  |  |  |  |

| 0                 | 1 | 0 | 0 |  |  |  |  |

| 0                 | 1 | 1 | 1 |  |  |  |  |

| 1                 | 0 | 0 | 0 |  |  |  |  |

| 1                 | 0 | 1 | 1 |  |  |  |  |

| 1                 | 1 | 0 | 1 |  |  |  |  |

| 1                 | 1 | 1 | 1 |  |  |  |  |

| 2 6 in a m . in m |   |   |   |  |  |  |  |

3 binary inputs so  $2^3 = 8$  rows in our truth table

An concise, unambiguous technique for giving the functional specification of a combinational device is to use a *truth table* to specify the output value for each possible combination of input values (N binary inputs  $\rightarrow$  2<sup>N</sup> possible combinations of input values).

6.111 Fall 2017 Lecture 2 13

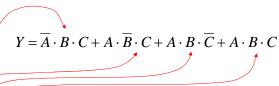

### Here's a Design Approach

- Write out our functional spec as a truth table

- 2. Write down a Boolean expression with terms covering each '1' in the output:

This approach creates equations of a particular form called

#### SUM-OF-PRODUCTS

0

1

1

$B \mid C \mid Y$

0 1 0

Α

0 0 0 0 0

0

0 1 0 0

0 1 1 1

1 0 0 0

1 0 1 1

1 1

1 1

Sum (+): ORs

Products (•): ANDs

6.111 Fall 2017 Lecture 2 14

### S-O-P Building Blocks

INVERTER:

$$A \longrightarrow Z = \overline{A}$$

Subble indicates inversion

AND:

$$A \longrightarrow Z = A \cdot B$$

OR:

$$A \longrightarrow Z = A + B$$

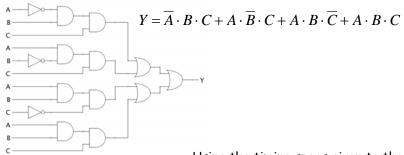

### Straightforward Synthesis

$Y = \overline{A} \cdot B \cdot C + A \cdot \overline{B} \cdot C + A \cdot B \cdot \overline{C} + A \cdot B \cdot C$

We can use

SUM-OF-PRODUCTS

to implement any logic function

Only need 3 gate types: INVERTER, AND, OR

Propagation delay:

- 3 levels of logic

- No more than 3 gate delays assuming gates with an arbitrary number of inputs. But, in general, we'll only be able to use gates with a bounded number of inputs (bound is ~4 for most logic families).

15

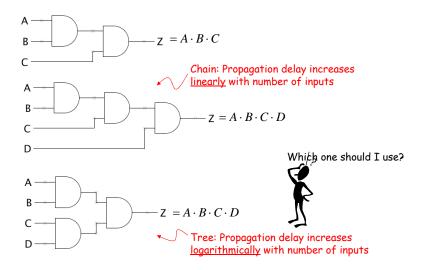

### ANDs and ORs with > 2 inputs

6.111 Fall 2017 Lecture 2 17

### SOP w/ 2-input gates

Previous example restricted to 2-input gates:

|                 | INV | AND2 | OR2  |

|-----------------|-----|------|------|

| † <sub>PD</sub> | 8ps | 15ps | 18ps |

| † <sub>C</sub>  | 1ps | 3ps  | 3ps  |

| D               |     |      |      |

Using the timing specs given to the left, what are  $t_{PD}$  and  $t_{CD}$  for this combinational circuit?

Hint: to find overall  $t_{PD}$  we need to find max  $t_{PD}$  considering all paths from inputs to outputs.

6.111 Fall 2017 Lecture 2 18

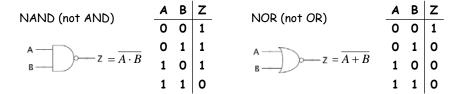

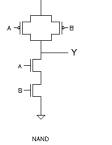

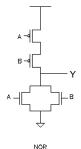

### More Building Blocks

CMOS gates are naturally inverting so we want to use NANDs and NORs in CMOS designs...

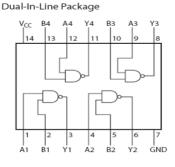

### NAND - NOR Internals

This device contains four independent gates each of which performs the logic NAND function.

6.111 Fall 2017 Lecture 2 19 6.111 Fall 2017 Lecture 2 20

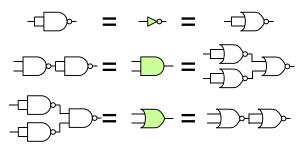

### Universal Building Blocks

NANDs and NORs are universal:

Any logic function can be implemented using only NANDs (or, equivalently, NORs). Note that chaining/treeing technique doesn't work directly for creating wide fan-in NAND or NOR gates. But wide fan-in gates can be created with trees involving both NANDs, NORs and inverters

6.111 Fall 2017 Lecture 2

### Logic Simplification

- · Can we implement the same function with fewer gates? Before trying we'll add a few more tricks in our bag.

- BOOLEAN ALGEBRA:

a+1=1 a+0=a a+a=aOR rules: AND rules:  $a \cdot 1 = a$   $a \cdot 0 = 0$   $a \cdot a = a$ Commutative: a+b=b+a  $a \cdot b=b \cdot a$

Associative: (a+b)+c=a+(b+c)  $(a\cdot b)\cdot c=a\cdot (b\cdot c)$ Distributive:  $a \cdot (b+c) = a \cdot b + a \cdot c$   $a+b \cdot c = (a+b) \cdot (a+c)$

Complements:  $a + \overline{a} = 1$   $a \cdot \overline{a} = 0$

Absorption:  $a+a \cdot b = a$   $a+\overline{a} \cdot b = a+b$   $a \cdot (a+b) = a$   $a \cdot (\overline{a}+b) = a \cdot b$

De Morgan's Law:  $\overline{a \cdot b} = \overline{a} + \overline{b}$   $\overline{a + b} = \overline{a} \cdot \overline{b}$ Reduction:

$a \cdot b + \overline{a} \cdot b = b$   $(a+b) \cdot (\overline{a} + b) = b$

Key to simplification: equations that match the pattern of the LHS (where "b" might be any expression) tell us that when "b" is true, the value of "a" doesn't matter. So "a" can be eliminated from the equation, getting rid of two 2-input ANDs and one 2-input OR.

#### SOP with NAND/NOR

When designing with NANDs and NORs one often makes use of De Morgan's laws: De Morgan-ized NAND symbol

NAND form:  $\overline{A \cdot B} = \overline{A} + \overline{B}$

So the following "SOP" circuits are all equivalent (note the use of De Morgan-ized symbols to make the inversions less confusing):

AND/OR form

NAND/NAND form This will be handy in Lab 1 since you'll be able to use just 7400's to implement your circuit!

NOR/NOR form

All these "extra" inverters may seem less than ideal but often the buffering they provide will reduce the capacitive load on the inputs and increase the output drive.

24

6.111 Fall 2017 Lecture 2

#### **Boolean Minimization:**

An Algebraic Approach

Lets simplify the equation from slide #3:

$$Y = \overline{A} \cdot B \cdot C + A \cdot \overline{B} \cdot C + A \cdot B \cdot \overline{C} + A \cdot B \cdot C$$

Using the identity

$$\alpha A + \alpha \overline{A} = \alpha$$

For any expression  $\alpha$  and variable A:

$$Y = \overline{A} \cdot B \cdot C + A \cdot \overline{B} \cdot C + A \cdot B \cdot \overline{C} + A \cdot B \cdot C$$

$$Y = B \cdot C + A \cdot C + A \cdot B$$

The tricky part: some terms participate in more than one reduction so can't do the algebraic steps one at a time!

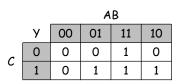

#### Karnaugh Maps: A Geometric Approach

K-Map: a truth table arranged so that terms which differ by exactly one variable are adjacent to one another so we can see potential reductions easily.

| Α | В | С | У |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

Here's the layout of a 3-variable K-map filled in with the values from our truth table:

010 011 000 001

Why did he shade that

row Gray?

It's cyclic. The left edge is adjacent to the right edge. It's really just a flattened out cube.

6.111 Fall 2017 Lecture 2

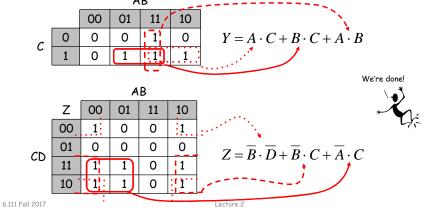

### On to Hyperspace

Here's a 4-variable K-map:

|    |    |    | Α  | В  |    |

|----|----|----|----|----|----|

|    | Z  | 00 | 01 | 11 | 10 |

|    | 00 | 1  | 0  | 0  | 1  |

| CD | 01 | 0  | 0  | 0  | 0  |

| CD | 11 | 1  | 1  | 0  | 1  |

|    | 10 | 1  | 1  | 0  | 1  |

Again it's cyclic. The left edge is adjacent to the right edge, and the top is adjacent to the bottom.

We run out of steam at 4 variables - K-maps are hard to draw and use in three dimensions (5 or 6 variables) and we're not equipped to use higher dimensions (> 6 variables)!

6.111 Fall 2017 Lecture 2 26

### Finding Subcubes

We can identify clusters of "irrelevent" variables by circling adjacent subcubes of 1s. A subcube is just a lower dimensional cube.

AB

Ζ 00 01 11 10 00 1 0 0 1 0 01 0 0 11 1 0 **1** 1 0

Three 2x1 subcubes

Three 2x2 subcubes

The best strategy is generally a greedy one.

- Circle the largest N-dimensional subcube ( $2^N$  adjacent 1's)  $4\times4$ ,  $4\times2$ ,  $4\times1$ ,  $2\times2$ ,  $2\times1$ ,  $1\times1$

- Continue circling the largest remaining subcubes (even if they overlap previous ones)

- Circle smaller and smaller subcubes until no 1s are left.

### Write Down Equations

Write down a product term for the portion of each cluster/subcube that is invariant. You only need to include enough terms so that all the 1's are covered. Result: a minimal sum of products expression for the truth table.

6.111 Fall 2017 Lecture 2 27

#### Morse Code to ASCII Exercise

- · Morse code variable length encoding, 6 bits max

- Letter "e" •

- Period - -

- ASCII (American Standard Code for Information Interchange)

- 8 bit binary representation of text

- How many bits are required to represent any morse code input?

6.111 Fall 2017 Lecture 2 29

### Two-Level Boolean Minimization

Two-level Boolean minimization is used to find a sum-of-products representation for a multiple-output Boolean function that is optimum according to a given cost function. The typical cost functions used are the number of product terms in a two-level realization, the number of literals, or a combination of both. The two steps in two-level Boolean minimization are:

- •Generation of the set of prime product-terms for a given function.

- •<u>Selection</u> of a minimum set of prime terms to implement the function.

We will briefly describe the Quine-McCluskey method which was the first algorithmic method proposed for two-level minimization and which follows the two steps outlined above. State-of-the-art logic minimization algorithms are all based on the Quine-McCluskey method and also follow the two steps above.

| A 010 \$\$\$\$\$\$\$00 0 1 0 0 0 0 0 0 1 1 0 0 0 0                                                                                        |        |

|-------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 1 0 1 0 0 0 0 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                       |        |

| 10 110 popo 0 1 1 1 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1                                                                                         |        |

| 10 10 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 0 1 1 0 0 0 0 1 1 0 0 0 0 1 1 2 0 0 0 0 |        |

| 16 110 p 0 p 0 0 1 1 0 0 0 0 1 1 2 1                                                                                                      |        |

| 16 110 p 0 p 0 0 1 1 0 0 0 0 1 1 2 1                                                                                                      |        |

| 16 110000011 0 2000 2 1 2 2                                                                                                               |        |

|                                                                                                                                           |        |

| H 001690000 0 100 1000                                                                                                                    | 125    |

| I 010444000 1 2001 001                                                                                                                    |        |

| 3 001 00 1 1 1 0 0 1 0 0 0                                                                                                                |        |

| K 110 0 0 1 101                                                                                                                           | 111110 |

| L 001000010 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                   | GD     |

| 0 2 1 0 0                                                                                                                                 | -      |

| 1 0 1 0 0 1 0 0 1 0 0                                                                                                                     | OK     |

| N 01 0 a 9 9 0 1 0 1 1 1 1 1                                                                                                              |        |

| 0 21 0 20 9 2 7 7 1 1 2 9 0 1 1 1 1 2 1 2 2                                                                                               |        |

| P 00 1 00 0 0 1 0 1 0 0 0 0 1 60 H L                                                                                                      | 7 B    |

| Q 001 \$41011 1 10 10 00 1 01 V P                                                                                                         | a X    |

| 111000000000000000000000000000000000000                                                                                                   | PX 4   |

| S 11 0 d d d 0 0 0 0 1 0 0 1 1 10   F   P                                                                                                 | pc     |

6.111 Fall 2017 Lecture 2

#### Prime Term Generation

Start by expressing your Boolean function using 0-terms (product terms with no don't care care entries). For compactness the table for example 4-input, 1-output function F(w,x,y,z) shown to the right includes only entries where the output of the function is 1 and we've labeled each entry with it's decimal equivalent.

| F | = | f( | (W | ',X,Y,Z |

|---|---|----|----|---------|

| W | X | Y  | Z  | label   |

| 0 | 0 | 0  | 0  | 0       |

| 0 | 1 | 0  | 1  | 5       |

| 0 | 1 | 1  | 1  | 7       |

| 1 | 0 | 0  | 0  | 8       |

| 1 | 0 | 0  | 1  | 9       |

| 1 | 0 | 1  | 0  | 10      |

| 1 | 0 | 1  | 1  | 11      |

| 1 | 1 | 1  | 0  | 14      |

| 1 | 1 | 1  | 1  | 15      |

Look for pairs of 0-terms that differ in only one bit position and merge them in a 1-term (i.e., a term that has exactly one '-' entry). Next 1-terms are examined in pairs to see if the can be merged into 2-terms, etc. Mark k-terms that get merged into (k+1) terms so we can discard them later.

```

0, 8 -000[A]

2-terms: 8, 9,10,11 10--[D]

1-terms:

5, 7 01-1 [B]

10,11,14,15 1-1-[E]

7,15 -111 [C]

8, 9 100-

3-terms: none!

8,10 10-0

9,11 10-1

Example due to

Label unmerged terms:

10.11 101-

Srini Devadas

10.14 1-10

these terms are prime!

11,15 1-11

14,15 111-

6.111 Fall 2017

Lecture 2

```

6.111 Fall 2017 Lecture 2 31

#### Prime Term Table

An "X" in the prime term table in row R and column K signifies that the 0term corresponding to row R is contained by the prime corresponding to column K.

Goal: select the minimum set of primes (columns) such that there is at least one "X" in every row. This is the classical minimum covering problem.

|      | Α | В | C | D | ь |                  |      |

|------|---|---|---|---|---|------------------|------|

| 0000 | Х |   |   |   |   | → A is essential | -000 |

| 0101 |   | Х |   |   |   | → B is essential | 01-1 |

| 0111 |   | Х | Х |   |   |                  |      |

| 1000 | Х |   |   | Х |   |                  |      |

| 1001 |   |   |   | Х |   | → D is essential | 10   |

| 1010 |   |   |   | Х | Х |                  |      |

| 1011 |   |   |   | Х | Х |                  |      |

| 1110 |   |   |   |   | Х | → E is essential | 1-1- |

| 1111 |   |   | Х |   | Х |                  |      |

V D C D E

Each row with a single X signifies an essential prime term since any prime implementation will have to include that prime term because the corresponding 0-term is not contained in any other prime.

In this example the essential primes "cover" all the 0-terms.

$$F = f(W,X,Y,Z) = \overline{X}\overline{Y}\overline{Z} + \overline{W}XZ + W\overline{X} + WY$$

6.111 Fall 2017 Lecture 2 33

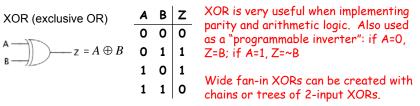

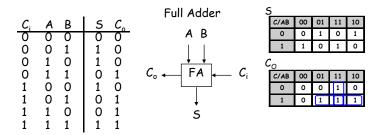

#### Logic that defies SOP simplification

$$S = \overline{A} \cdot B \cdot \overline{C} + A \cdot \overline{B} \cdot \overline{C} + \overline{A} \cdot \overline{B} \cdot C + A \cdot B \cdot C = A \oplus B \oplus C_i$$

$$C_O = A \cdot C + B \cdot C + A \cdot B$$

The sum 5 doesn't have a simple sum-of-products implementation even though it can be implemented using only two 2-input XOR gates.

6.111 Fall 2017 Lecture 2 34

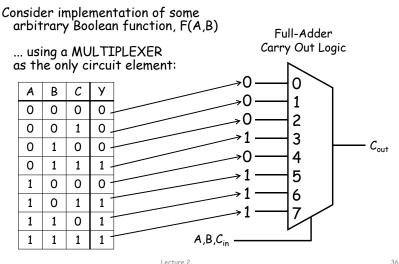

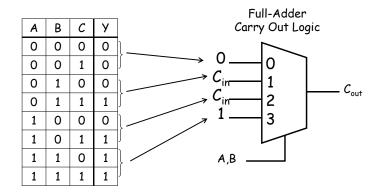

### Logic Synthesis Using MUXes

### Systematic Implementation of Combinational Logic

# Systematic Implementation of Combinational Logic

Same function as on previous slide, but this time let's use a 4-input mux

6.111 Fall 2017 Lecture 2 37

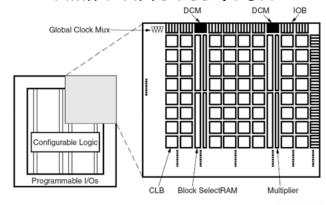

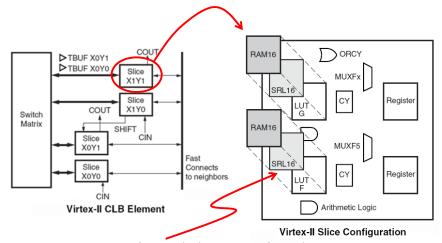

#### Xilinx Virtex II FPGA

Virtex-II Architecture Overview

#### XC2V6000:

- 957 pins, 684 IOBs

- CLB array: 88 cols x 96/col = 8448 CLBs

- 18Kbit BRAMs = 6 cols x 24/col = 144 BRAMs = 2.5Mbits

- $18 \times 18$  multipliers = 6 cols  $\times$  24/col = 144 multipliers

6.111 Fall 2017 Lecture 2 Figures from Xilinx Virtex II datasheet

#### Virtex II CLB

16 bits of RAM which can be configured as a 16x1 single- or dual-port RAM, a 16-bit shift register, or a 16-location lookup table

Figures from Xilinx Virtex II or a 16-bit shift register.

6,111 Fall 2017

Figures from Xilinx Virtex II datasheet

39

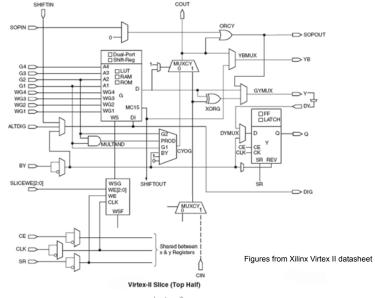

### Virtex II Slice Schematic

40

6,111 Fall 2017 Lecture 2

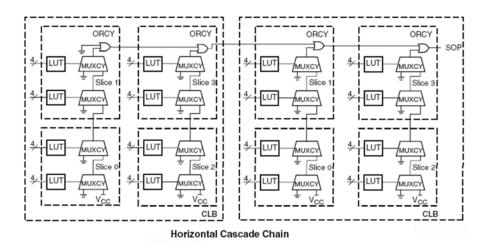

### Virtex II Sum-of-products

Figures from Xilinx Virtex II datasheet

6.111 Fall 2017 Lecture 2

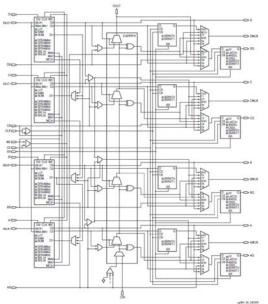

### Spartan 6 FPGA

Figure 31: XC6SLX45T Floorplan View in PlanAhead

6.111 Fall 2017 Lecture 2 4

### Spartan 6 SliceM Schematic

Figures from Xilinx Spartan 6 CLB datasheet

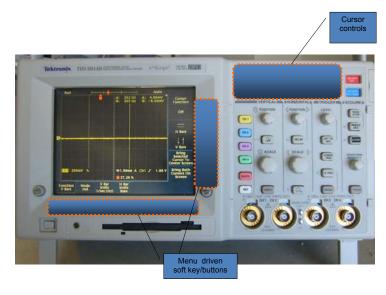

### Oscilloscope

6.111 Fall 2017 Lecture 2 43 6.111 Fall 2017 4

### Oscilloscope Controls

- Auto Set, soft menu keys

- Trigger

- channel,

- slope,

- Level

- Input

6.111 Fall 2017

- AC, DC coupling,

- 10x probe,

- 1khz calibration source,

- probe calibration,

- bandwidth filter

- Signal measurement

- time,

- frequency,

- voltage

- cursors

- single sweep

45

· Image capture

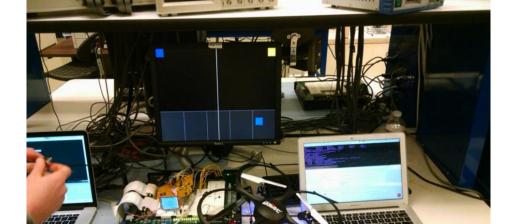

## Gesture Controlled Drone Fall 2014

- Track hands with a camera and determine x,y coordinates

- Based on movement of the coordinates, recognize gestures.

- Generate real time digital signals and convert to analog format for transmission to drone – controlling pitch, roll, hover

- Innovation: using hand motion and recognition of gestures to control flight