Variables in Verilog that are set inside an "always" block (qa,qb,qc,qd) block must be declared as "reg" so insert "reg" after "output" for qa,qb,qc,qd.

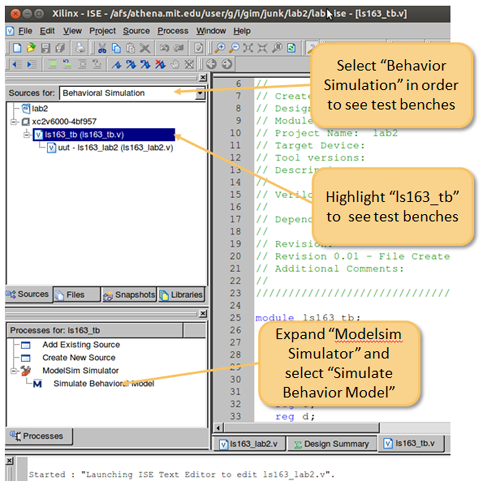

Click on the test bench "ls163_tb". To create a 10ns clock in your test bench, insert

always #5 clk = !clk; // change state every 5nsbefore the line "initial begin". To initialize the counter to the value five and begin counting, copy and paste the following lines your test bench "ls163_tb" after the line "// Add stimulus here"

////////////////////////////////////////////// // clr_bar = 1; ld_bar = 0; // note ld_bar is active low qa = 1; // now load 0b1001 to counter qb = 0; qc = 0; qd = 1; #20; // wait for 20ns ld_bar = 1; // /////////////////////////////////////////////

Save the changes.

Double click on "Simulate Behavior Model". Modelsim and a Waveform window will pop up. With the mouse in the waveform window right click "Zoom Full" to view the full simulation. Simulating with Modelsim contains examples of complex test benches.