# L10: Major/Minor FSMs, Lab 3, and RAM/ROM Instantiation

**Acknowledgements: Rex Min**

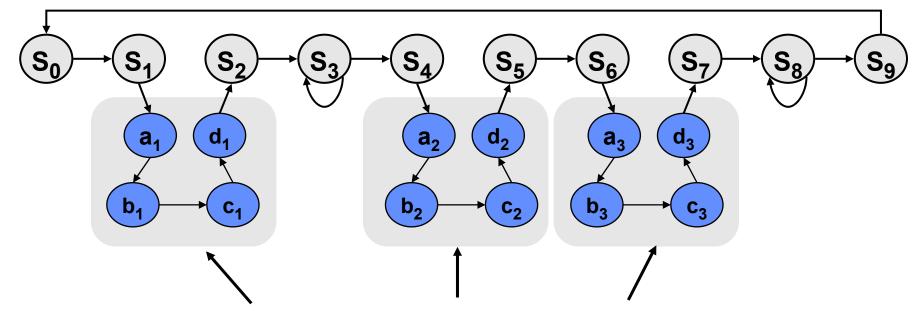

#### Consider the following abstract FSM:

- Suppose that each set of states a<sub>x</sub>...d<sub>x</sub> is a "sub-FSM" that produces exactly the same outputs.

- Can we simplify the FSM by removing equivalent states? No! The outputs may be the same, but the next-state transitions are not.

- This situation closely resembles a procedure call or function call in software...how can we apply this concept to FSMs?

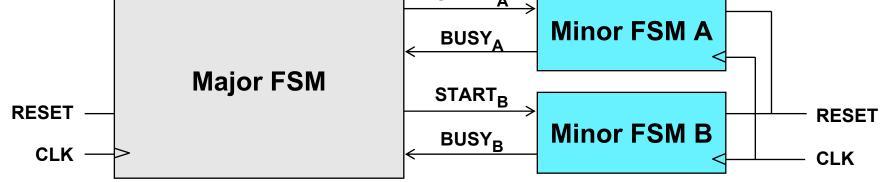

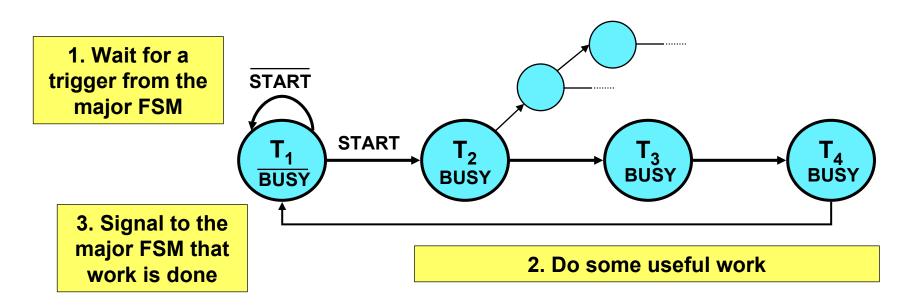

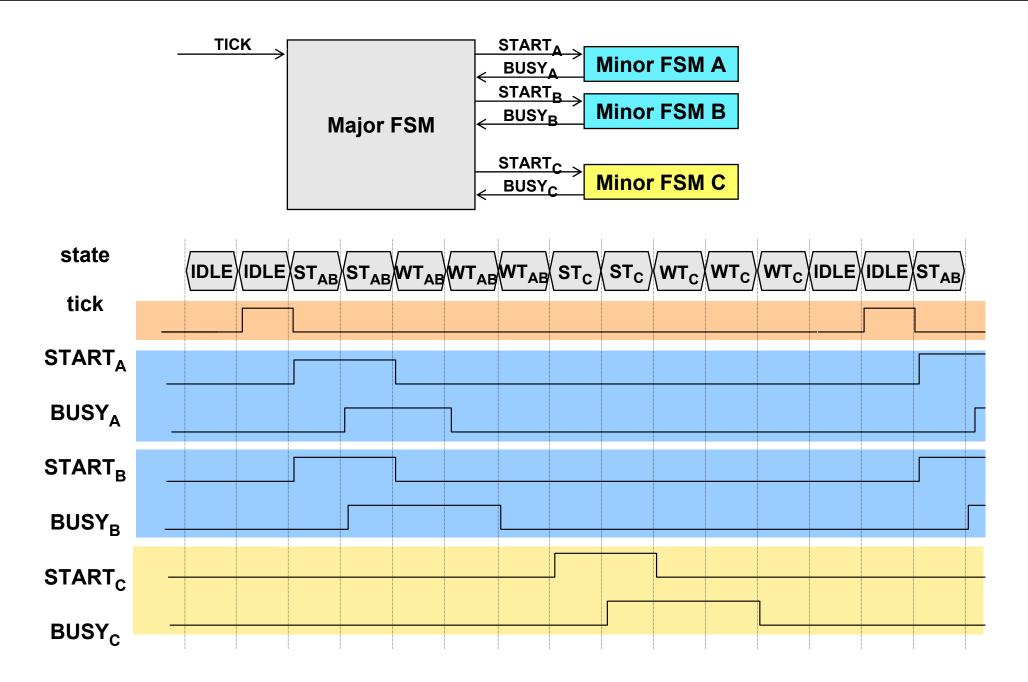

- Subtasks are encapsulated in minor FSMs with common reset and clock

- Simple communication abstraction:

START: tells the minor FSM to begin operation (the call)

BUSY: tells the major FSM whether the minor is done (the return)

- The major/minor abstraction is great for...

- □ Modular designs (*always* a good thing)

- Tasks that occur often but in different contexts

- □ Tasks that require a variable/unknown period of time

- Event-driven systems

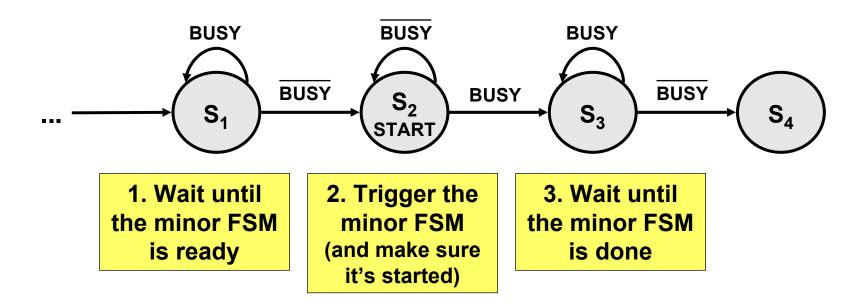

#### **Inside the Minor FSM**

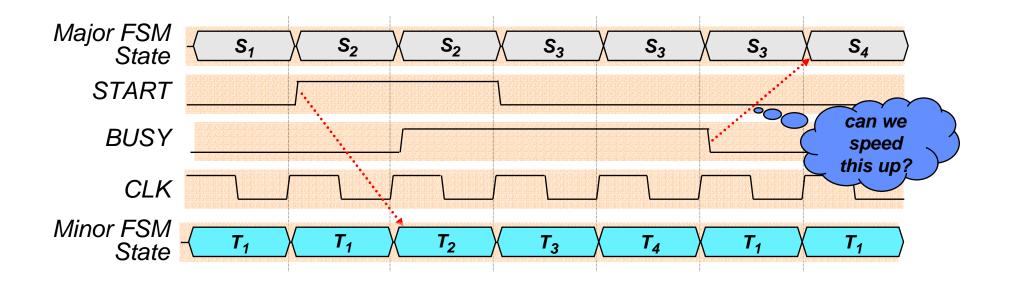

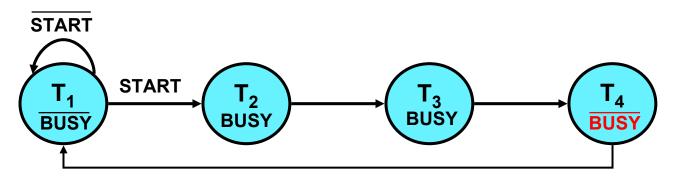

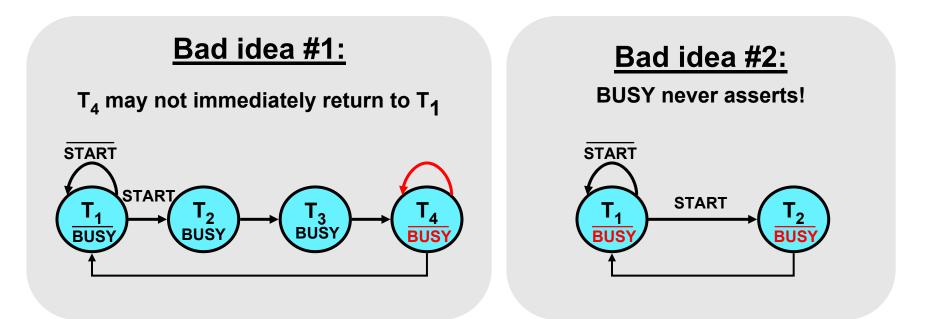

#### Good idea: de-assert BUSY one cycle early

### A Four-FSM Example

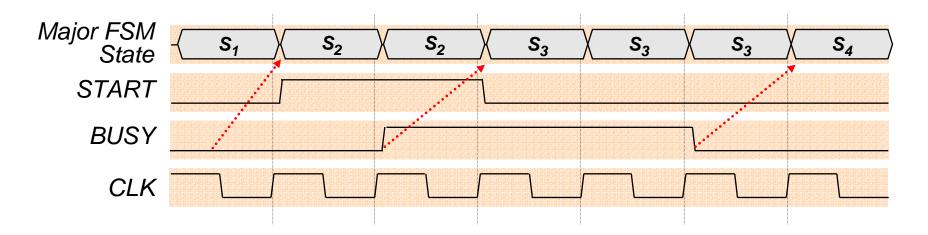

#### **Four-FSM Sample Waveform**

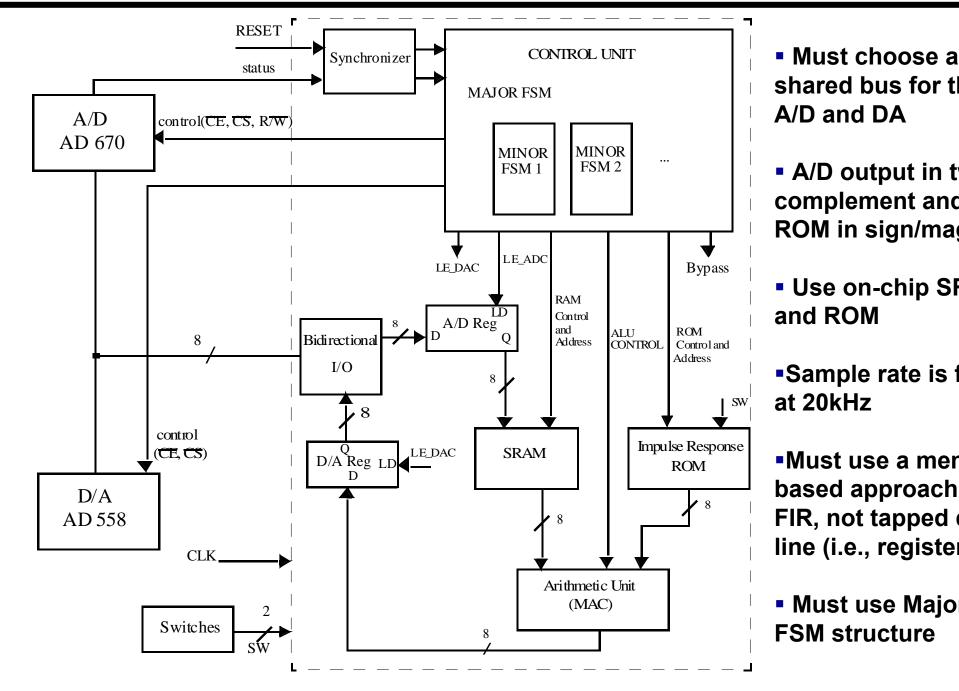

## Lab3 Block Diagram

shared bus for the A/D and DA A/D output in twos complement and **ROM** in sign/magnitude

Use on-chip SRAM and ROM

Sample rate is fixed at 20kHz

Must use a memory based approach to FIR, not tapped delay line (i.e., registers)

Must use Major/Minor **FSM** structure

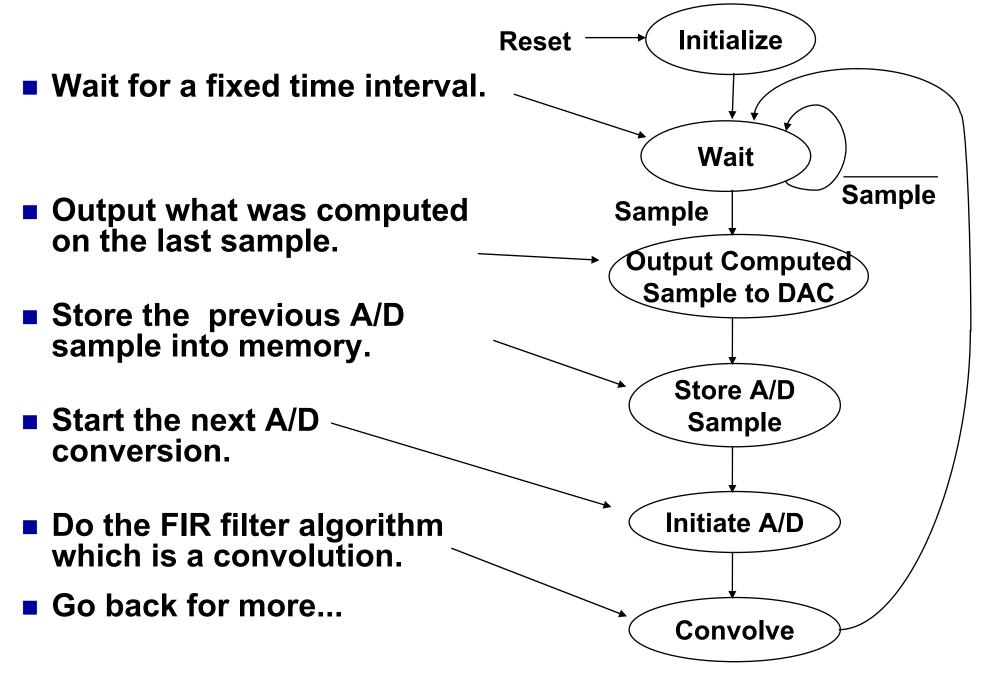

## **Control Flow for Lab3**

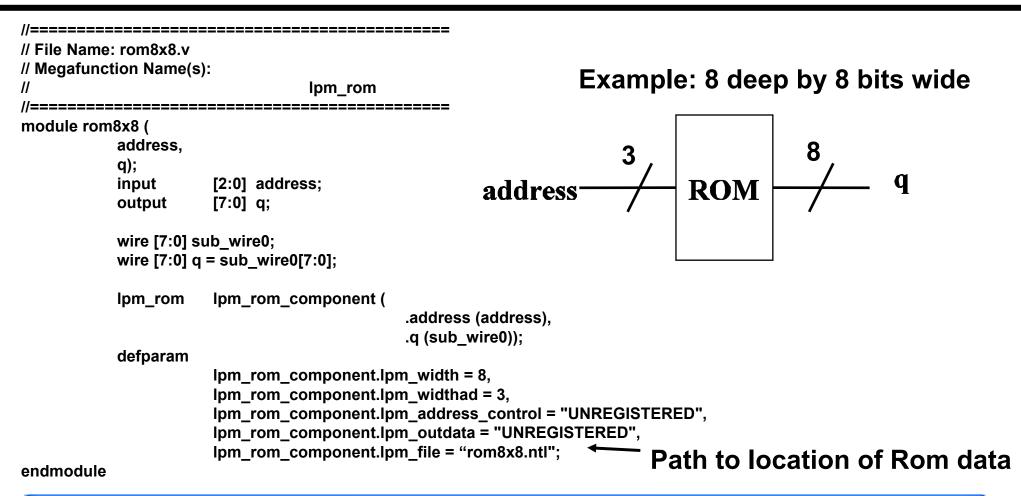

#### **Click on File** $\rightarrow$ MegaWizard Plug-In Manager

- □This starts up a series of windows so that you can specify parameters of the LPM module. You can choose

- ROM

- RAM

- **o** dp Dual Ported

- o dq Separate Inputs and Outputs

- o io TriState Inputs and Outputs (like the 6264)

- You choose the number of address bits and the word size.

- □You should specify a file to set the values of the ROM.

- □You can choose registered or unregistered inputs, outputs, and addresses.

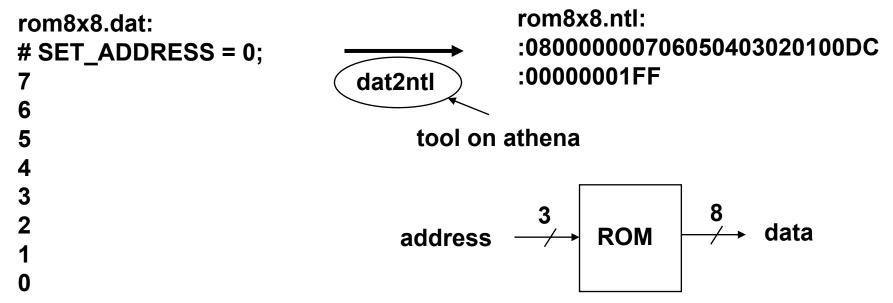

### **ROM Contents**

- Prepare a .dat file.

- You can type this in, write a computer program, get it from another application (speech or graphics, etc.)

- □ This has numbers separated by white space.

- The default base is HEX but you can use binary or decimal if you include the following statement (before the numbers).

# BASE = BINARY:

□ Insert, # SET\_ADDRESS = 0; (specifies that data should start at address 0)

- Run dat2ntl on Athena to format your .dat file into Intel HEX

- □ for details, after 'setup 6.111' type 'man dat2ntl'

dat2ntl <filename>.dat <filename>.ntl

See http://web.mit.edu/6.111/www/s2004/software.html for .mif format (memory initialization format)

| MAX+plus II File Edit View Node Assign Utilities Options Window Help    Image: Second | •  | MAX+plus II - c:\do        | ocuments and sett | ings\anantha\my      | documents\6.111                              | \verilog\lect | ture10\rom8 | 3x8 - [rom8  | 3x8.scf - Wave | form Editor] |            |         |          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----------------------------|-------------------|----------------------|----------------------------------------------|---------------|-------------|--------------|----------------|--------------|------------|---------|----------|

| Ref:    300.0ns    **    Time:    266.4ns    Interval:   33.6ns      Name:    Value:    100.0ns    200.0ns    300.0ns    400.0ns    500.0ns    600.0ns    700.0ns    800.0ns      ** address    H3    0    1    2    3    4    5    6    7    0      *    0    1    2    3    4    5    6    7    0      *    address    H3    0    1    2    3    4    5    6    7    0      *    07    06    05    04    03    02    01    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00    00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 23 | 🕻 MAX+plus II 🛛 File 🛛 Edi | it View Node Assi | gn Utilities Options | : Window Help                                |               |             |              |                |              |            |         | _ 8 ×    |

| Name:    Value:    100.0ns    200.0ns    300.0ns    400.0ns    500.0ns    600.0ns    700.0ns    800.0ns      address    H3    0    1    2    3    4    5    6    7    0      q    H05    07    06    05    04    3    02    01    00    1      Q    H05    07    06    05    04    3    02    01    00    1      Q    H05    07    06    05    04    1    03    02    01    00    1      Q    H05    07    06    05    04    1    03    02    01    00    1      Q    H05    07    06    05    04    1    03    02    01    00    1      Q    H05    07    06    05    04    1    03    02    01    00    1      Q    H05    07    06    05    04    1    03    02    01    00    <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    | ) 🖻 🖬 🚭 🐰 🖻                | a 🛍 🗠 💦 🛛         | 💊 🖻 🖻 🖉              | 🎜 🖹 👗                                        | <b>1 1</b>    | 🏶 🖗 🦉 🗿     | <b>r:</b> 52 | Q              |              |            |         |          |

| address    H3    0    1    2    3    4    5    6    7    0      q    H05    07    06    05    04    03    02    01    00    00      Q    Image: Constraint of the second sec                                                                                                                                                                                                                                                                                                           |    | 8                          | <b>+ +</b>        | Time: 266.4ns        | Interval                                     |               | 300.0ns     | $\bigcirc$   |                |              |            |         |          |

| Image: Hos      O7      X      O6      X      O4      X      O3      X      O2      X      O1      X      O0      X        Image: I                                                                                                                                                                                   | Ē  | 🗧 Name:                    | Value:            | 100.0ns              | 200.0ns                                      | 300           | Dns         | 400.0ns      | 500,0n;        | s 600        | ).Ons      | 700.0ns | 800.0ns  |

| ROM delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    | 🖅 address                  | Т нз Т            | <u> </u>             | <u>    1                                </u> | 2             | 3           | X            | 4 <u>X</u>     | 5            | <u>x</u> 6 | 77      | <u> </u> |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | <b>≠</b> ∞> q              | H 05              | 07                   | 06 🔪                                         | 05            | 0.          | 4            | 03             | 02           | )          | 01 (    | 00 ))    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |                            |                   |                      |                                              |               |             | $\bigcirc$   | ROM            | delay        | 1          |         | >        |

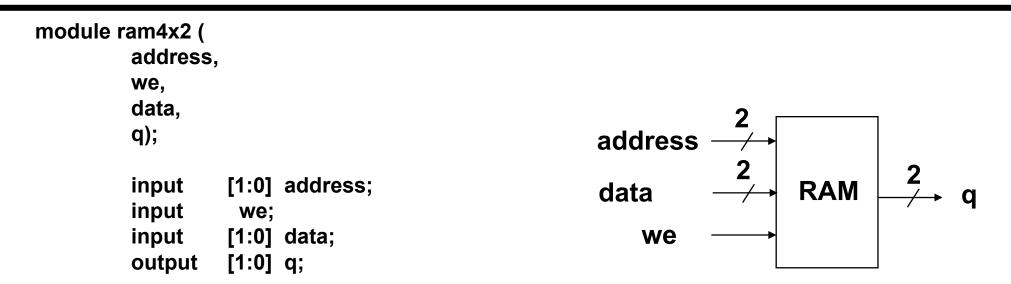

// megafunction wizard: %LPM RAM DQ% module ram4x2 ( address, address we, data, 2 RAM **q);** data a input [1:0] address; we input we; input [1:0] data; output [1:0] q; wire [1:0] sub wire0; wire [1:0] q = sub\_wire0[1:0]; lpm\_ram\_dqlpm\_ram\_dq\_component ( .address (address), .data (data), .we (we), .q (sub\_wire0)); defparam lpm\_ram\_dq\_component.lpm\_width = 2, lpm\_ram\_dq\_component.lpm\_widthad = 2, lpm ram dq component.lpm indata = "UNREGISTERED", lpm\_ram\_dq\_component.lpm\_address\_control = "UNREGISTERED", lpm\_ram\_dq\_component.lpm\_outdata = "UNREGISTERED", lpm\_ram\_dq\_component.lpm\_hint = "USE\_EAB=ON"; endmodule

#### endmodule

| 💼 M.                 | MAX+plus II - c:\documents and settings\anantha\my documents\6.111\verilog\lecture10\ram4x2 - [ram4x2.scf - Waveform Editor] |        |                   |                 |             |             |             |             |             |            |  |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------|--------|-------------------|-----------------|-------------|-------------|-------------|-------------|-------------|------------|--|--|

| 式 M                  | 📉 MAX+plus II File Edit View Node Assign Utilities Options Window Help 📃 🗗 🗙                                                 |        |                   |                 |             |             |             |             |             |            |  |  |

|                      | □ 🛱 🖶 🗧 🕺 💦 💊 № 💩 ▲ 🏛 🗮 🖉 🗑 🗑 🦓 🎘 🎘 👯 🍳                                                                                      |        |                   |                 |             |             |             |             |             |            |  |  |

| A                    | Ref: 200.0ns                                                                                                                 |        | ► ► Time: 741.0ns | Interval: 541.0 | Ins         |             |             |             |             | ^          |  |  |

| A                    |                                                                                                                              |        | 200.0ns           |                 |             |             |             |             |             |            |  |  |

| Æ                    | Name:                                                                                                                        | Value: | 200,0ns 400,0ns   | 600.0ns 800.0ns | 1.0us 1.2us | 1.4us 1.6us | 1.8us 2.0us | 2.2us 2.4us | 2.6us 2.8us | 3.0us 3.2i |  |  |

|                      | 🗩 we                                                                                                                         | 1      |                   |                 |             |             |             |             | _           |            |  |  |

|                      | 🗊 address                                                                                                                    | HO     | 0                 | 1               | 2           | 3           | X O         | ( 1 )       | 2           | (3         |  |  |

|                      | 🗊 data                                                                                                                       | H3     | 3                 | 2               | ( 1         | X           |             | 0           |             |            |  |  |

| Second second second | 💿 q                                                                                                                          | НО     | 0 () 3            | ) 0 ) 2         |             | ) 0         | Х. з        | 2           | χ1          | )          |  |  |

| Q                    |                                                                                                                              |        |                   | 📉 Lat           | ch interfa  | ace: Data   | must be     | setup and   | d held arc  | ound the   |  |  |

| E                    | 20.000                                                                                                                       | 1      |                   |                 |             |             |             | -           |             |            |  |  |

| 0                    | falling edge of the clock. Address must be setup before                                                                      |        |                   |                 |             |             |             |             |             |            |  |  |

|                      | rising edge and held after falling edge                                                                                      |        |                   |                 |             |             |             |             |             |            |  |  |

# SRAM with Registered Address and Data (Synchronous)

| 1                                         | MAX+plus II - c:\c | locuments an  | d settings\anantha\my (    | documents\6.111\v | erilog\lecture10 | \ram4x2_clocked | - [ram4x2_clocl | ked.scf - Wavefor | m Editor] |       |     |          | X        |

|-------------------------------------------|--------------------|---------------|----------------------------|-------------------|------------------|-----------------|-----------------|-------------------|-----------|-------|-----|----------|----------|

| 3                                         | MAX+plus II File E | dit View Node | e Assign Utilities Options | Window Help       |                  |                 |                 |                   |           |       |     | - 8      | X        |

| □ 2 2 3 1 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 |                    |               |                            |                   |                  |                 |                 |                   |           |       |     |          |          |

| R                                         | Ref: 0.0ns         |               | • 🔸 Time: 1.023us          | Interval:         | 1.023us          |                 |                 |                   |           |       |     |          | ^        |

| A                                         |                    | [             | 0.0ns                      |                   |                  |                 |                 |                   |           |       |     |          |          |

| }<br>A<br>€                               | Name:              | _Value: ]     | [ 200.0ns                  | 400.0ns           | 600.0ns          | 800.0ns         | 1.Ous           | 1.2us             | 1.4us     | 1.6us | 1   | 1.8us    |          |

|                                           | nclock             |               |                            |                   |                  |                 |                 |                   |           |       |     | 7        |          |

|                                           | in- we             | 0             |                            |                   |                  |                 |                 |                   |           |       |     |          |          |

|                                           | 🗊 address          | HO            | 0                          | 1)                | 2                | 3               | 0               | 1                 | 2         | 3)    | 0   | ) 1      |          |

| <u>0</u>                                  | 💕 data             | Н3            | 3                          | 0)                | 1 )              | 2               |                 |                   | 3         |       |     |          |          |

| Q<br>E                                    |                    | HO            |                            | 0                 | )( 1             | 0 2             | 3               | 0                 | 1         | 2     | _)( | 3        | )        |

| 0                                         | <                  |               |                            |                   |                  |                 |                 |                   |           |       |     |          | <b>V</b> |

| T                                         |                    |               |                            |                   |                  |                 |                 |                   |           |       |     | <u>/</u> |          |

**Register interface:**

Address, data and we should be setup and held on the rising edge of clock If we=1 on the rising edge, a write operation takes place If we=0 on the rising edge, a read operation takes place