# L4: Sequential Building Blocks (Flip-flops, Latches and Registers)

(Most) Lecture material derived from R. Katz, G. Borriello, "Contemporary Logic Design" (second edition), Prentice-Hall/Pearson Education, 2005. Some material from J. Rabaey, A. Chandrakasan, B. Nikolic, "Digital Integrated Circuits: A Design Perspective" Prentice-Hall/Pearson Education, 2003.

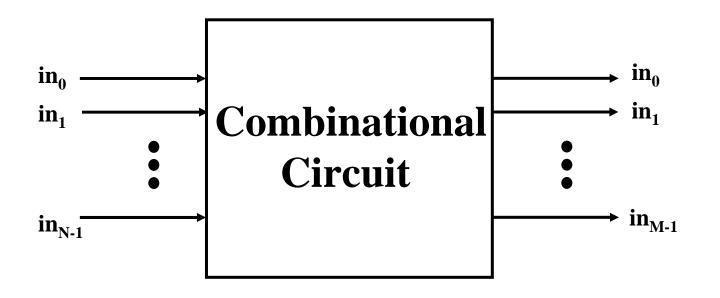

- Combinational logic circuits are memoryless

- No feedback in combinational logic circuits

- Output assumes the function implemented by the logic network, assuming that the switching transients have settled

- Outputs can have multiple logical transitions before settling to the correct value

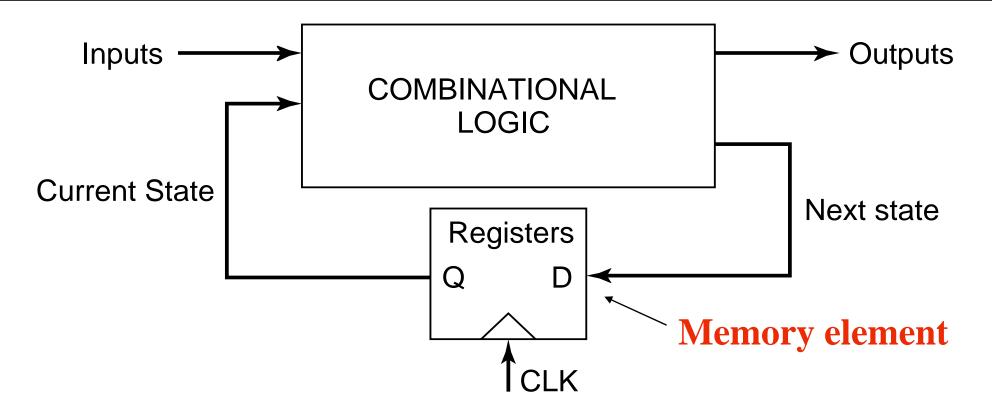

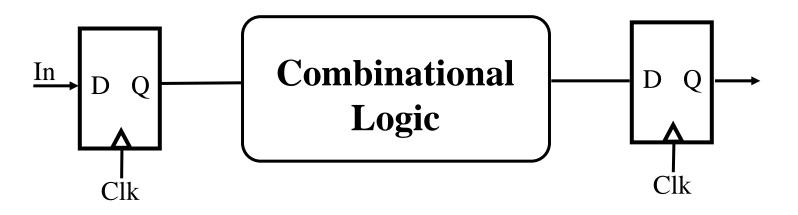

- Sequential circuits have memory (i.e., remember the past)

- The current state is "held" in memory and the next state is computed based the current state and the current inputs

- In a synchronous systems, the clock signal orchestrates the sequence of events

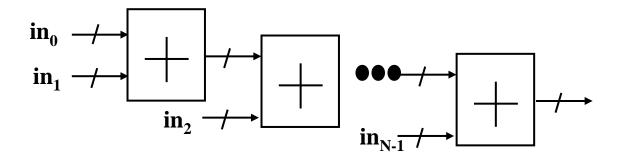

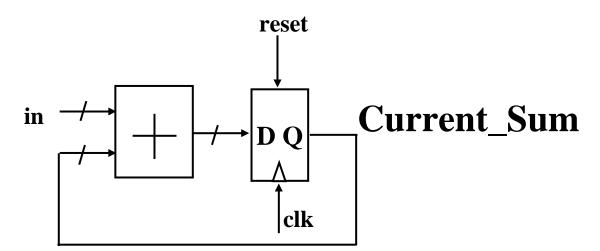

#### **Adding N inputs (N-1 Adders)**

### Using a sequential (serial) approach

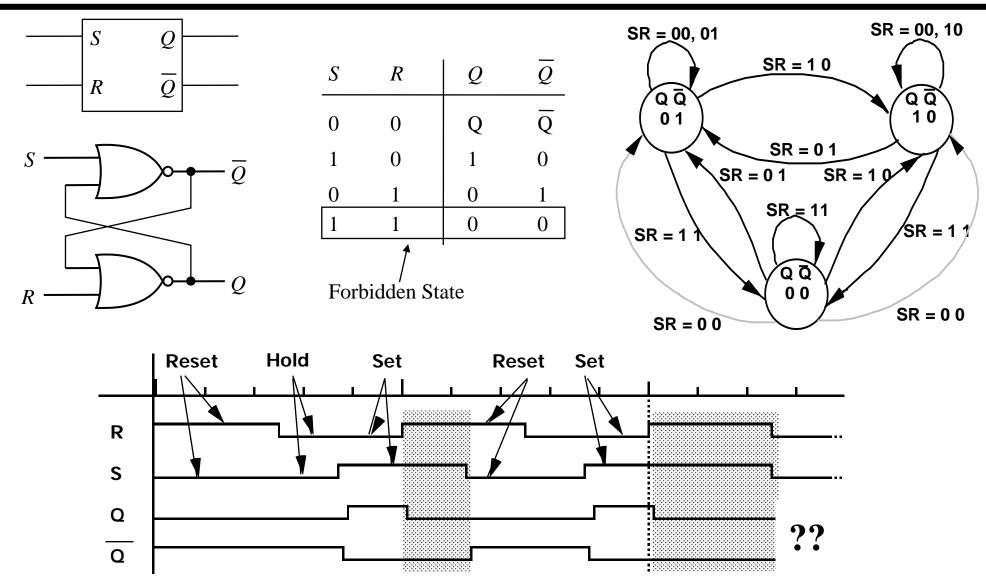

# NOR-based Set-Reset (SR) Flipflop

Flip-flop refers to a bi-stable element (edge-triggered registers are also called flip-flops) – this circuit is not clocked and outputs change "asynchronously" with the inputs

L4: 6.111 Spring 2005

**Introductory Digital Systems Laboratory**

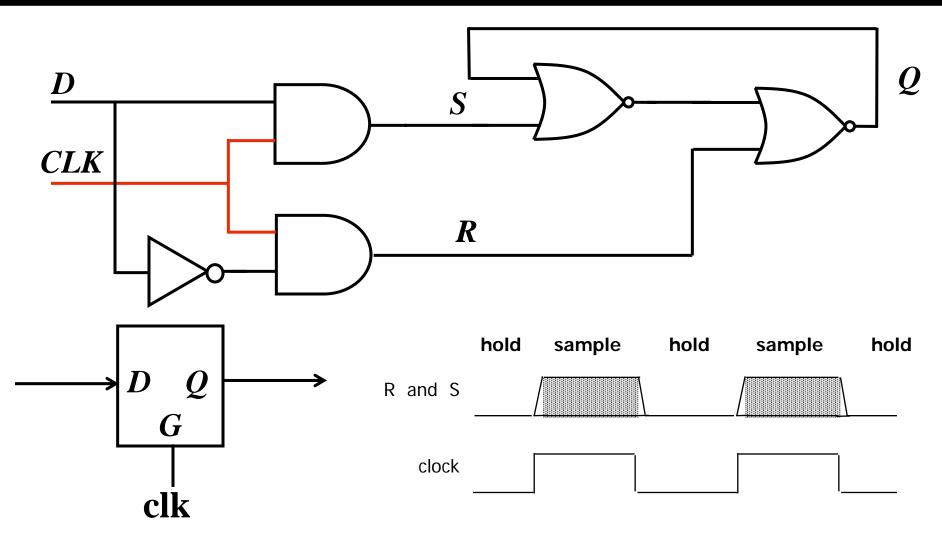

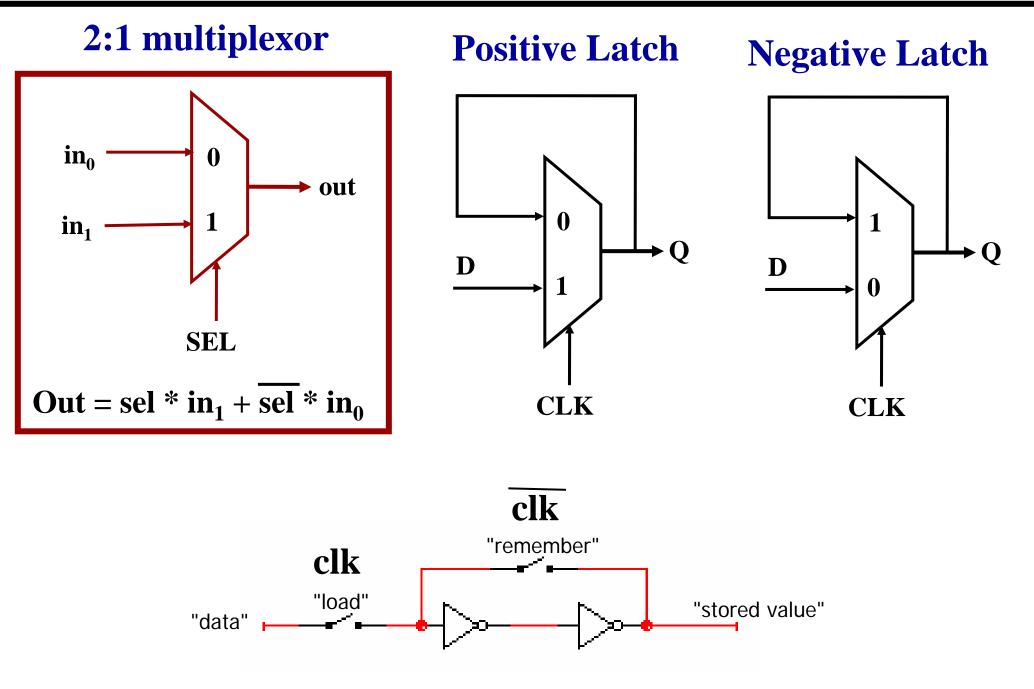

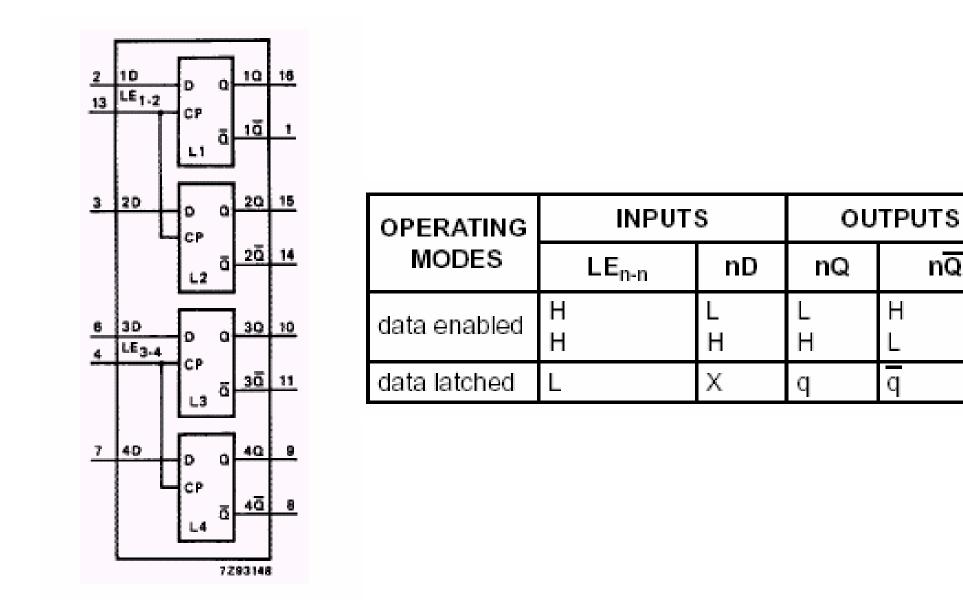

### Making a Clocked Memory Element: Positive D-Latch

- A Positive D-Latch: Passes input D to output Q when CLK is high and holds state when clock is low (i.e., ignores input D)

- A Latch is level-sensitive: invert clock for a negative latch

nQ

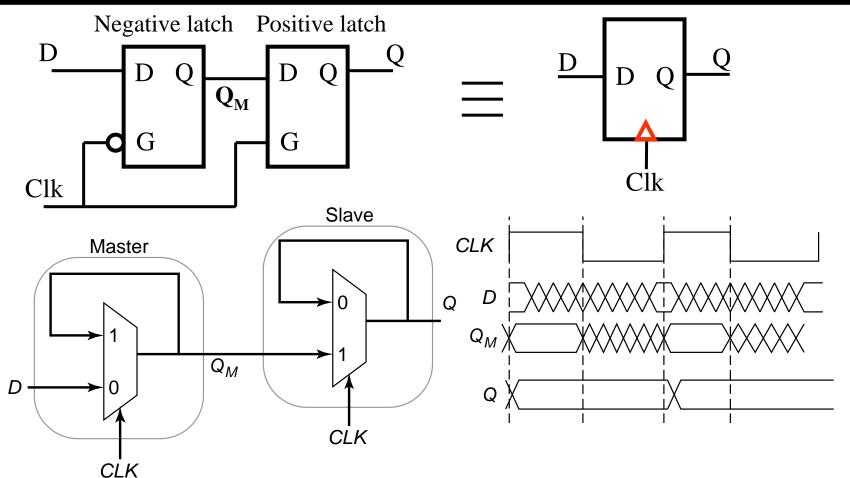

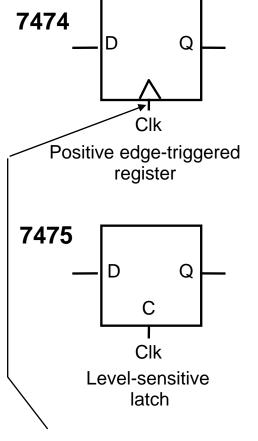

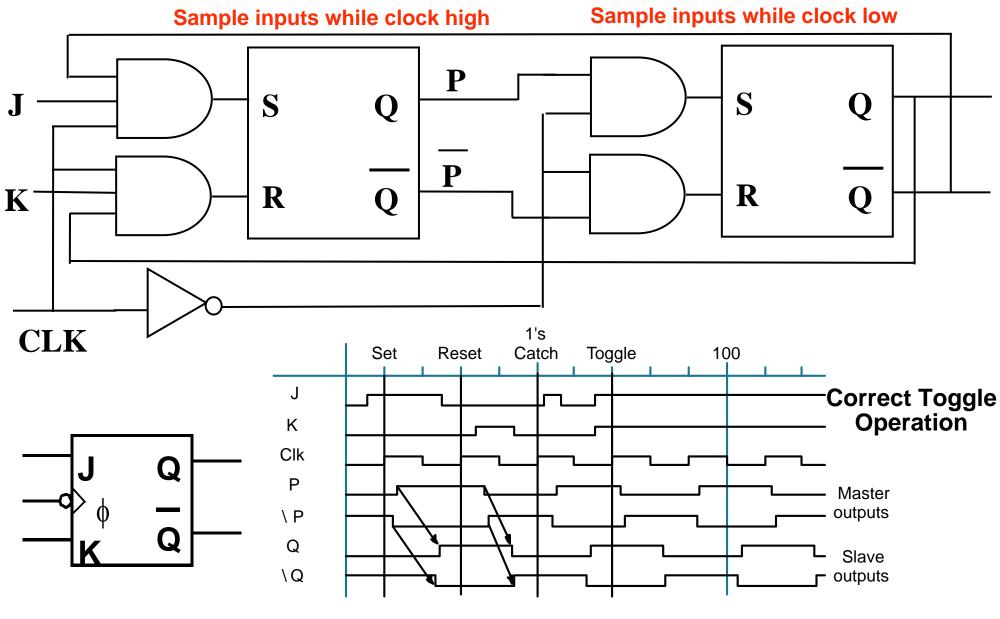

# **Building an Edge-Triggered Register**

- Master-Slave Register

- Use negative clock phase to latch inputs into first latch

- Use positive clock to change outputs with second latch

#### View pair as one basic unit

master-slave flip-flop twice as much logic

Bubble here for negative edge triggered register Edge triggered device sample inputs on the event edge

*Transparent latches* sample inputs as long as the clock is asserted

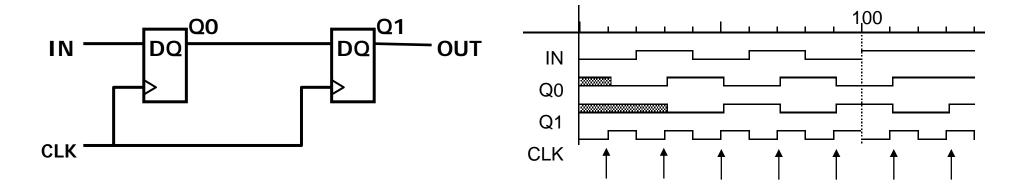

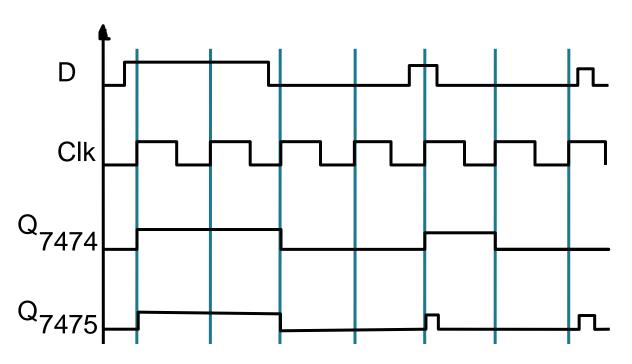

Timing Diagram:

Behavior the same unless input changes while the clock is high

Clock:

Periodic Event, causes state of memory element to change

memory element can be updated on the: rising *edge*, falling *edge*, high *level*, low *level*

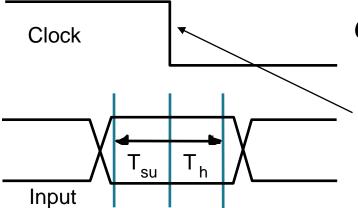

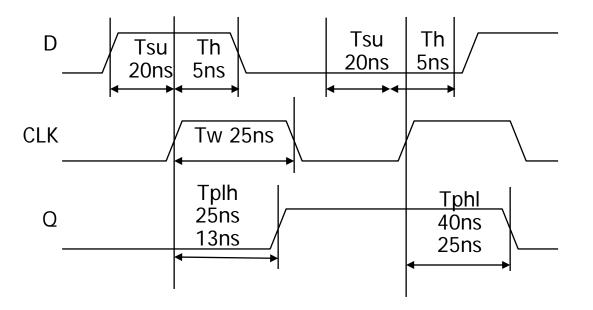

#### Setup Time (T<sub>su</sub>)

There is a timing "window" around the clocking event during which the input must remain stable and unchanged in order to be recognized Minimum time before the clocking event by which the input must be stable

#### Hold Time $(T_h)$

Minimum time after the clocking event during which the input must remain stable

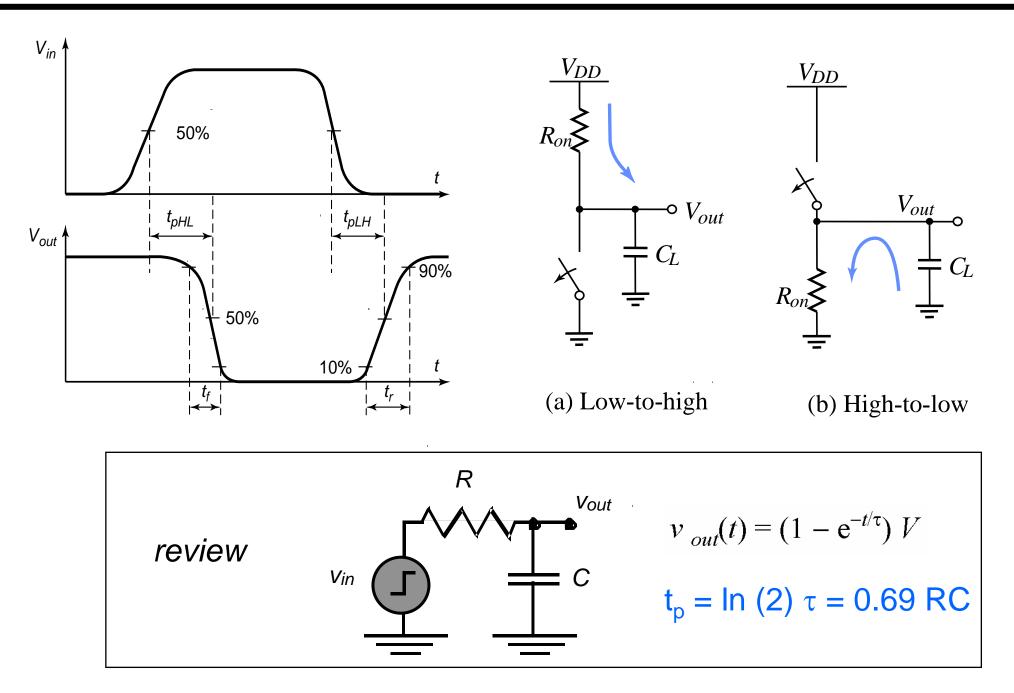

Propagation Delay ( $T_{cq}$  for an edge-triggered register and  $T_{dq}$  for a latch)

Delay overhead of the memory element

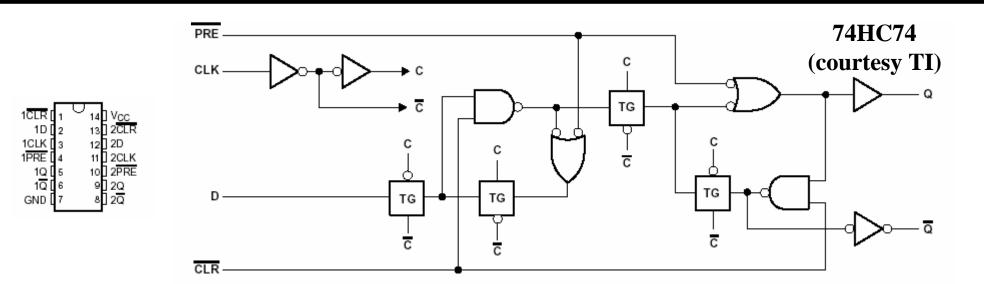

# 74HC74 (Positive Edge-Triggered Register)

|                        |                            |                     |       | T <sub>A</sub> = 25°C |     | SN54HC74 |     | SN74HC74 |     |      |

|------------------------|----------------------------|---------------------|-------|-----------------------|-----|----------|-----|----------|-----|------|

|                        |                            |                     | Vcc   | MIN                   | MAX | MIN      | MAX | MIN      | MAX | UNIT |

|                        |                            |                     | 2 V   | 0                     | 6   | 0        | 4.2 | 0        | 5   | MHz  |

| fclock Clock frequency |                            |                     | 4.5 V | 0                     | 31  | 0        | 21  | 0        | 25  |      |

|                        |                            |                     | 6 V   | 0                     | 36  | 0        | 25  | 0        | 29  |      |

|                        | Pulse duration             | PRE or CLR low      | 2 V   | 100                   |     | 150      |     | 125      |     | ns   |

|                        |                            |                     | 4.5 V | 20                    |     | 30       |     | 25       |     |      |

|                        |                            |                     | 6 V   | 17                    |     | 25       |     | 21       |     |      |

| t <sub>W</sub>         |                            | CLK high or low     | 2 V   | 80                    |     | 120      |     | 100      |     |      |

|                        |                            |                     | 4.5 V | 16                    |     | 24       |     | 20       |     |      |

|                        |                            |                     | 6 V   | 14                    |     | 20       |     | 17       |     |      |

|                        | Setup time before CLK1     | Data                | 2 V   | 100                   |     | 150      |     | 125      |     | ns   |

|                        |                            |                     | 4.5 V | 20                    |     | 30       |     | 25       |     |      |

| +                      |                            |                     | 6 V   | 17                    |     | 25       |     | 21       |     |      |

| t <sub>su</sub>        |                            | PRE or CLR inactive | 2 V   | 25                    |     | 40       |     | 30       |     |      |

|                        |                            |                     | 4.5 V | 5                     |     | 8        |     | 6        |     |      |

|                        |                            |                     | 6 V   | 4                     |     | 7        |     | 5        |     |      |

| th                     |                            |                     | 2 V   | 0                     |     | 0        |     | 0        |     |      |

|                        | Hold time, data after CLK↑ |                     | 4.5 V | 0                     |     | 0        |     | 0        |     | ns   |

|                        |                            |                     | 6 V   | 0                     |     | 0        |     | 0        |     |      |

| FUNCTION TABLE |     |         |   |    |    |  |  |

|----------------|-----|---------|---|----|----|--|--|

|                | INP | OUTPUTS |   |    |    |  |  |

| PRE            | CLR | CLK     | D | Q  | Q  |  |  |

| L              | н   | Х       | Х | н  | L  |  |  |

| н              | L   | х       | Х | L  | н  |  |  |

| L              | L   | Х       | Х | нt | нt |  |  |

↑

$\uparrow$

L

**D-FF** with preset and clear

н

L

Х

н

L

Q<sub>0</sub>

L

н

$\overline{Q}_0$

н

Н

н

Н

н

н

#### Introductory Digital Systems Laboratory

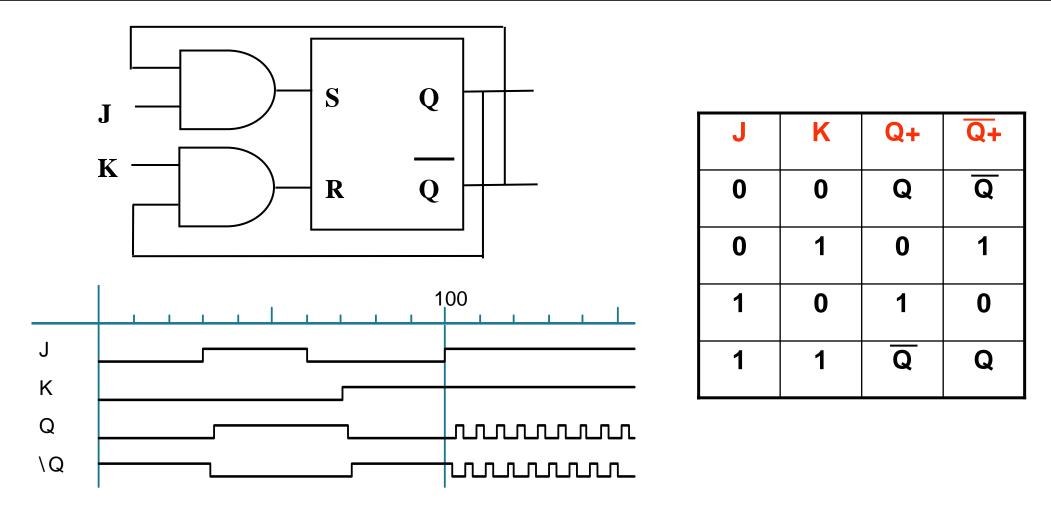

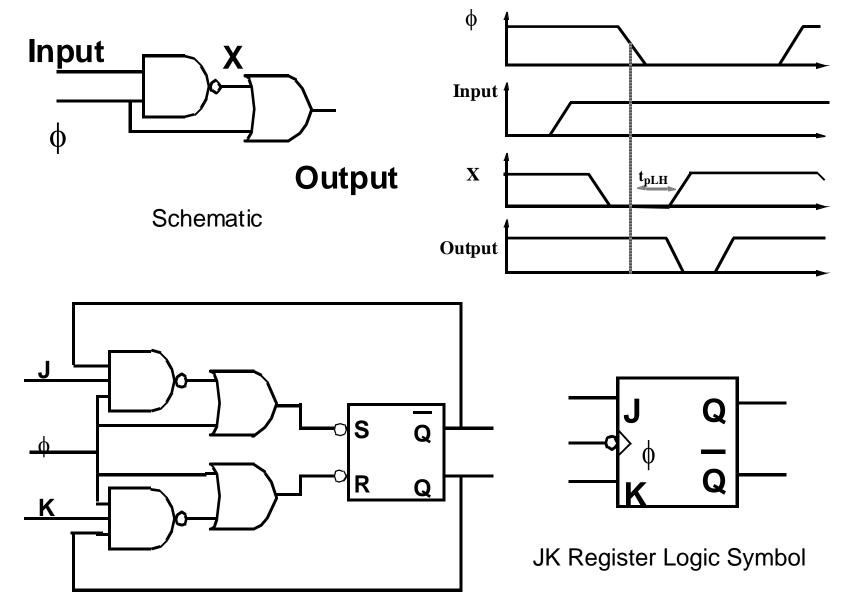

# **The J-K Flip-Flop**

Eliminate the forbidden state of the SR Flip-flop

#### Use output feedback to guarantee that R and S are never both one

Is there a problem with this circuit?

# Pulse Based Edge-Triggered J-K Register

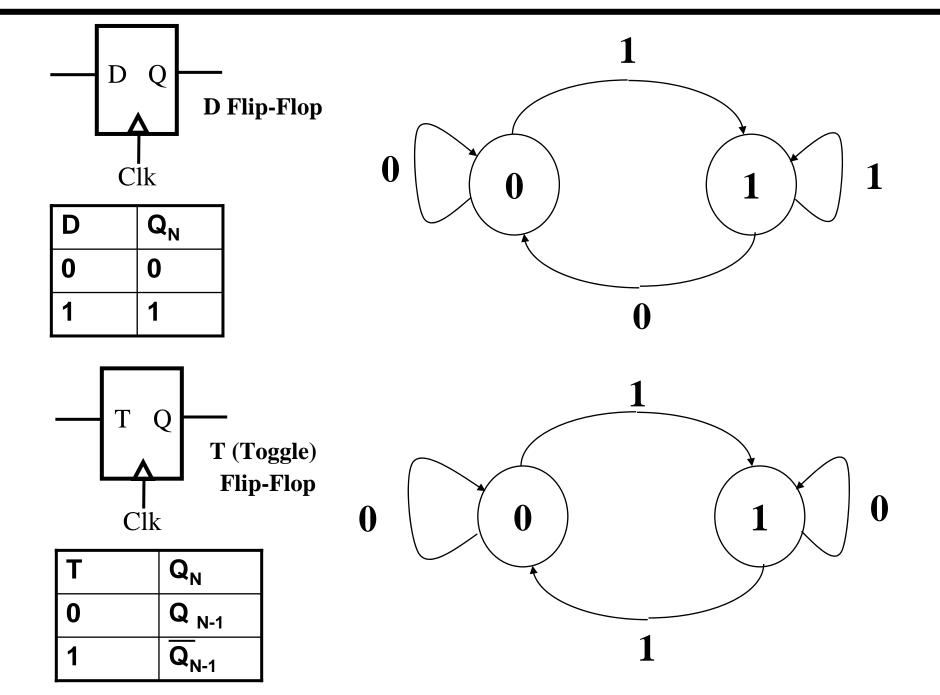

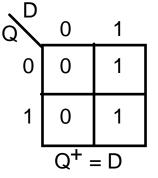

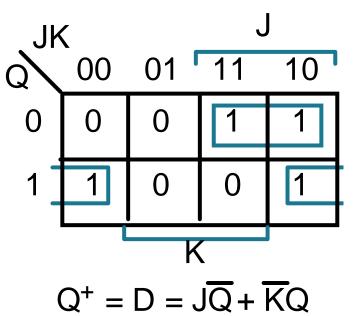

# D Flip-Flop vs. Toggle Flip-Flop

Realizing different types of memory elements

#### **Characteristic Equations**

D: Q+ = DJ-K:  $Q+ = J\overline{Q} + \overline{K}Q$ T:  $Q+ = T\overline{Q} + \overline{T}Q$

E.g., J=K=0, then Q+ = Q J=1, K=0, then Q+ = 1 J=0, K=1, then Q+ =  $\frac{0}{J=1}$ , K=1, then Q+ = Q

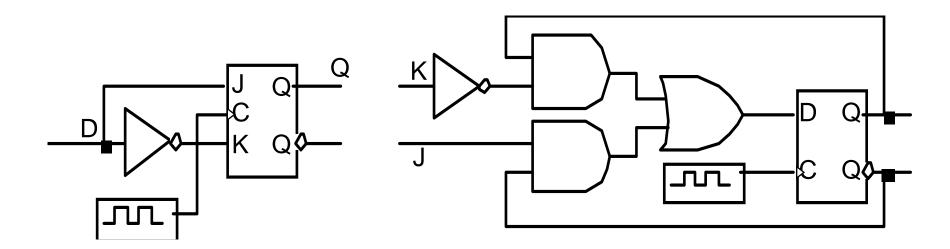

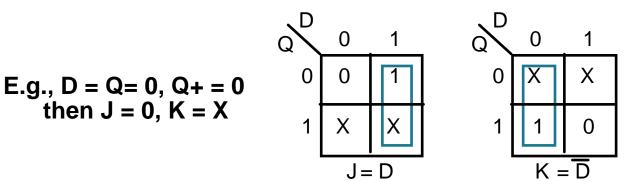

Implementing One FF in Terms of Another

D implemented with J-K

J-K implemented with D

# **Design Procedure**

Excitation Tables: What are the necessary inputs to cause a particular kind of change in state?

| Q | Q+               | J | Κ | Т | D |

|---|------------------|---|---|---|---|

| 0 | 0                | 0 | Χ | 0 | 0 |

| 0 | 1                | 1 | Χ | 1 | 1 |

| 1 | 0                | Χ | 1 | 1 | 0 |

| 1 | 0<br>1<br>0<br>1 | X | 0 | 0 | 1 |

Implementing D FF with a J-K FF:

- 1) Start with K-map of Q + = f(D, Q)

- 2) Create K-maps for J and K with same inputs (D, Q)

- 3) Fill in K-maps with appropriate values for J and K to cause the same state changes as in the original K-map

Implementing J-K FF with a D FF:

- 1) K-Map of Q+ = F(J, K, Q)

- 2,3) Revised K-map using D's excitation table its the same! that is why design procedure with D FF is simple!

Resulting equation is the combinational logic input to D to cause same behavior as J-K FF. Of course it is identical to the characteristic equation for a J-K FF.

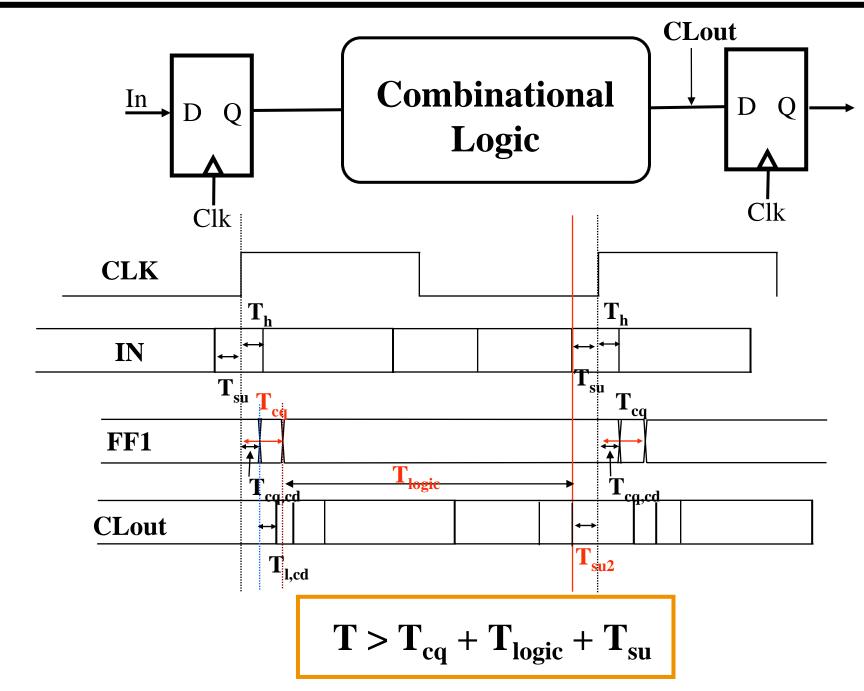

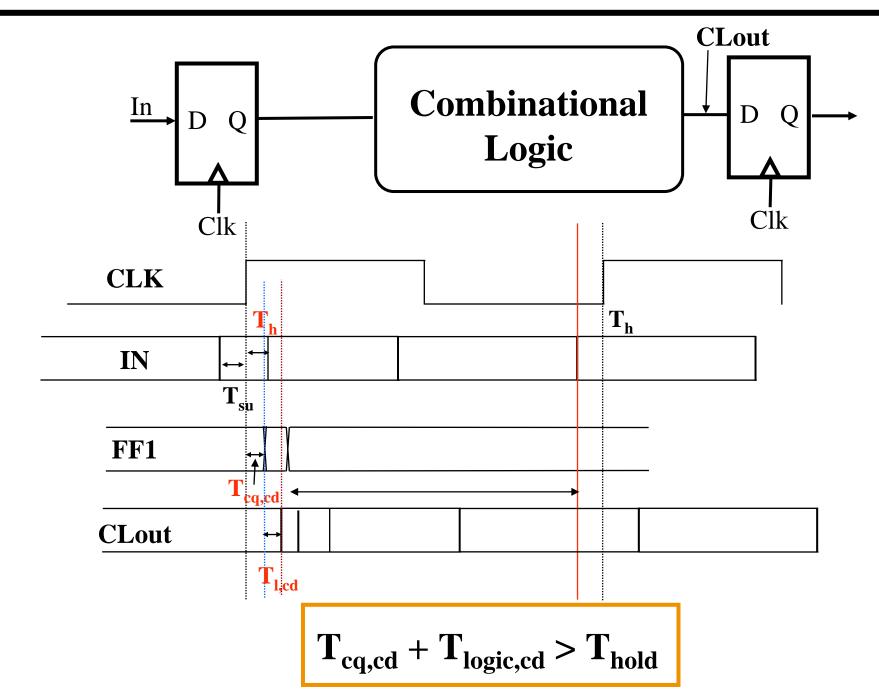

### **Register Timing Parameters**

$T_{cq}$ : worst case rising edge clock to q delay  $T_{cq, cd}$ : contamination or minimum delay from clock to q  $T_{su}$ : setup time  $T_h$ : hold time

## **Logic Timing Parameters**

T<sub>logic</sub> : worst case delay through the combinational logic network T<sub>logic,cd</sub>: contamination or minimum delay through logic network

# **Delay in Digital Circuits**

# System Timing (I): Minimum Period

# System Timing (II): Minimum Delay

#### Typical parameters for Positive edge-triggered D Register

all measurements are made from the clocking event that is, the rising edge of the clock

Shift-register