## **L6: FSMs and Synchronization**

**Lecture material courtesy of Rex Min**

#### **Asynchronous Inputs in Sequential Systems**

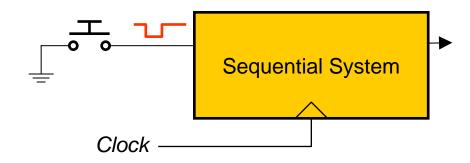

#### What about external signals?

Can't guarantee setup and hold times will be met!

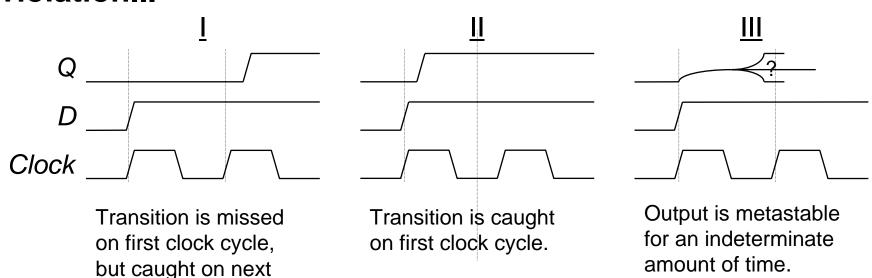

# When an asynchronous signal causes a setup/hold violation...

**Q: Which cases are problematic?**

clock cycle.

#### **Asynchronous Inputs in Sequential Systems**

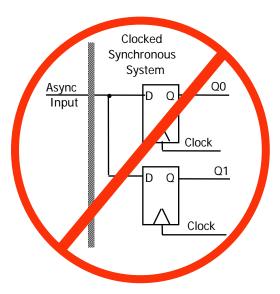

All of them can be, if more than one happens simultaneously within the same circuit.

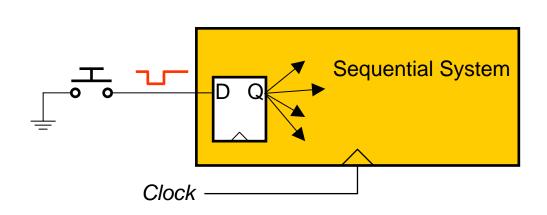

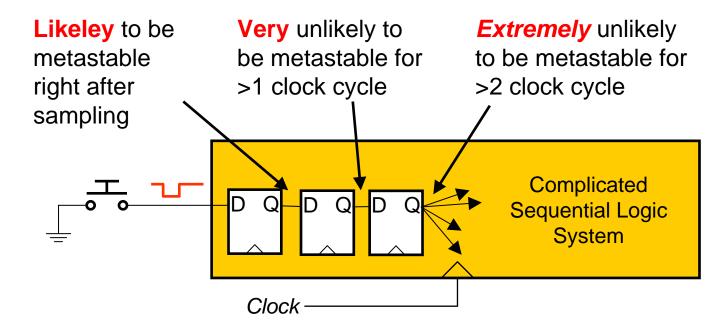

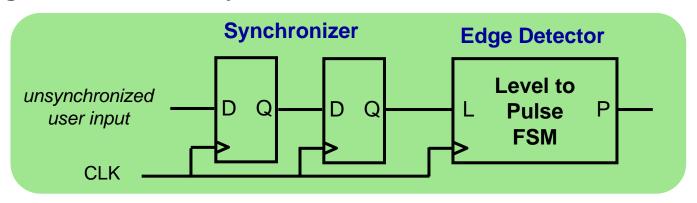

Idea: ensure that external signals directly feed exactly one flip-flop

This prevents the possibility of I and II occurring in different places in the circuit, but what about metastability?

## **Handling Metastability**

- Preventing metastability turns out to be an impossible problem

- High gain of digital devices makes it likely that metastable conditions will resolve themselves quickly

- Solution to metastability: allow time for signals to stabilize

#### How many registers are necessary?

- Depends on many design parameters(clock speed, device speeds, ...)

- In 6.111, one or maybe two synchronization registers is sufficient

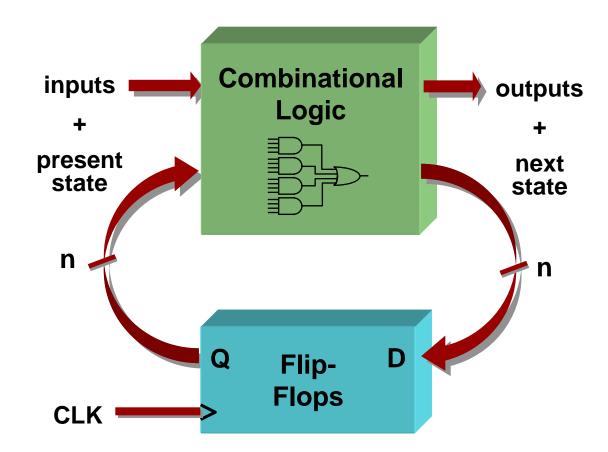

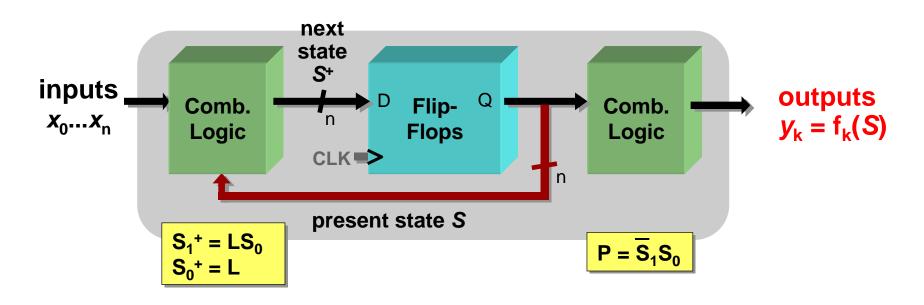

#### **Finite State Machines**

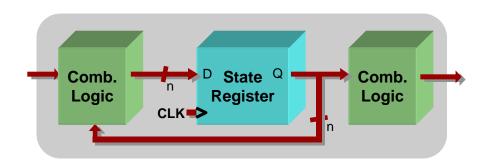

- Finite State Machines (FSMs) are a useful abstraction for sequential circuits with centralized "states" of operation

- At each clock edge, combinational logic computes outputs and next state as a function of inputs and present state

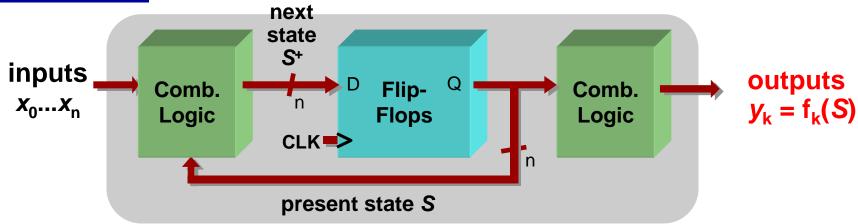

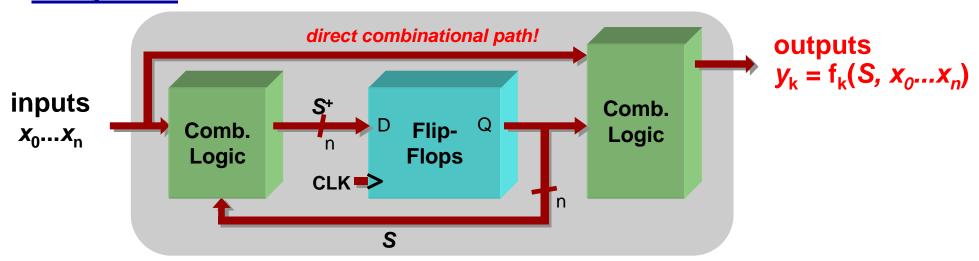

## **Two Types of FSMs**

#### **Moore and Mealy FSMs are distinguished by their output generation**

#### **Moore FSM:**

#### **Mealy FSM:**

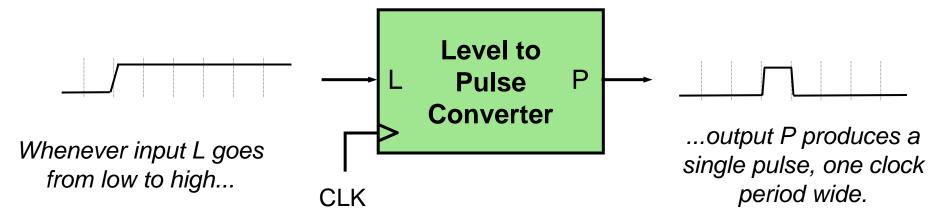

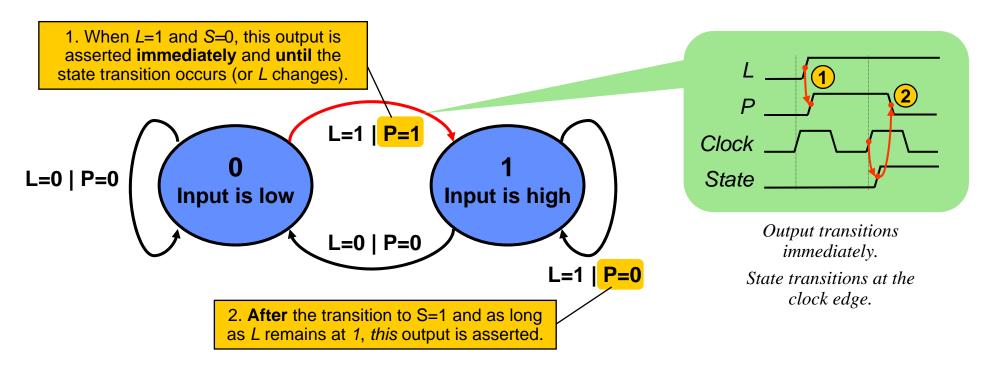

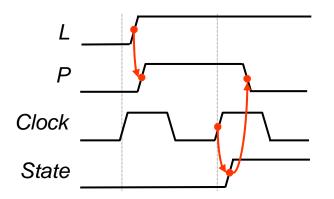

#### **Design Example: Level-to-Pulse**

- A level-to-pulse converter produces a single-cycle pulse each time its input goes high.

- In other words, it's a synchronous risingedge detector.

- Sample uses:

- Buttons and switches pressed by humans for arbitrary periods of time

- □ Single-cycle enable signals for counters

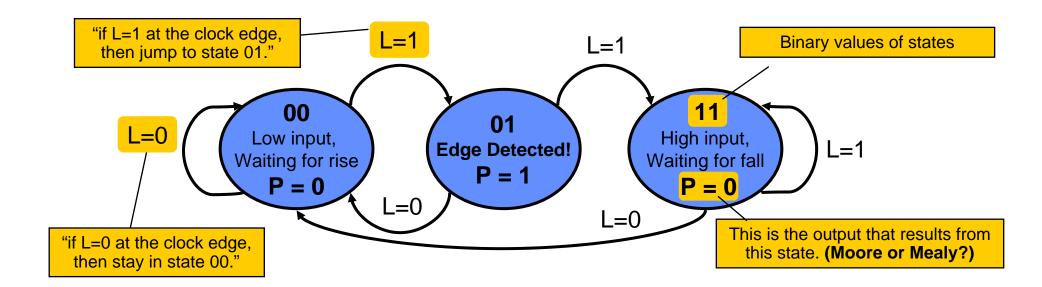

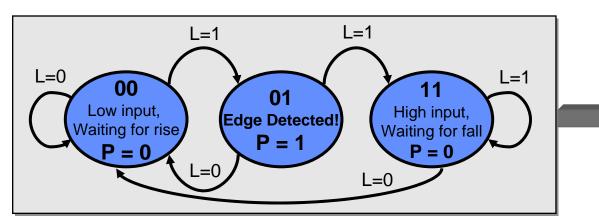

#### **State Transition Diagrams**

Block diagram of desired system:

State transition diagram is a useful FSM representation and design aid

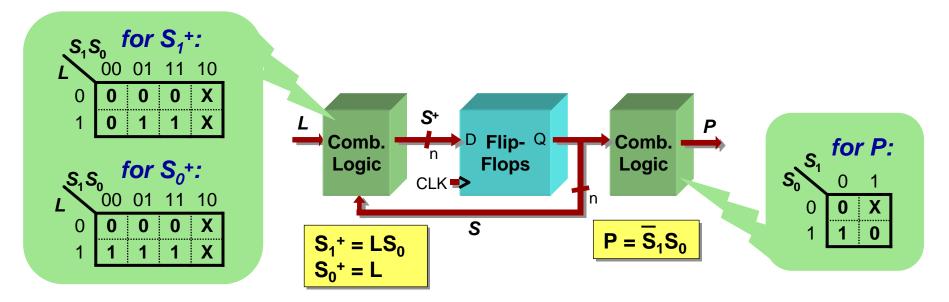

#### **Logic Derivation for a Moore FSM**

Transition diagram is readily converted to a state transition table (just a truth table)

| Current<br>State |    | In | Next<br>State           |                         | Out |

|------------------|----|----|-------------------------|-------------------------|-----|

| S <sub>1</sub>   | So | L  | <b>S</b> <sub>1</sub> + | <b>S</b> <sub>0</sub> + | P   |

| 0                | 0  | 0  | 0                       | 0                       | 0   |

| 0                | 0  | 1  | 0                       | 1                       | 0   |

| 0                | 1  | 0  | 0                       | 0                       | 1   |

| 0                | 1  | 1  | 1                       | 1                       | 1   |

| 1                | 1  | 0  | 0                       | 0                       | 0   |

| 1                | 1  | 1  | 1                       | 1                       | 0   |

Combinational logic may be derived by Karnaugh maps

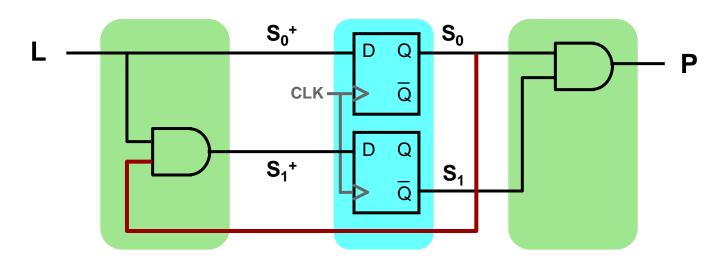

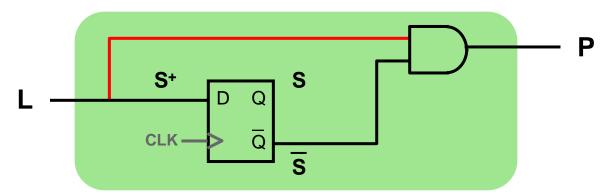

#### **Moore Level-to-Pulse Converter**

#### Moore FSM circuit implementation of level-to-pulse converter:

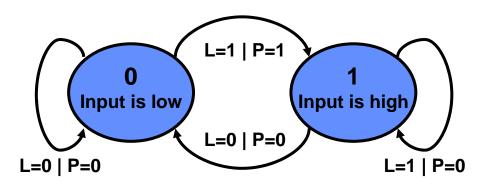

## **Design of a Mealy Level-to-Pulse**

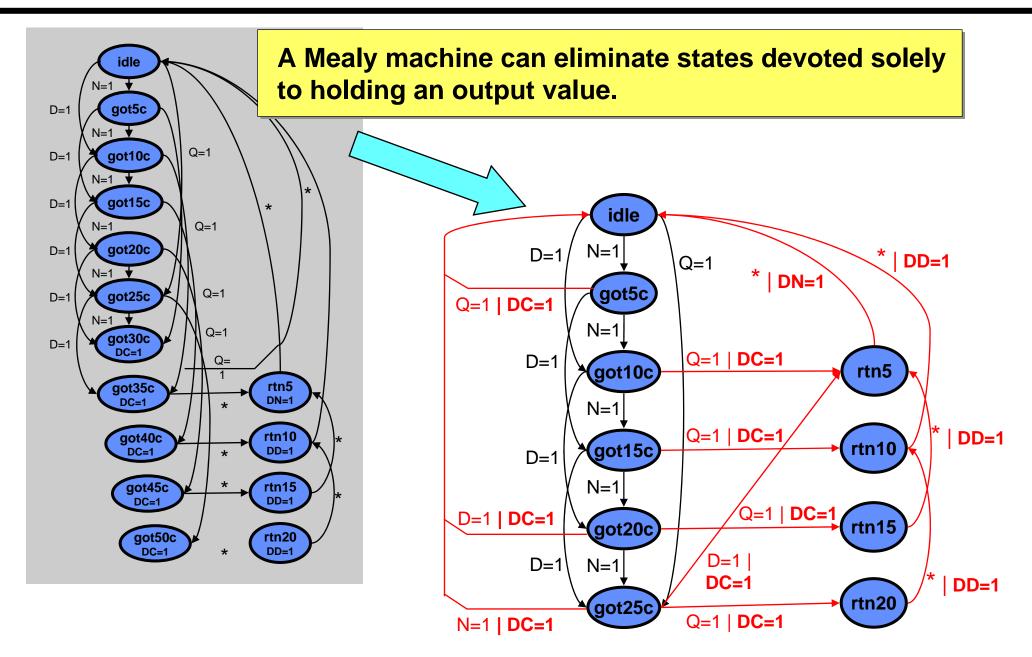

Since outputs are determined by state and inputs, Mealy FSMs may need fewer states than Moore FSM implementations

## **Mealy Level-to-Pulse Converter**

| Pres.<br>State | In | Next<br>State  | Out |

|----------------|----|----------------|-----|

| S              | L  | S <sup>+</sup> | P   |

| 0              | 0  | 0              | 0   |

| 0              | 1  | 1              | 1   |

| 1              | 0  | 0              | 0   |

| 1              | 1  | 1              | 0   |

#### Mealy FSM circuit implementation of level-to-pulse converter:

- FSM's state simply remembers the previous value of L

- Circuit benefits from the Mealy FSM's implicit single-cycle assertion of outputs during state transitions

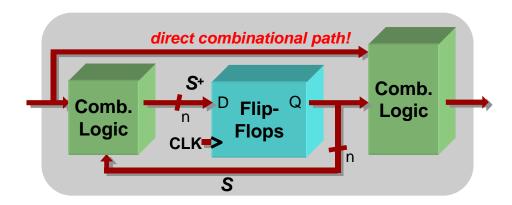

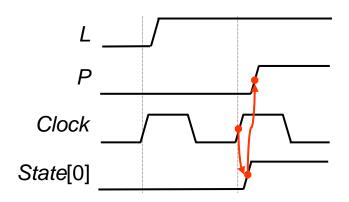

## **Moore/Mealy Trade-Offs**

- Remember that the difference is in the output:

- Moore outputs are based on state only

- ☐ Mealy outputs are based on state *and input*

- □ Therefore, Mealy outputs generally occur one cycle earlier than a Moore:

Moore: delayed assertion of P

Mealy: immediate assertion of P

- Compared to a Moore FSM, a Mealy FSM might...

- ☐ Be more difficult to conceptualize and design

- □ Have fewer states

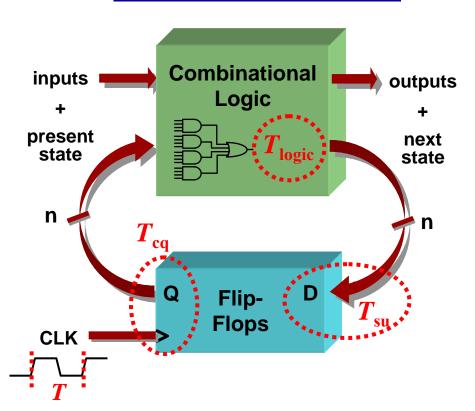

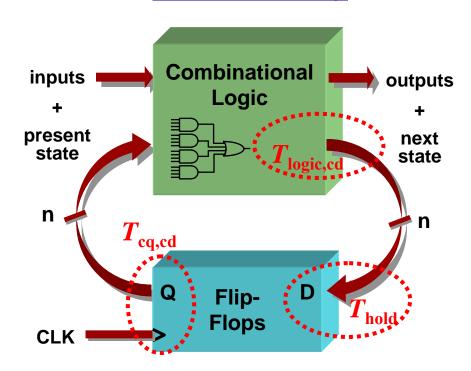

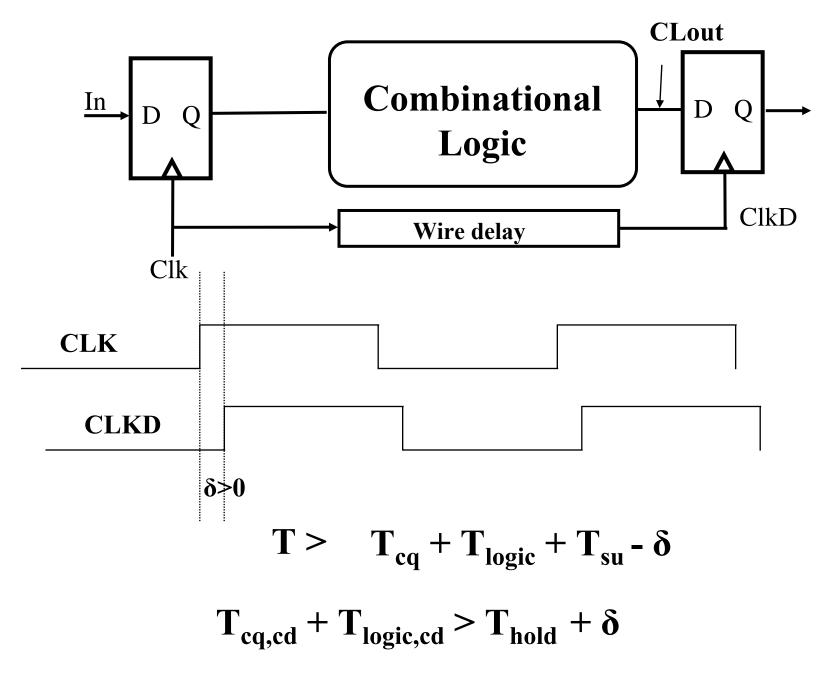

## **FSM Timing Requirements**

Timing requirements for FSM are identical to any generic sequential system with feedback

#### **Minimum Clock Period**

$$T > T_{cq} + T_{logic} + T_{su}$$

#### **Minimum Delay**

$$T_{cq,cd} + T_{logic,cd} > T_{hold}$$

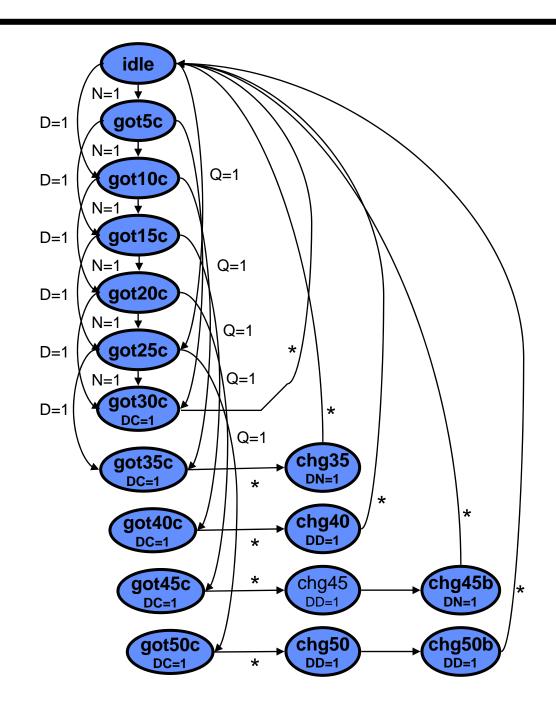

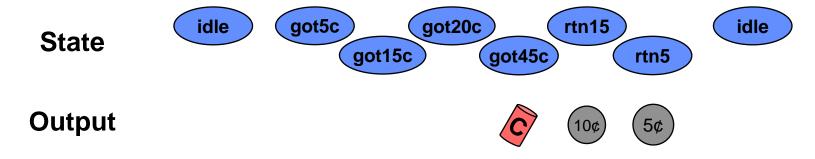

## The 6.111 Vending Machine

- Lab assistants demand a new soda machine for the 6.111 lab.

You design the FSM controller.

- All selections are \$0.30.

- The machine makes change. (Dimes and nickels only.)

- Inputs: limit 1 per clock

- □ Q quarter inserted

- D dime inserted

- □ N nickel inserted

- Outputs: limit 1 per clock

- □ DC dispense can

- □ DD dispense dime

- □ DN dispense nickel

## What States are in the System?

A starting (idle) state:

A state for each possible amount of money captured:

■ What's the maximum amount of money captured before purchase?

25 cents (just shy of a purchase) + one quarter (largest coin)

States to dispense change (one per coin dispensed):

#### A Moore Vender

Here's a first cut at the state transition diagram.

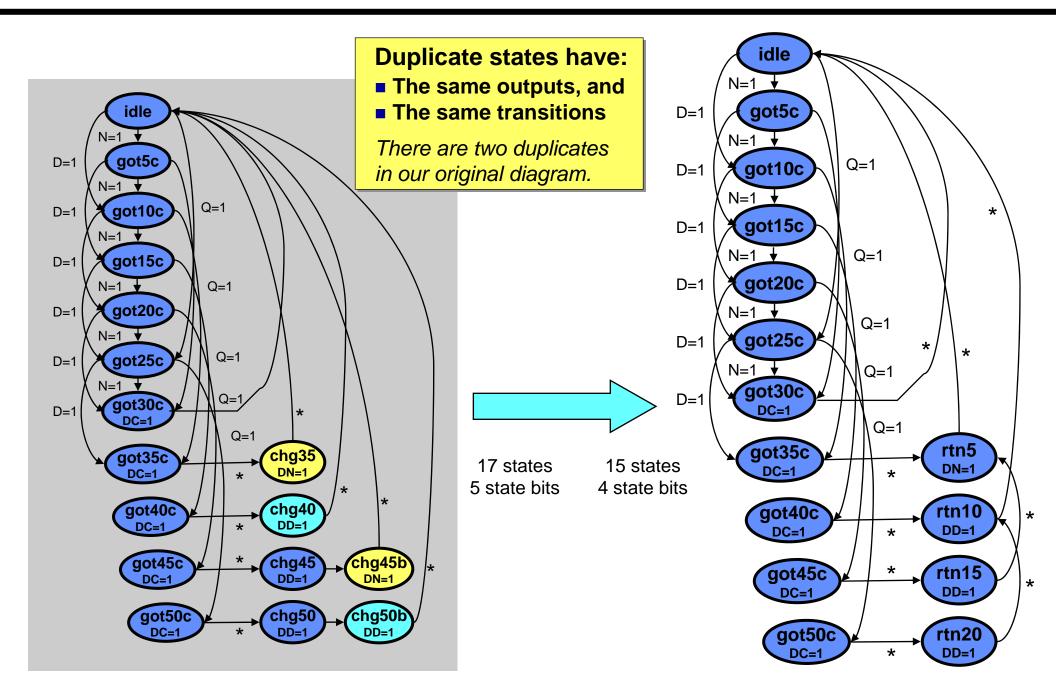

#### **State Reduction**

#### **Verilog for the Moore Vender**

# FSMs are easy in Verilog. Simply write one of each:

- State register (sequential always block)

- Next-state combinational logic (comb. always block with case)

- Output combinational logic block (comb. always block or assign statements)

#### States defined with parameter keyword

```

parameter IDLE = 0;

parameter GOT_5c = 1;

parameter GOT_10c = 2;

parameter GOT_15c = 3;

parameter GOT_20c = 4;

parameter GOT_25c = 5;

parameter GOT_30c = 6;

parameter GOT_35c = 7;

parameter GOT_40c = 8;

parameter GOT_45c = 9;

parameter GOT_50c = 10;

parameter RETURN_20c = 11;

parameter RETURN_15c = 12;

parameter RETURN_5c = 14;

```

# State register defined with sequential always block

```

always @ (posedge clk or negedge reset)

if (!reset) state <= IDLE;

else state <= next;</pre>

```

#### **Verilog for the Moore Vender**

## Next-state logic within a combinational always block

```

always @ (state or N or D or Q) begin

case (state)

IDLE: if (Q) next = GOT 25c;

else if (D) next = GOT 10c;

else if (N) next = GOT 5c;

else next = IDLE;

GOT 5c: if (Q) next = GOT 30c;

else if (D) next = GOT 15c;

else if (N) next = GOT 10c;

else next = GOT 5c;

GOT 10c: if (Q) next = GOT 35c;

else if (D) next = GOT 20c;

else if (N) next = GOT 15c;

else next = GOT_10c;

GOT 15c: if (Q) next = GOT 40c;

else if (D) next = GOT 25c;

else if (N) next = GOT 20c;

else next = GOT 15c;

GOT 20c: if (Q) next = GOT 45c;

else if (D) next = GOT 30c;

else if (N) next = GOT 25c;

else next = GOT 20c;

```

```

GOT 25c: if (Q) next = GOT 50c;

else if (D) next = GOT 35c;

else if (N) next = GOT 30c;

else next = GOT 25c;

GOT 30c: next = IDLE;

GOT 35c: next = RETURN 5c;

GOT 40c: next = RETURN 10c;

GOT 45c: next = RETURN 15c;

GOT 50c: next = RETURN 20c;

RETURN 20c: next = RETURN 10c;

RETURN 15c: next = RETURN_5c;

RETURN 10c: next = IDLE;

RETURN 5c: next = IDLE;

default: next = IDLE;

endcase

end

```

#### **Combinational output assignment**

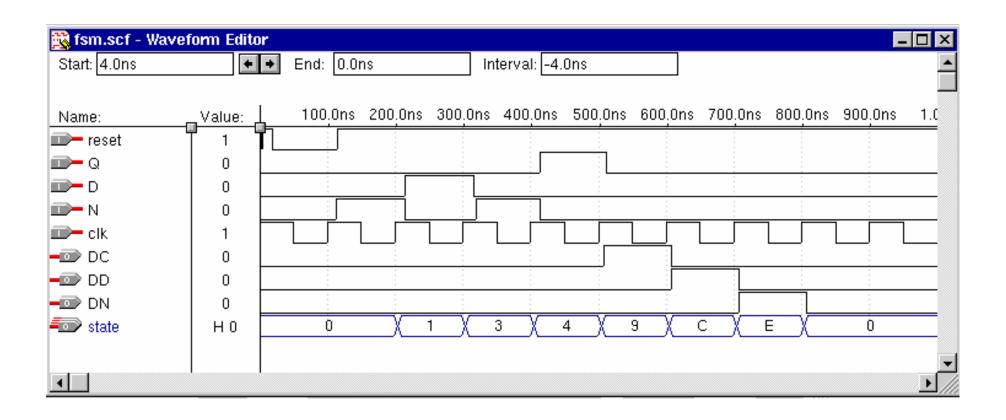

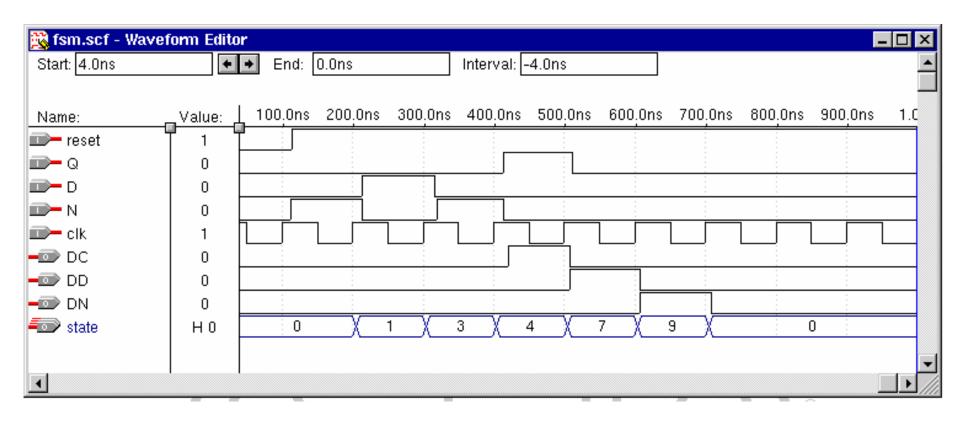

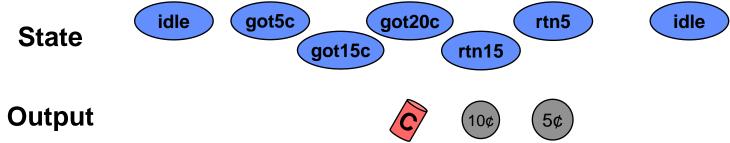

#### Simulation of Moore Vender

#### **Coding Alternative: Two Blocks**

#### Next-state and output logic combined into a single always block

```

always @ (state or N or D or Q) begin

GOT 30c: begin

DC = 0; DD = 0; DN = 0; // defaults

DC = 1; next = IDLE;

end

case (state)

begin

GOT 35c:

if (Q) next = GOT 25c;

IDLE:

DC = 1; next = RETURN 5c;

else if (D) next = GOT 10c;

end

else if (N) next = GOT 5c;

GOT 40c:

begin

else next = IDLE;

DC = 1; next = RETURN 10c;

end

GOT 5c: if (Q) next = GOT 30c;

GOT 45c:

begin

else if (D) next = GOT 15c;

DC = 1; next = RETURN 15c;

else if (N) next = GOT 10c;

end

else next = GOT 5c;

GOT 50c: begin

DC = 1; next = RETURN 20c;

GOT 10c: if (Q) next = GOT 35c;

else if (D) next = GOT 20c;

else if (N) next = GOT 15c;

RETURN 20c: begin

else next = GOT 10c;

DD = 1; next = RETURN 10c;

end

GOT 15c: if (Q) next = GOT 40c;

RETURN 15c: begin

else if (D) next = GOT 25c;

DD = 1; next = RETURN 5c;

else if (N) next = GOT 20c;

end

else next = GOT 15c;

RETURN 10c: begin

DD = 1; next = IDLE;

GOT 20c: if (Q) next = GOT 45c;

end

else if (D) next = GOT 30c;

RETURN 5c:

begin

else if (N) next = GOT 25c;

DN = 1; next = IDLE;

else next = GOT 20c;

end

GOT 25c: if (Q) next = GOT 50c;

default: next = IDLE;

else if (D) next = GOT 35c;

endcase

else if (N) next = GOT 30c;

end

else next = GOT 25c;

```

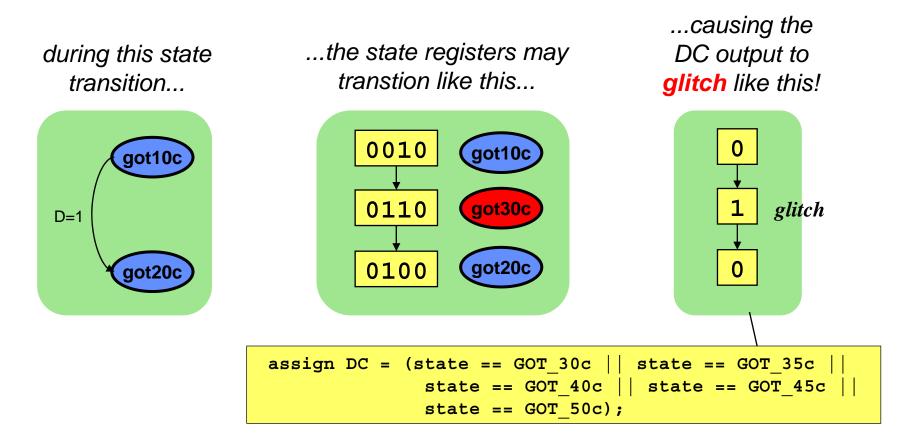

## **FSM Output Glitching**

- FSM state bits may not transition at precisely the same time

- Combinational logic for outputs may contain hazards

- Result: your FSM outputs may glitch!

If the soda dispenser is glitch-sensitive, your customers can get a 20-cent soda!

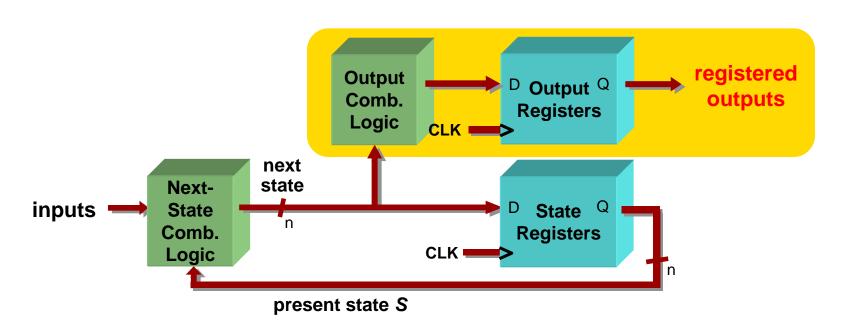

## Registered FSM Outputs are Glitch-Free

- Move output generation into the sequential always block

- Calculate outputs based on <u>next</u> state

## Mealy Vender (covered in Recitation)

## Verilog for Mealy FSM

```

module mealyVender (N, D, Q, DC, DN, DD, clk, reset, state);

input N, D, Q, clk, reset;

output DC, DN, DD;

req DC, DN, DD;

output [3:0] state;

reg [3:0] state, next;

parameter IDLE = 0;

parameter GOT 5c = 1;

parameter GOT 10c = 2;

parameter GOT 15c = 3;

parameter GOT 20c = 4;

parameter GOT 25c = 5;

parameter RETURN 20c = 6;

parameter RETURN 15c = 7;

parameter RETURN 10c = 8;

parameter RETURN 5c = 9;

// Sequential always block for state assignment

always @ (posedge clk or negedge reset)

if (!reset) state <= IDLE;</pre>

else

state <= next;

```

## **Verilog for Mealy FSM**

```

always @ (state or N or D or Q) begin

DC = 0; DN = 0; DD = 0; // defaults

case (state)

IDLE:

if (Q) next = GOT 25c;

else if (D) next = GOT 10c;

else if (N) next = GOT 5c;

else next = IDLE;

GOT 5c:

if (Q) begin

DC = 1; next = IDLE;

end

else if (D) next = GOT 15c;

else if (N) next = GOT 10c;

else next = GOT 5c;

GOT 10c:

if (Q) begin

DC = 1; next = RETURN 5c;

end

else if (D) next = GOT 20c;

else if (N) next = GOT 15c;

else next = GOT 10c;

GOT 15c:

if (Q) begin

DC = 1; next = RETURN 10c;

end

else if (D) next = GOT 25c;

else if (N) next = GOT 20c;

else next = GOT 15c;

GOT 20c:

if (Q) begin

DC = 1; next = RETURN 15c;

end

else if (D) begin

DC = 1; next = IDLE;

end

else if (N) next = GOT 25c;

else next = GOT_20c;

```

# For state GOT\_5c, output DC is only asserted if Q=1

```

GOT 25c:

if (Q) begin

DC = 1; next = RETURN 20c;

end

else if (D) begin

DC = 1; next = RETURN 5c;

end

else if (N) begin

DC = 1; next = IDLE;

end

else next = GOT 25c;

RETURN 20c: begin

DD = 1; next = RETURN 10c;

RETURN 15c: begin

DD = 1; next = RETURN 5c;

RETURN 10c: begin

DD = 1; next = IDLE;

end

RETURN 5c:

begin

DN = 1; next = IDLE;

end

default: next = IDLE;

endcase

end

endmodule

```

## **Simulation of Mealy Vender**

## Clocks are not perfect: Clock Skew

## **Summary**

- Synchronize all asynchronous inputs

- ■Use two back to back registers

- Two types of Finite State Machines introduced

- Moore Outputs are a function of current state

- □ Mealy outputs a function of current state and input

- A standard template can be used for coding FSMs

- Register outputs of combinational logic for critical control signals