# L4: Sequential Building Blocks (Flip-flops, Latches and Registers)

#### **Acknowledgements:**

- ➤ Lecture material adapted from R. Katz, G. Borriello, "Contemporary Logic Design" (second edition), Prentice-Hall/Pearson Education, 2005.

- ➤ Lecture material adapted from J. Rabaey, A. Chandrakasan, B. Nikolic, "Digital Integrated Circuits: A Design Perspective" Copyright 2003 Prentice Hall/Pearson.

- >Lecture notes prepared by Professor Anantha Chandrakasan

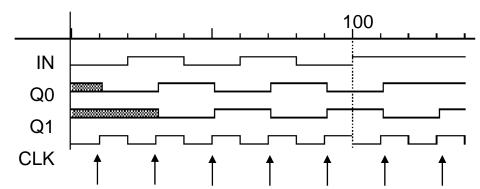

#### **Combinational Logic Review**

- Combinational logic circuits are memoryless

- No feedback in combinational logic circuits

- Output assumes the function implemented by the logic network, assuming that the switching transients have settled

- Outputs can have multiple logical transitions before settling to the correct value

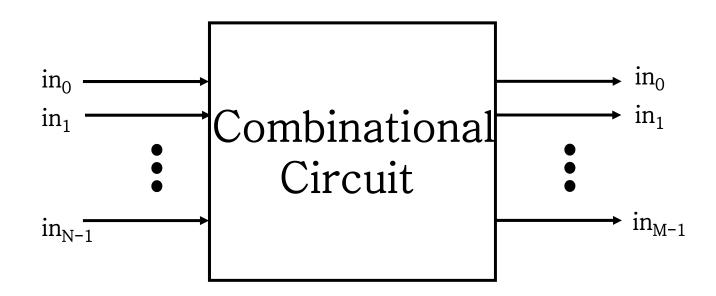

#### **A Sequential System**

- Sequential circuits have memory (i.e., remember the past)

- The current state is "held" in memory and the next state is computed based the current state and the current inputs

- In a synchronous systems, the clock signal orchestrates the sequence of events

#### A Simple Example

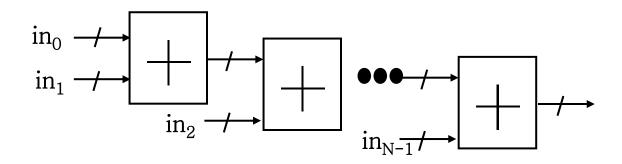

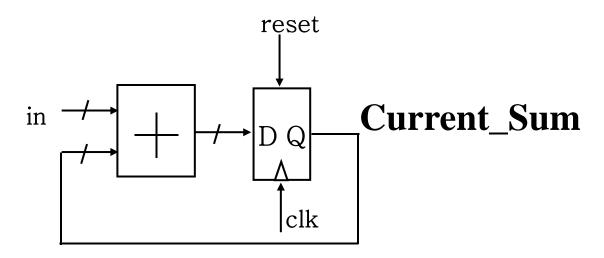

#### Adding N inputs (N-1 Adders)

#### Using a sequential (serial) approach

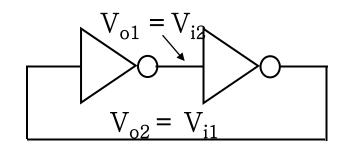

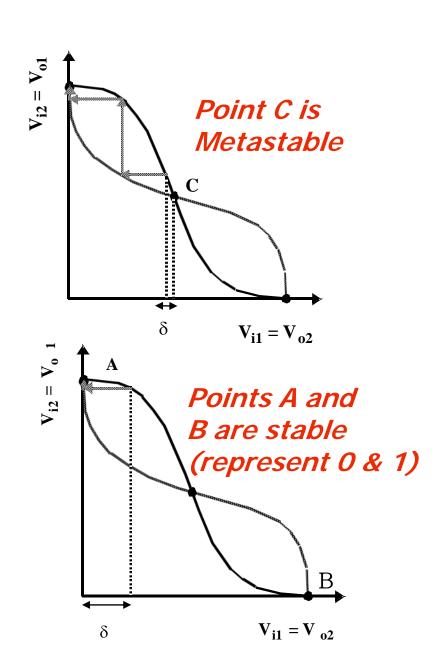

#### Implementing State: Bi-stability

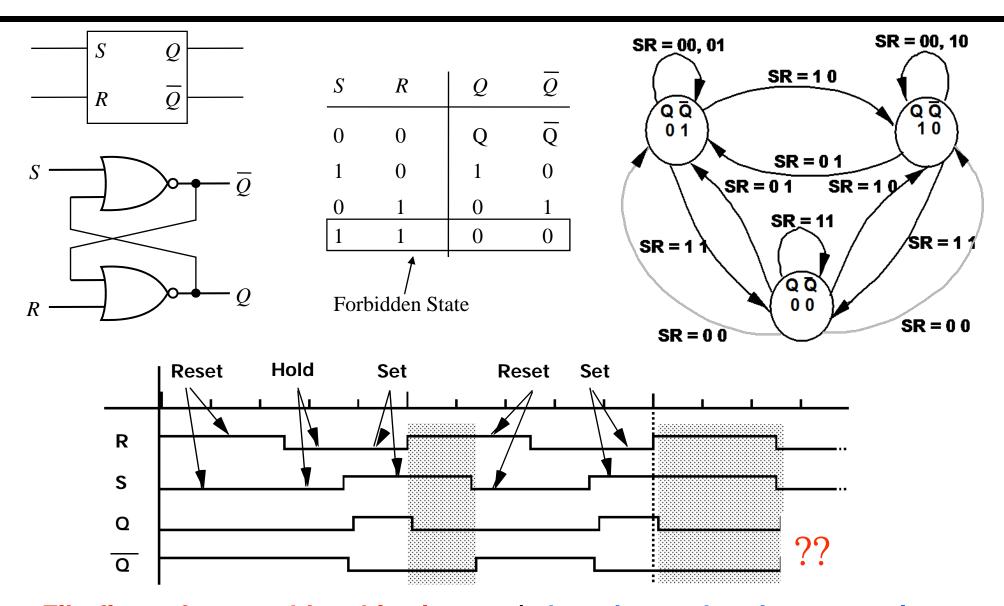

#### NOR-based Set-Reset (SR) Flipflop

Flip-flop refers to a bi-stable element (edge-triggered registers are also called flip-flops) – this circuit is not clocked and outputs change "asynchronously" with the inputs

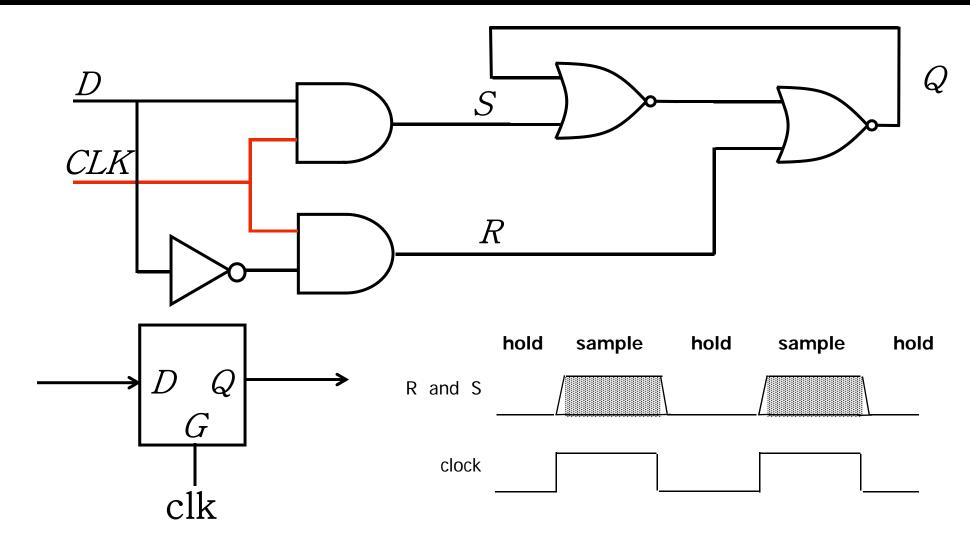

## Making a Clocked Memory Element: Positive D-Latch

- A Positive D-Latch: Passes input D to output Q when CLK is high and holds state when clock is low (i.e., ignores input D)

- A Latch is level-sensitive: invert clock for a negative latch

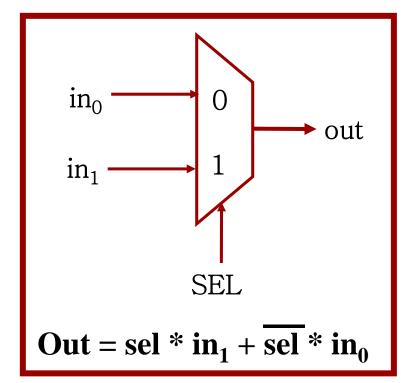

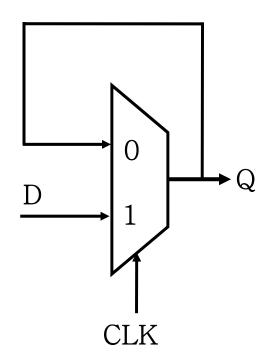

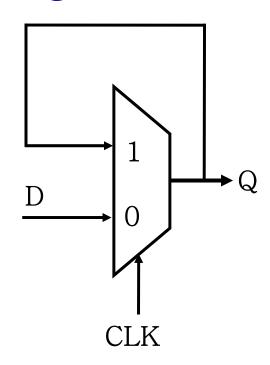

#### **Multiplexer Based Positive & Negative Latch**

#### 2:1 multiplexer

#### **Positive Latch**

#### **Negative Latch**

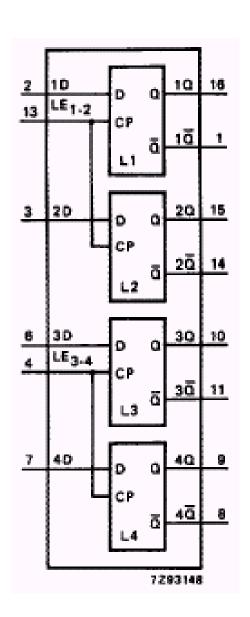

## 74HC75 (Positive Latch)

| OPERATING    | INPUT             | s  | OUTPUTS |     |  |

|--------------|-------------------|----|---------|-----|--|

| MODES        | LE <sub>n-n</sub> | nD | nQ      | nΩ  |  |

| data enabled | H<br>H            | L  | L       | H - |  |

| data latched | L                 | Х  | a       | a a |  |

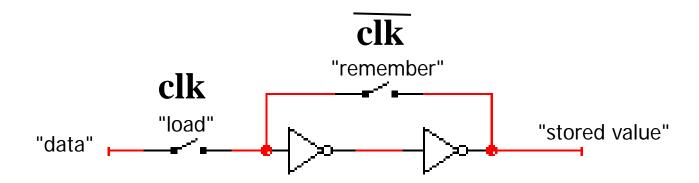

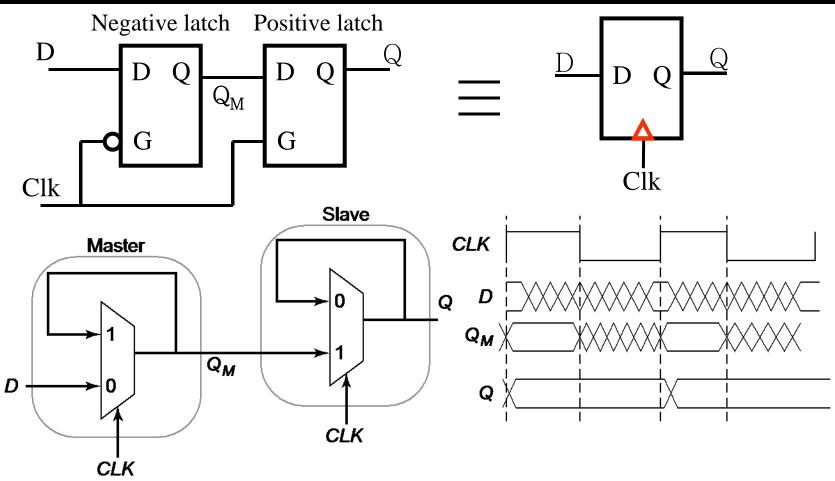

#### **Building an Edge-Triggered Register**

- Master-Slave Register

- Use negative clock phase to latch inputs into first latch

- □ Use positive clock to change outputs with second latch

- View pair as one basic unit

- master-slave flip-flop twice as much logic

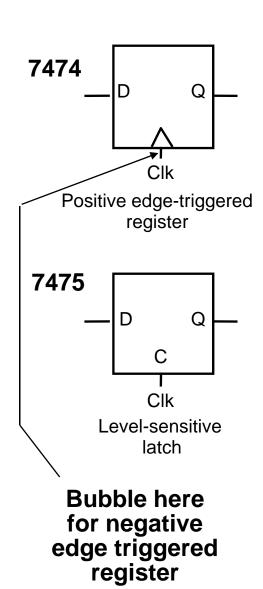

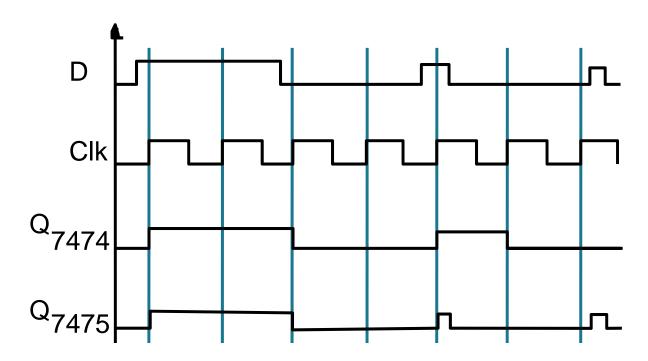

#### Latches vs. Edge-Triggered Register

Edge triggered device sample inputs on the event edge

Transparent latches sample inputs as long as the clock is asserted

**Timing Diagram:**

Behavior the same unless input changes while the clock is high

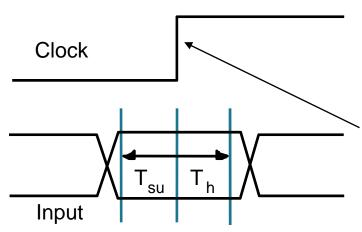

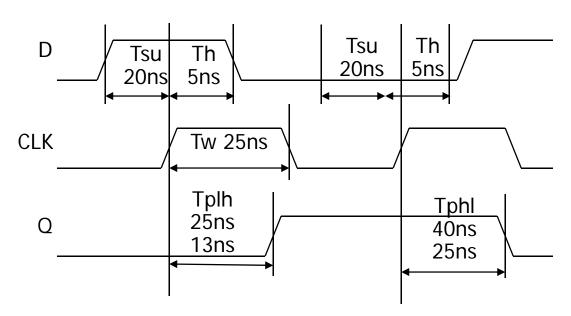

#### **Important Timing Parameters**

#### Clock:

Periodic Event, causes state of memory element to change

memory element can be updated on the: rising edge, falling edge, high level, low level

There is a timing

"window" around the

clocking event

during which the

input must remain

stable and

unchanged in order

to be recognized

Setup Time (T<sub>su</sub>)

Minimum time before the clocking event by which the input must be stable

Hold Time  $(T_h)$

Minimum time after the clocking event during which the input must remain stable

Propagation Delay ( $T_{cq}$  for an edge-triggered register and  $T_{dq}$  for a latch)

Delay overhead of the memory element

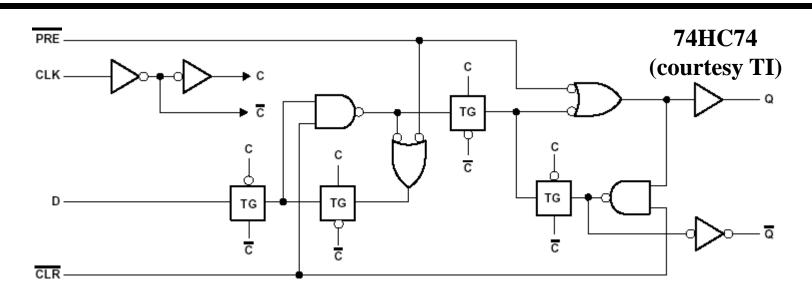

## IIII 74HC74 (Positive Edge-Triggered Register) IIII

#### **FUNCTION TABLE**

| INPUTS |     |            | OUTI | PUTS           |                  |

|--------|-----|------------|------|----------------|------------------|

| PRE    | CLR | CLK        | D    | Q              | ρl               |

| L      | Н   | X          | Х    | Н              | L                |

| н      | L   | X          | X    | L              | н                |

| L      | L   | X          | Χ    | H†             | н†               |

| Н      | Н   | $\uparrow$ | Н    | н              | L                |

| Н      | Н   | $\uparrow$ | L    | L              | Н                |

| Н      | Н   | L          | X    | Q <sub>0</sub> | $\overline{Q}_0$ |

#### **D-FF** with preset and clear

|                                           |                         |                     | V     | T <sub>A</sub> = 25°C |     | SN54HC74 |     | SN74HC74 |     | UNIT |

|-------------------------------------------|-------------------------|---------------------|-------|-----------------------|-----|----------|-----|----------|-----|------|

|                                           |                         |                     | VCC   | MIN                   | MAX | MIN      | MAX | MIN      | MAX | UNII |

|                                           |                         |                     | 2 V   | 0                     | 6   | 0        | 4.2 | 0        | 5   |      |

| f <sub>clock</sub>                        | Clock frequency         |                     | 4.5 V | 0                     | 31  | 0        | 21  | 0        | 25  | MHz  |

|                                           |                         |                     | 6 V   | 0                     | 36  | 0        | 25  | 0        | 29  |      |

|                                           |                         |                     | 2 V   | 100                   |     | 150      |     | 125      |     |      |

|                                           |                         | PRE or CLR low      | 4.5 V | 20                    |     | 30       |     | 25       |     |      |

| ١.                                        | Pulse duration          |                     | 6 V   | 17                    |     | 25       |     | 21       |     | ns   |

| t <sub>W</sub>                            | Pulse duration          | CLK high or low     | 2 V   | 80                    |     | 120      |     | 100      |     |      |

|                                           |                         |                     | 4.5 V | 16                    |     | 24       |     | 20       |     |      |

|                                           |                         |                     | 6 V   | 14                    |     | 20       |     | 17       |     |      |

|                                           |                         | Data                | 2 V   | 100                   |     | 150      |     | 125      |     | ns   |

|                                           |                         |                     | 4.5 V | 20                    |     | 30       |     | 25       |     |      |

|                                           | Saturations before CLKT |                     | 6 V   | 17                    |     | 25       |     | 21       |     |      |

| t <sub>su</sub>                           | Setup time before CLK↑  | PRE or CLR inactive | 2 V   | 25                    |     | 40       |     | 30       |     |      |

|                                           |                         |                     | 4.5 V | 5                     |     | 8        |     | 6        |     |      |

|                                           |                         |                     | 6 V   | 4                     |     | 7        |     | 5        |     |      |

| t <sub>h</sub> Hold time, data after CLK↑ |                         | 2 V                 | 0     |                       | 0   |          | 0   |          |     |      |

|                                           |                         | 4.5 V               | 0     |                       | 0   |          | 0   |          | ns  |      |

|                                           |                         |                     | 6 V   | 0                     |     | 0        |     | 0        |     |      |

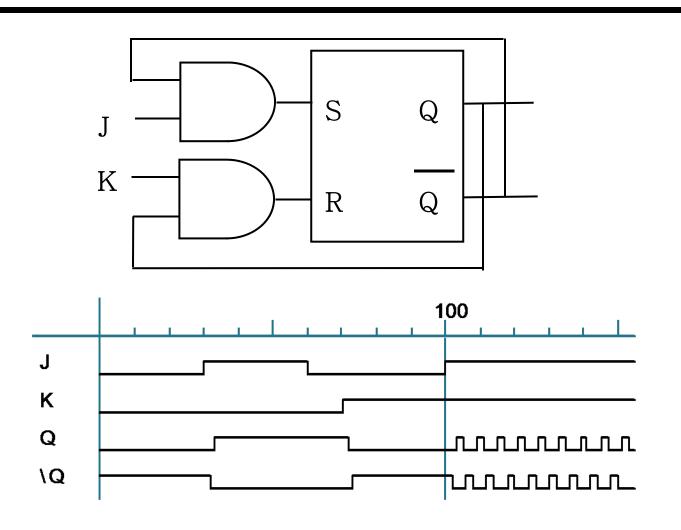

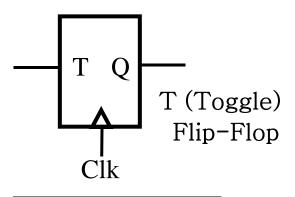

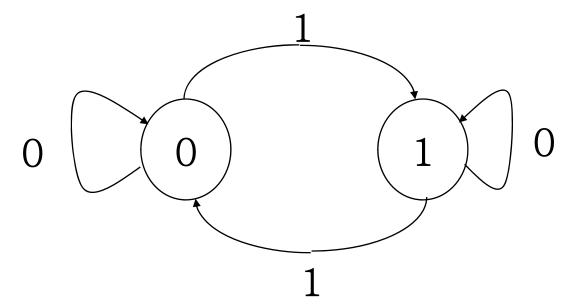

## The J-K Flip-Flop

| J | K | Q+ | Q+ |

|---|---|----|----|

| 0 | 0 | Q  | Q  |

| 0 | 1 | 0  | 1  |

| 1 | 0 | 1  | 0  |

| 1 | 1 | Q  | Q  |

- Eliminate the forbidden state of the SR Flip-flop

- Use output feedback to guarantee that R and S are never both one

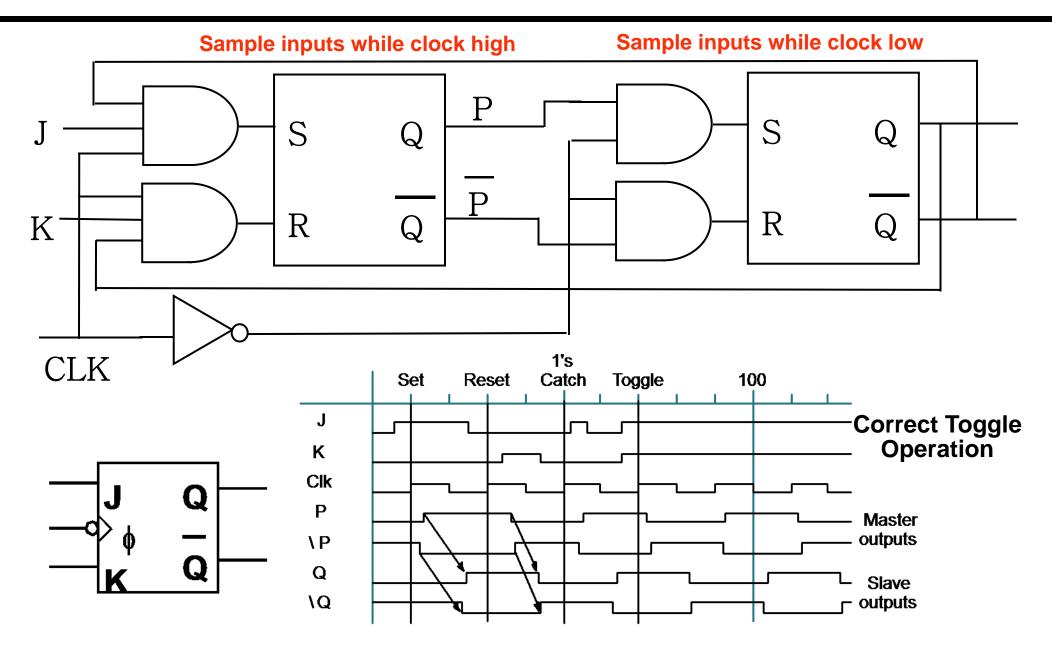

#### J-K Master-Slave Register

Is there a problem with this circuit?

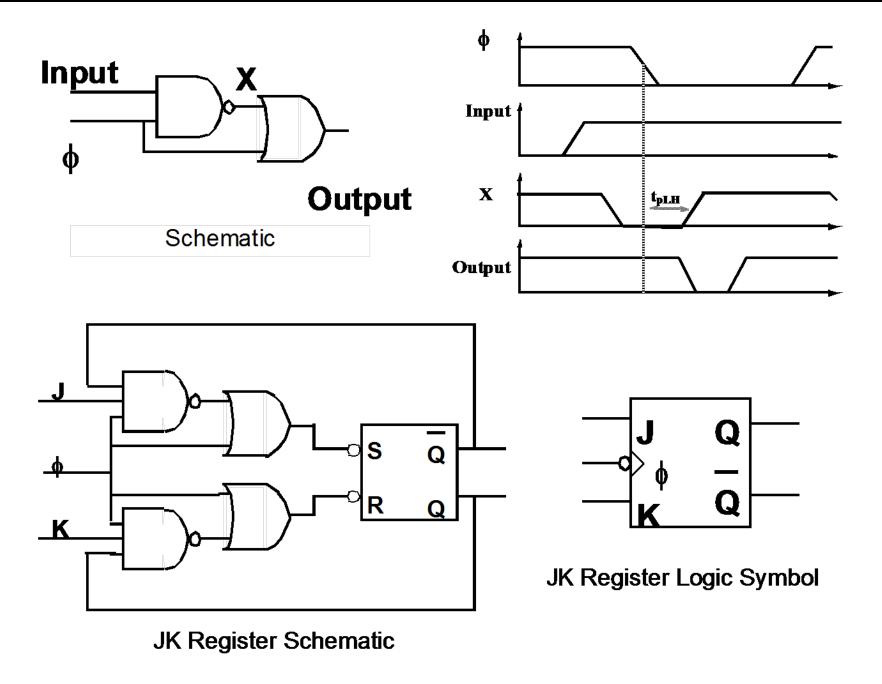

#### Pulse Based Edge-Triggered J-K Register

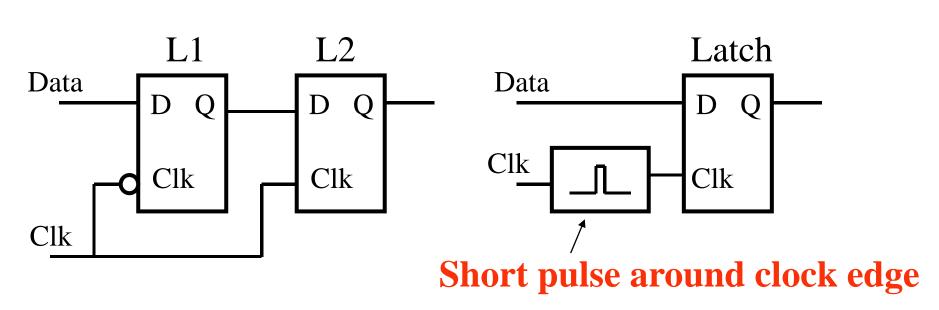

## **Pulse-Triggered Registers**

#### Ways to design an edge-triggered sequential cell:

#### **Master-Slave Latches**

#### **Pulse-Based Register**

- Pulse registers are widely used in high-performance microprocessor chips (Sun Microsystems, AMD, Intel, etc.)

- The can have a negative setup time!

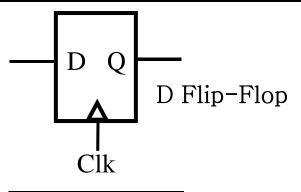

## D Flip-Flop vs. Toggle Flip-Flop

| D | $Q_N$ |

|---|-------|

| 0 | 0     |

| 1 | 1     |

| Т | $Q_N$                         |

|---|-------------------------------|

| 0 | Q <sub>N-1</sub>              |

| 1 | $\overline{\mathbf{Q}}_{N-1}$ |

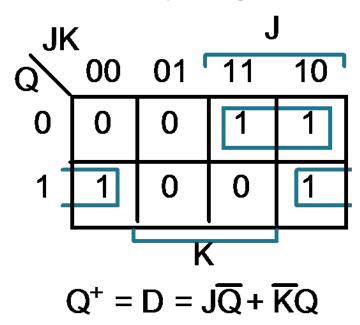

## Realizing Different Types of Memory Elements

#### Characteristic Equations

D:

$$Q+=D$$

J-K:

$$Q+=J\overline{Q}+\overline{K}Q$$

T:

$$Q+=T\overline{Q}+\overline{T}Q$$

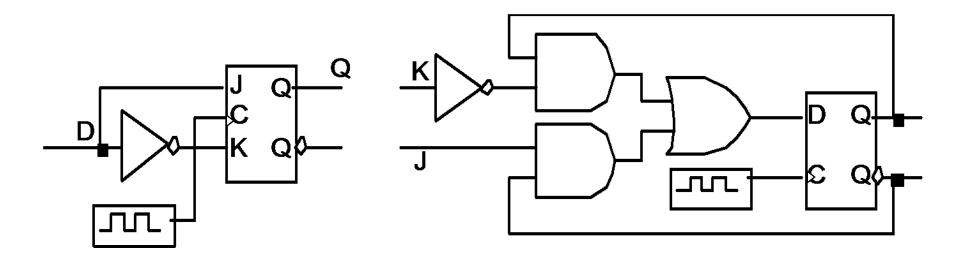

#### Implementing One FF in Terms of Another

D implemented with J-K

J-K implemented with D

## **Design Procedure**

Excitation Tables: What are the necessary inputs to cause a particular kind of change in state?

| Q | Q+ | J                | K | Т | D |

|---|----|------------------|---|---|---|

| 0 | 0  | 0                | X | 0 | 0 |

| 0 | 1  | 1                | X | 1 | 1 |

| 1 | 0  | X                | 1 | 1 | 0 |

| 1 | 1  | 0<br>1<br>X<br>X | 0 | 0 | 1 |

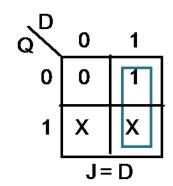

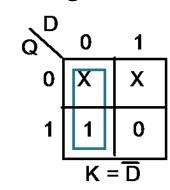

Implementing D FF with a J-K FF:

- 1) Start with K-map of Q+=f(D, Q)

- 2) Create K-maps for J and K with same inputs (D, Q)

- 3) Fill in K-maps with appropriate values for J and K to cause the same state changes as in the original K-map

| o\_D | 0                | 1        |

|------|------------------|----------|

| 0    | 0                | 1        |

| 1    | 0                | 1        |

|      | O <sup>+</sup> : | <u> </u> |

## **Design Procedure (cont.)**

Implementing J-K FF with a D FF:

- 1) K-Map of Q+ = F(J, K, Q)

- 2,3) Revised K-map using D's excitation table its the same! that is why design procedure with D FF is simple!

Resulting equation is the combinational logic input to D to cause same behavior as J-K FF. Of course it is identical to the characteristic equation for a J-K FF.

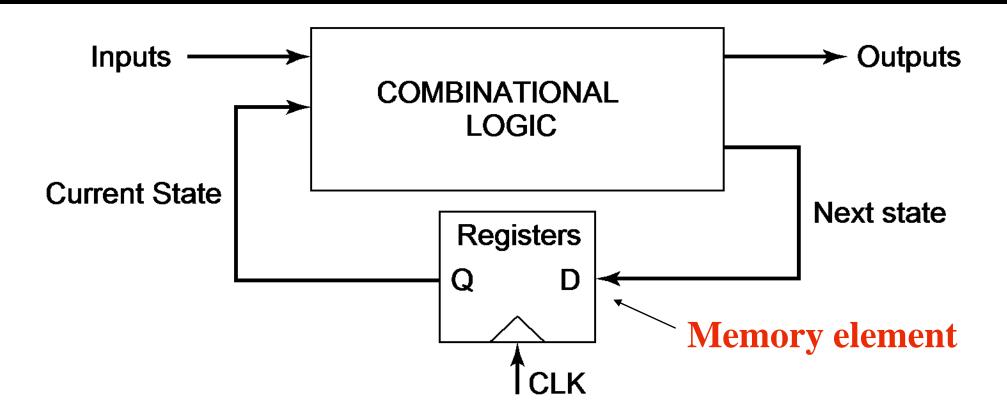

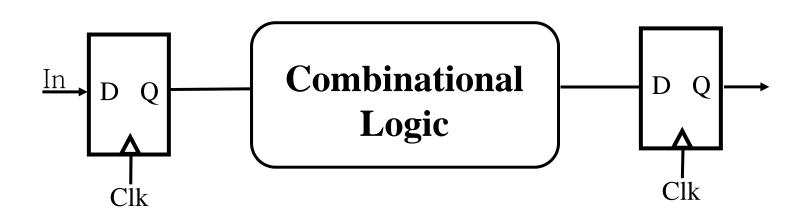

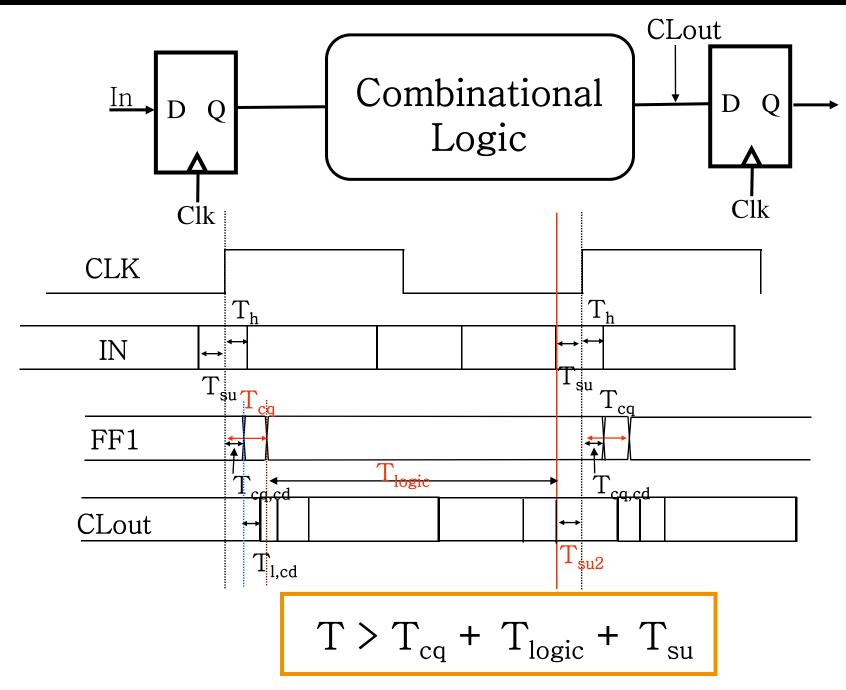

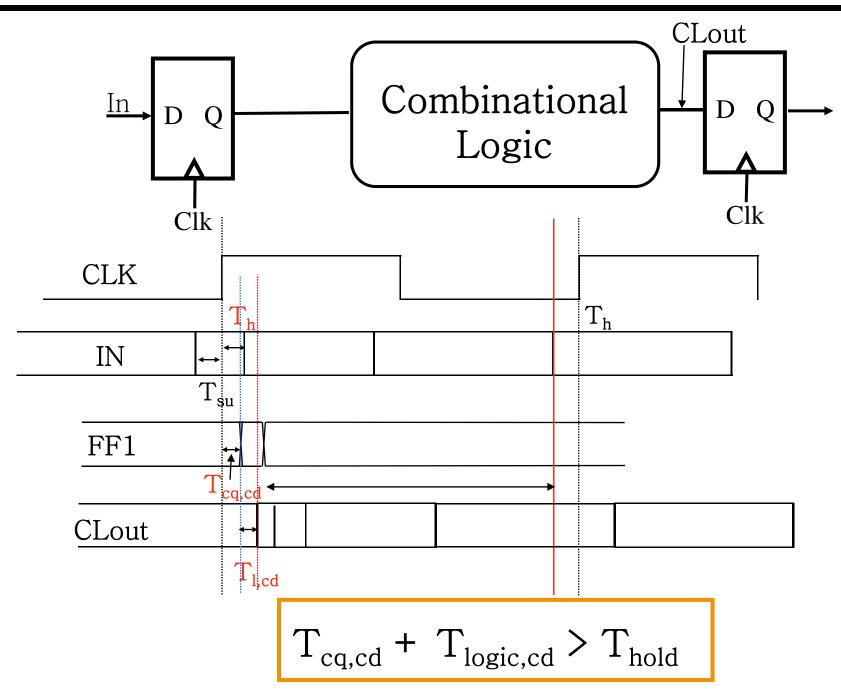

## **System Timing Parameters**

#### **Register Timing Parameters**

#### **Logic Timing Parameters**

T<sub>cq</sub>: worst case rising edge clock to q delay

$T_{cq, cd}$ : contamination or minimum delay from clock to q

T<sub>su</sub>: setup time

$T_h$ : hold time

T<sub>logic</sub>: worst case delay through the combinational logic network

T<sub>logic,cd</sub>: contamination or minimum delay

through logic network

#### System Timing (I): Minimum Period

## **System Timing (II): Minimum Delay**

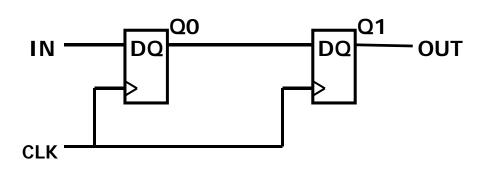

## **Shift-Register**

#### Typical parameters for Positive edge-triggered D Register

all measurements are made from the clocking event that is, the rising edge of the clock

#### Shift-register