May 1998

# **ADC0841**

# 8-Bit µP Compatible A/D Converter

# **General Description**

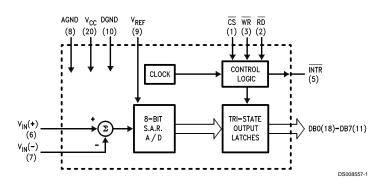

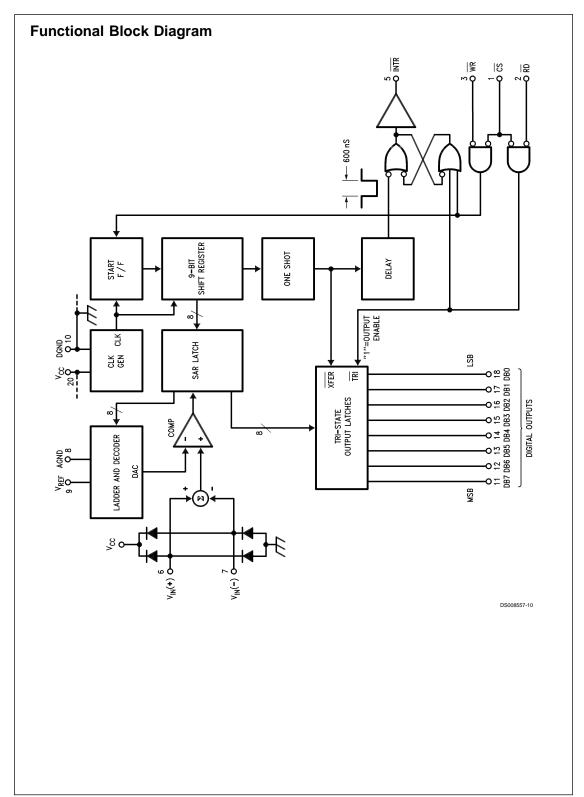

The ADC0841 is a CMOS 8-bit successive approximation A/D converter. Differential inputs provide low frequency input common mode rejection and allow offsetting the analog range of the converter. In addition, the reference input can be adjusted enabling the conversion of reduced analog ranges with 8-bit resolution.

The A/D is designed to operate with the control bus of a variety of microprocessors. TRI-STATE® output latches that directly drive the data bus permit the A/D to be configured as a memory location or I/O device to the microprocessor with no interface logic necessary.

#### **Features**

■ Easy interface to all microprocessors

- Operates ratiometrically or with 5 V<sub>DC</sub> voltage reference

- No zero or full-scale adjust required

- Internal clock

- 0V to 5V input range with single 5V power supply

- 0.3" standard width 20-pin package

- 20 Pin Molded Chip Carrier Package

# **Key Specifications**

- Resolution: 8 Bits

- Total Unadjusted Error: ±½ LSB and ± 1 LSB

- Single Supply: 5 V<sub>DC</sub>

Low Power: 15 mW

Conversion Time: 40 µs

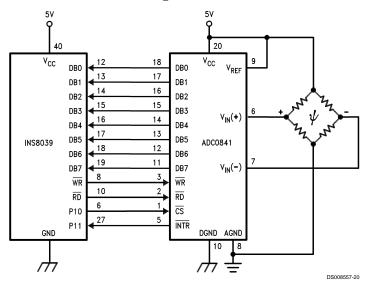

# **Block and Connection Diagrams**

#### **Dual-In-Line Package (N)**

(N.C.-No Connection)

Top View

#### Molded Chip Carrier Package (V)

Top View

TRI-STATE® is a registered trademark of National Semiconductor Corporation. NSC800™ is a trademark of National Semiconductor Corporation.

# **Absolute Maximum Ratings** (Notes 1, 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage (V<sub>CC</sub>) 6.5V

Voltage

-0.3V to  $V_{\rm CC}$ +0.3V Logic Control Inputs At Other Inputs and Outputs -0.3V to  $V_{\rm CC}$ +0.3V

Input Current Per Pin (Note 3) ±5 mA Input Current Per Package (Note 3) ±20 mA -65°C to +150°C Storage Temperature

Package Dissipation at T<sub>A</sub>=25°C 875 mW Lead Temp. (Soldering, 10 seconds) Dual-In-Line Package (Plastic) Molded Chip Carrier Package Vapor Phase (60 seconds) Infrared (15 seconds) ESD Susceptibility (Note 10)

260°C 215°C 220°C 800V

# Operating Conditions (Notes 1, 2)

4.5  $V_{DC}$  to 6.0  $V_{DC}$ Supply Voltage (V<sub>CC</sub>) Temperature Range  $T_{MIN}\!\!\leq\!\!T_{A}\!\!\leq\!\!T_{MAX}$ ADC0841BCN, ADC0841CCN  $0^{\circ}C \le T_A \le 70^{\circ}C$ –40°C≤T<sub>A</sub>≤85°C ADC0841BCV, ADC0841CCV

## **Electrical Characteristics**

The following specifications apply for  $V_{CC}$ =5  $V_{DC}$  unless otherwise specified. Boldface limits apply from  $T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A$ = $T_j$ =25°C.

|                          |                                        | ADC<br>ADC |                       |                       |       |

|--------------------------|----------------------------------------|------------|-----------------------|-----------------------|-------|

| Parameter                | Conditions                             | Тур        | Tested                | Design                | Units |

|                          |                                        | (Note 6)   | Limit                 | Limit                 |       |

|                          |                                        |            | (Note 7)              | (Note 8)              |       |

| CONVERTER AND MULTIPLEXE | R CHARACTERISTICS                      |            |                       | •                     |       |

| Maximum Total            | V <sub>REF</sub> =5.00 V <sub>DC</sub> |            |                       |                       |       |

| Unadjusted Error         | (Note 4)                               |            |                       |                       |       |

| ADC0841BCN, BCV          |                                        |            | ±1/2                  | ±1/2                  | LSB   |

| ADC0841CCN, CCV          |                                        |            | ±1                    | ±1                    | LSB   |

| Minimum Reference        |                                        | 2.4        | 1.2                   | 1.1                   | kΩ    |

| Input Resistance         |                                        |            |                       |                       |       |

| Maximum Reference        |                                        | 2.4        | 5.4                   | 5.9                   | kΩ    |

| Input Resistance         |                                        |            |                       |                       |       |

| Maximum Common-Mode      | (Note 5)                               |            | V <sub>CC</sub> +0.05 | V <sub>cc</sub> +0.05 | V     |

| Input Voltage            |                                        |            |                       |                       |       |

| Minimum Common-Mode      | (Note 5)                               |            | GND-0.05              | GND-0.05              | V     |

| Input Voltage            |                                        |            |                       |                       |       |

| DC Common-Mode Error     | Differential Mode                      | ±1/16      | ±1/4                  | ±1/4                  | LSB   |

| Power Supply Sensitivity | V <sub>CC</sub> =5V±5%                 | ±1/16      | ±1/8                  | ±1/8                  | LSB   |

## **Electrical Characteristics**

The following specifications apply for  $V_{CC}$ =5  $V_{DC}$  unless otherwise specified. **Boldface limits apply from T<sub>MIN</sub> to T<sub>MAX</sub>**; all other limits  $T_A$ = $T_j$ =25  $^{\circ}$ C.

|                    |                                    |                        | ADC0841BCN, ADC0841CCN<br>ADC0841BCV, ADC0841CCV |                       |                             |       |

|--------------------|------------------------------------|------------------------|--------------------------------------------------|-----------------------|-----------------------------|-------|

| Symbol             | Parameter                          | Conditions             | Typ<br>(Note 6)                                  | Tested Limit (Note 7) | Design<br>Limit<br>(Note 8) | Units |

| DIGITAL AI         | ND DC CHARACTERISTIC               | s                      |                                                  |                       |                             |       |

| V <sub>IN(1)</sub> | Logical "1" Input<br>Voltage (Min) | V <sub>CC</sub> =5.25V |                                                  | 2.0                   | 2.0                         | V     |

| $V_{IN(0)}$        | Logical "0" Input<br>Voltage (Max) | V <sub>CC</sub> =4.75V |                                                  | 0.8                   | 0.8                         | V     |

| I <sub>IN(1)</sub> | Logical "1" Input<br>Current (Max) | V <sub>IN</sub> =5.0V  | 0.005                                            |                       | 1                           | μА    |

## **Electrical Characteristics** (Continued)

The following specifications apply for  $V_{CC}$ =5  $V_{DC}$  unless otherwise specified. **Boldface limits apply from T<sub>MIN</sub> to T<sub>MAX</sub>**; all other limits  $T_A$ = $T_j$ =25 C.

|                     |                       |                                   | ADC08    |          |          |       |

|---------------------|-----------------------|-----------------------------------|----------|----------|----------|-------|

| Symbol              | Parameter             | Conditions                        | Тур      | Tested   | Design   | Units |

|                     |                       |                                   | (Note 6) | Limit    | Limit    |       |

|                     |                       |                                   |          | (Note 7) | (Note 8) |       |

| DIGITAL AN          | ND DC CHARACTERISTICS |                                   |          | •        |          | •     |

| I <sub>IN(0)</sub>  | Logical "0" Input     | V <sub>IN</sub> =0V               | -0.005   |          | -1       | μA    |

|                     | Current (Max)         |                                   |          |          |          |       |

| V <sub>OUT(1)</sub> | Logical "1"           | V <sub>CC</sub> =4.75V            |          |          |          |       |

| , ,                 | Output Voltage (Min)  | I <sub>OUT</sub> =-360 μA         |          | 2.8      | 2.4      | V     |

|                     |                       | I <sub>OUT</sub> =-10 μA          |          | 4.6      | 4.5      | V     |

| V <sub>OUT(0)</sub> | Logical "0"           | V <sub>CC</sub> =4.75V            |          | 0.34     | 0.4      | V     |

|                     | Output Voltage (Max)  | I <sub>OUT</sub> =1.6 mA          |          |          |          |       |

| I <sub>OUT</sub>    | TRI-STATE Output      | V <sub>OUT</sub> =0V              | -0.01    | -0.3     | -3       | μA    |

|                     | Current (Max)         | V <sub>OUT</sub> =5V              | 0.01     | 0.3      | 3        | μA    |

| I <sub>SOURCE</sub> | Output Source         | V <sub>OUT</sub> =0V              | -14      | -7.5     | -6.5     | mA    |

|                     | Current (Min)         |                                   |          |          |          |       |

| I <sub>SINK</sub>   | Output Sink           | V <sub>OUT</sub> =V <sub>CC</sub> | 16       | 9.0      | 8.0      | mA    |

|                     | Current (Min)         |                                   |          |          |          |       |

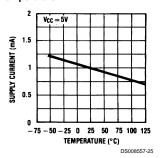

| I <sub>cc</sub>     | Supply Current (Max)  | CS =1, V <sub>REF</sub> Open      | 1        | 2.3      | 2.5      | mA    |

## **AC Characteristics**

The following specifications apply for  $V_{CC}$  = 5 $V_{DC}$ ,  $t_r$  =  $t_f$  = 10 ns unless otherwise specified. **Boldface limits apply from T<sub>MIN</sub> to T<sub>MAX</sub>**; all other limits  $T_A$  =  $T_J$  = 25°C.

|                                   |                                                                                        |                                           |          | Tested   | Design   |       |

|-----------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------|----------|----------|----------|-------|

| Symbol                            | Parameter                                                                              | Conditions                                | Тур      | Limit    | Limit    | Units |

|                                   |                                                                                        |                                           | (Note 6) | (Note 7) | (Note 8) |       |

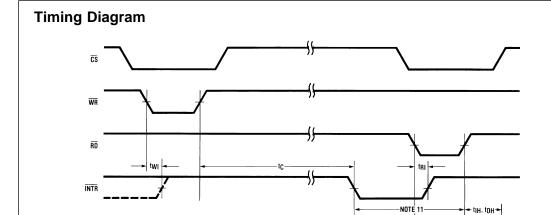

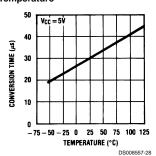

| t <sub>C</sub>                    | Maximum Conversion Time (See Graph)                                                    |                                           | 30       | 40       | 60       | μs    |

| t <sub>W(WR)</sub>                | Minimum WR Pulse Width                                                                 | (Note 9)                                  | 50       | 150      |          | ns    |

| t <sub>ACC</sub>                  | Maximum Access Time (Delay from Falling Edge                                           | C <sub>L</sub> = 100 pF                   | 145      | 225      |          | ns    |

|                                   | of RD to Output Data Valid)                                                            | (Note 9)                                  |          |          |          |       |

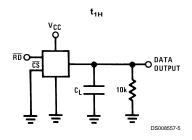

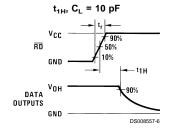

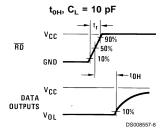

| t <sub>1H</sub> , t <sub>0H</sub> | TRI-STATE Control (Maximum Delay from Rising                                           | $C_L = 10 \text{ pF}, R_L = 10 \text{k},$ | 125      |          | 200      | ns    |

|                                   | Edge of RD to Hi-Z State)                                                              | t <sub>r</sub> = 20 ns (Note 9)           |          |          |          |       |

| t <sub>WI</sub> , t <sub>RI</sub> | Maximum Delay from Falling Edge of $\overline{\text{WR}}$ or $\overline{\text{RD}}$ to | (Note 9)                                  | 200      | 400      |          | ns    |

|                                   | Reset of INTR                                                                          |                                           |          |          |          |       |

| C <sub>IN</sub>                   | Capacitance of Logic Inputs                                                            |                                           | 5        |          |          | pF    |

| C <sub>OUT</sub>                  | Capacitance of Logic Outputs                                                           |                                           | 5        |          |          | pF    |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating the device beyond its specified operating conditions.

Note 2: All voltages are measured with respect to the ground pins.

Note 3: During over-voltage conditions (V<sub>IN</sub><0V and V<sub>IN</sub>>V<sub>CC</sub>) the maximum input current at any one pin is ±5 mA. If the current is limited to ±5 mA at all the pins no more than four pins can be in this condition in order to meet the Input Current Per Package (±20 mA) specification.

Note 4: Total unadjusted error includes offset, full-scale, and linearity.

Note 5: For  $V_{IN}$  (-)  $\geq V_{IN}$  (+) the digital output code will be 0000 0000. Two on-chip diodes are tied to each analog input, which will forward-conduct for analog input voltages one diode drop below ground or one diode drop greater than  $V_{CC}$  supply. Be careful during testing at low  $V_{CC}$  levels (4.5V), as high level analog inputs (5V) can cause this input diode to conduct, especially at elevated temperatures, and cause errors for analog inputs near full-scale. The spec allows 50 mV forward bias of either diode. This means that as long as the analog  $V_{IN}$  does not exceed the supply voltage by more than 50 mV, the output code will be correct. To achieve an absolute 0  $V_{DC}$  to 5  $V_{DC}$  input voltage range will therefore require a minimum supply voltage of 4.950  $V_{DC}$  over temperature variations, initial tolerance and loading.

Note 6: Typicals are at 25°C and represent most likely parametric norm.

Note 7: Tested limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 8: Design limits are guaranteed but not 100% production tested. These limits are not used to calculate outgoing quality levels.

Note 9: The temperature coefficient is 0.3% °C.

Note 10: Human body model, 100 pF discharged through 1.5 k $\Omega$  resistor.

Note 11: Read strobe must occur at least 600 ns after the assertion of interrupt to guarantee reset of INTR.

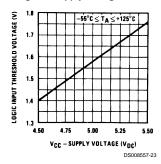

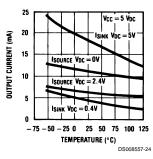

# **Typical Performance Characteristics**

# Logic Input Threshold Voltage vs Supply Voltage

## Output Current vs Temperature

#### Power Supply Current vs Temperature

DBO-DB7

DS008557-9

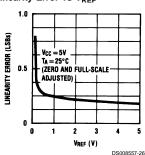

Linearity Error vs V<sub>REF</sub>

Conversion Time vs V<sub>SUPPLY</sub>

Conversion Time vs Temperature

# Typical Performance Characteristics (Continued)

Unadjusted Offset Error vs  $V_{\mathsf{REF}}$  Voltage

# **TRI-STATE Test Circuits and Waveforms**

t<sub>r</sub> = 20 ns

t<sub>r</sub> = 20 ns

VCC VCC VCC DATA DATA OUTPUT

# **Functional Description**

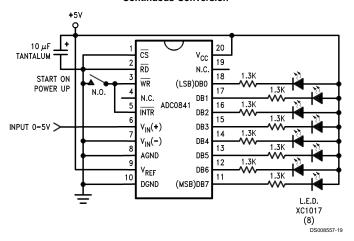

A conversion is initiated via the  $\overline{CS}$  and  $\overline{WR}$  lines. If the data from a previous conversion is not read, the  $\overline{INTR}$  line will be low. The falling edge of  $\overline{WR}$  will reset the  $\overline{INTR}$  line high and ready the A/D for a conversion cycle. The rising edge of  $\overline{WR}$  starts a conversion. After the conversion cycle ( $t_C \le 60$  µsec), which is set by the internal clock frequency, the digital data is transferred to the output latch and the  $\overline{INTR}$  is asserted low. Taking  $\overline{CS}$  and  $\overline{RD}$  low resets  $\overline{INTR}$  output high and transfers the conversion result on the output data lines (DB0–DB7).

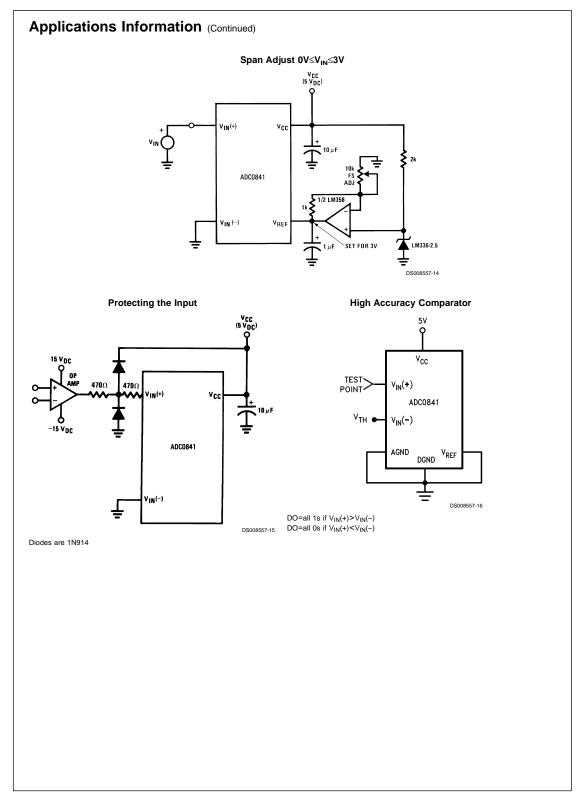

# **Applications Information**

#### 1.0 REFERENCE CONSIDERATIONS

The voltage applied to the reference input of this converter defines the voltage span of the analog input (the difference between  $V_{\mathsf{IN}(\mathsf{MAX})}$  and  $V_{\mathsf{IN}(\mathsf{MIN})}$ ) over which the 256 possible output codes apply. The device can be used in either ratiometric applications or in systems requiring absolute accuracy. The reference pin must be connected to a voltage source capable of driving the minimum reference input resistance of 1.1  $\Omega$ . This pin is the top of a resistor divider string used for the successive approximation conversion.

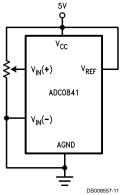

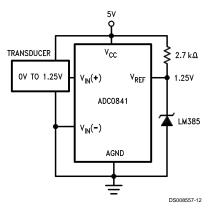

In a ratiometric system (*Figure 1a*), the analog input voltage is proportional to the voltage used for the A/D reference. This voltage is typically the system power supply, so the  $V_{\rm REF}$  pin can be tied to  $V_{\rm CC}.$  This technique relaxes the stability requirements of the system reference as the analog input and A/D reference move together maintaining the same output code for a given input condition.

For absolute accuracy (Figure 1b), where the analog input varies between very specific voltage limits, the reference pin can be biased with a time and temperature stable voltage source. The LM385 and LM336 reference diodes are good low current devices to use with this converter.

The maximum value of the reference is limited to the  $V_{\rm CC}$  supply voltage. The minimum value, however, can be quite small (see Typical Performance Characteristics) to allow direct conversions of transducer outputs providing less than a 5V output span. Particular care must be taken with regard to noise pickup, circuit layout and system error voltage sources when operating with a reduced span due to the increased sensitivity of the converter (1 LSB equals  $V_{\rm RFF}/256$ ).

#### 2.0 THE ANALOG INPUTS

# 2.1 Analog Differential Voltage Inputs and Common-Mode Rejection

The differential inputs of this converter actually reduce the effects of common-mode input noise, a signal common to both selected "+" and "-" inputs for a conversion (60 Hz is most typical). The time interval between sampling the "+" input and then the "-" input is ½ of a clock period. The change in the common-mode voltage during this short time interval can cause conversion errors. For a sinusoidal common-mode signal this error is:

$$V_{\text{ERROR(MAX)}} = V_{\text{peak}} (2\pi f_{\text{CM}}) \times 0.5 \times \left(\frac{t_{\text{C}}}{8}\right)$$

where  $f_{CM}$  is the frequency of the common-mode signal, Vpeak is its peak voltage value and  $t_C$  is the conversion time. For a 60 Hz common-mode signal to generate a ½ LSB error ( $\approx$  5 mV) with the converter running at 40  $\mu$ S, its peak value would have to be 5.43V. This large common-mode signal is

much greater than that generally found in a well designed

data acquisition system.

2.2 Input Current

# Due to the sampling nature of the analog inputs, short duration spikes of current enter the "+" input and exit the "-" input at the clock edges during the actual conversion. These currents decay rapidly and do not cause errors as the internal comparator is strobed at the end of a clock period. Bypass capacitors at the inputs will average these currents and cause an effective DC current to flow through the output resistance of the analog gianal cause. Purpose consciting

cause an effective DC current to flow through the output resistance of the analog signal source. Bypass capacitors should not be used if the source resistance is greater than 1 k $\Omega$ . An op amp RC active low pass filter can provide both impedance buffering and noise filtering should a high impedance signal source be required.

#### 3.0 OPTIONAL ADJUSTMENTS

#### 3.1 Zero Error

The zero of the A/D does not require adjustment. If the minimum analog input voltage value,  $V_{\text{IN}(\text{MIN})},$  is not ground, a zero offset can be done. The converter can be made to output 0000 0000 digital code for this minimum input voltage by biasing the  $V_{\text{IN}}$  (–) input at this  $V_{\text{IN}(\text{MIN})}$  value.

The zero error of the A/D converter relates to the location of the first riser of the transfer function and can be measured by grounding the V $^-$  input and applying a small magnitude positive voltage to the V $^+$  input. Zero error is the difference between actual DC input voltage which is necessary to just cause an output digital code transition from 0000 0000 to 0000 0001 and the ideal ½ LSB value (½ LSB=9.8 mV for  $V_{\rm RFF}{=}5.000~V_{\rm DC}$ ).

#### 3.2 Full-Scale

The full-scale adjustment can be made by applying a differential input voltage which is 1 ½ LSB down from the desired analog full-scale voltage range and then adjusting the magnitude of the  $V_{\rm REF}$  input for a digital output code changing from 1111 1110 to 1111 1111.

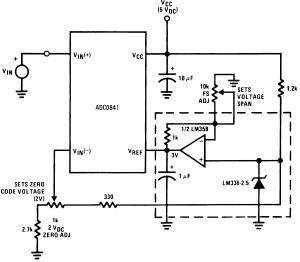

# 3.3 Adjusting for an Arbitrary Analog Input Voltage Range

If the analog zero voltage of the A/D is shifted away from ground (for example, to accommodate an analog input signal which does not go to ground), this new zero reference should be properly adjusted first. A voltage which equals this desired zero reference plus ½ LSB (where the LSB is calculated for the desired analog span, 1 LSB = analog span/256) is applied to the "+" input ( $V_{\rm IN}^{(+)}$ ) and the zero reference voltage at the "-" input ( $V_{\rm IN}^{(-)}$ ) should then be adjusted to just obtain the  $00_{\rm HEX}$  to  $01_{\rm HEX}$  code transition.

a) Ratiometric

b) Absolute with a Reduced Span

FIGURE 1. Referencing Examples

The full-scale adjustment should be made [with the proper  $V_{\rm IN}$  (–) voltage applied] by forcing a voltage to the  $V_{\rm IN}(+)$  input which is given by:

$$V_{IN}$$

(+) fs adj =  $V_{MAX}$  -1.5  $\left[\frac{(V_{MAX} - V_{MIN})}{256}\right]$

where  $V_{MAX}$ =the high end of the analog input range and  $V_{MIN}$ =the low end (the offset zero) of the analog range. (Both are ground referenced.)

The  $V_{REF}$  (or  $V_{CC}$ ) voltage is then adjusted to provide a code change from FE<sub>HEX</sub> to FF<sub>HEX</sub>. This completes the adjustment procedure.

For an example see the Zero-Shift and Span Adjust circuit below.

## Zero Shift and Span Adjust (2V≤V<sub>IN</sub>≤5V)

DS008557-13

## **Continuous Conversion**

## Operating with Automotive Ratiometric Transducers

$^*V_{IN}(-) = 0.15 \ V_{CC}$ 15% of  $V_{CC} \le V_{XDR} \le 85\%$  of  $V_{CC}$

# SAMPLE PROGRAM FOR ADC0841 — INS8039 INTERFACE CONVERTING TWO RATIOMETRIC, DIFFERENTIAL SIGNALS

|      |       |        | ORG  | 0H       |                                 |

|------|-------|--------|------|----------|---------------------------------|

| 0000 | 04 10 |        | JMP  | BEGIN    | ;START PROGRAM AT ADDR 10       |

|      |       |        | ORG  | 10H      | ;MAIN PROGRAM                   |

| 0010 | B9 FF | BEGIN: | MOV  | R1,#0FFH | ;LOAD R1 WITH A UNUSED ADDR     |

|      |       |        |      |          | ;LOCATION                       |

| 0012 | B8 20 |        | MOV  | R0,#20H  | ;A/D DATA ADDRESS               |

| 0014 | 89 FF |        | ORL  | P1,#0FFH | ;SET PORT 1 OUTPUTS HIGH        |

| 0016 | 23 00 |        | MOV  | A,00H    | ;LOAD THE ACC WITH 00           |

| 0018 | 14 50 |        | CALL | CONV     | ;CALL THE CONVERSION SUBROUTINE |

;CONTINUE MAIN PROGRAM

;CONVERSION SUBROUTINE

;ENTRY: ACC — A/D MUX DATA

;EXIT: ACC—CONVERTED DATA

|      |       |       | ORG  | 50H      |                                                 |

|------|-------|-------|------|----------|-------------------------------------------------|

| 0050 | 99 FE | CONV: | ANL  | P1,#0FEH | ;CHIP SELECT THE A/D                            |

| 0052 | 91    |       | MOVX | @R1,A    | ;START CONVERSION                               |

| 0053 | 09    | LOOP: | IN   | A,P1     | ;INPUT INTR STATE                               |

| 0054 | 32 53 |       | JB1  | LOOP     | ;IF INTR = 1 GOTO LOOP                          |

| 0056 | 81    |       | MOVX | A,@R1    | ;IF $\overline{\text{INTR}} = 0$ INPUT A/D DATA |

| 0057 | 89 01 |       | ORL  | P1,&01H  | ;CLEAR THE A/D CHIP SELECT                      |

| 0059 | A0    |       | MOV  | @R0,A    | ;STORE THE A/D DATA                             |

| 005A | 83    |       | RET  |          | ;RETURN TO MAIN PROGRAM                         |

## ADC0841\_INS8039 Interface

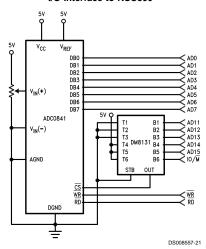

## I/O Interface to NSC800™

## SAMPLE PROGRAM FOR ADC0841 — NSC800 INTERFACE

| 0010  |          | NCONV   | EQU  | 16        | ;TWICE THE NUMBER OF REQUIRED ;CONVERSIONS |

|-------|----------|---------|------|-----------|--------------------------------------------|

| 000F  |          | DEL     | EQU  | 15        | ;DELAY 60 µsec CONVERSION                  |

| 001F  |          | CS      | EQU  | 1FH       | ;THE BOARD ADDRESS                         |

| 3C00  |          | ADDTA   | EQU  | 003CH     | ;START OF RAM FOR A/D                      |

|       |          |         |      |           | ;DATA                                      |

| 0000' | 00       | DTA:    | DB   | 08H       | ;DATA                                      |

| 0001' | 0E 1F    | START:  | LD   | C,CS      |                                            |

| 0003' | 06 16    |         | LD   | B,NCONV   |                                            |

| 0005' | 21 0000' |         | LD   | HL,DTA    |                                            |

| 0008' | 11 003C  |         | LD   | DE,ADDTA  |                                            |

| 000B' | ED A3    | STCONV: | OUTI |           | ;START A CONVERSION                        |

| 000D' | EB       |         | EX   | DE,HL     | ;HL=RAM ADDRESS FOR THE                    |

|       |          |         |      |           | ;A/D DATA                                  |

| 000E' | 3E 0F    |         | LD   | A,DEL     |                                            |

| 0010' | 3D       | WAIT:   | DEC  | Α         | ;WAIT 60 µsec FOR THE                      |

| 0011' | C2 0013' |         | JP   | NZ,WAIT   | ;CONVERSION TO FINISH                      |

| 0014' | ED A2    |         | INI  |           | ;STORE THE A/D'S DATA                      |

|       |          |         |      |           | ;THE REQUIRED CONVERSIONS COMPLETED?       |

| 0016' | EB       |         | EX   | DE,HL     |                                            |

| 0017' | C2 000E' |         | JP   | NZ,STCONV | ;IF NOT GOTO STCONV                        |

|       |          |         |      |           |                                            |

|       |          |         |      |           |                                            |

Note 12: A conversion is started, then a 60 µs wait for the A/D to complete a conversion and the data is stored at address ADDTA for the first conversion, ADDTA + 1 for the second conversion, etc. for a total of 8 conversions.

END

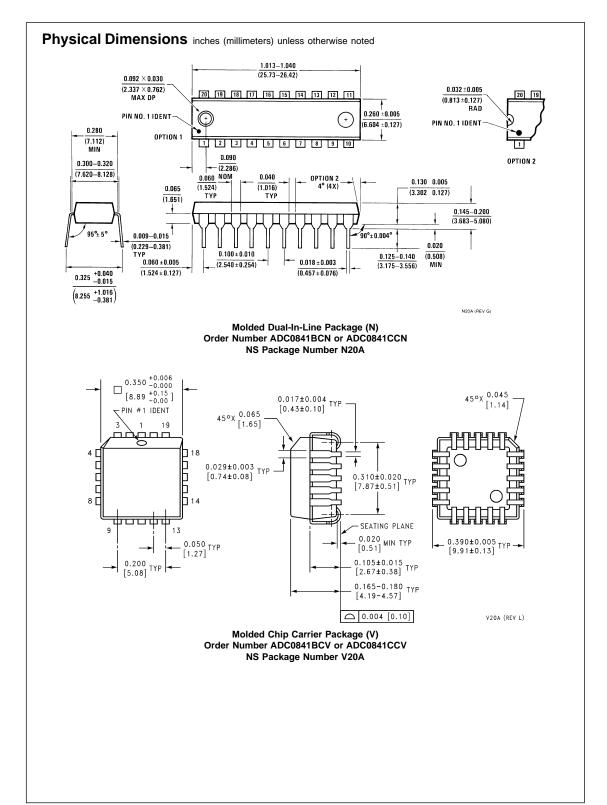

# **Ordering Information**

| Temperature    | Total Unad | usted Error | Package                  |

|----------------|------------|-------------|--------------------------|

| Range          | ±½ LSB     | ±1 LSB      | Outline                  |

| 0°C to +70°C   | ADC0841BCN | ADC0841CCN  | N20A Molded Dip          |

| -40°C to +85°C | ADC0841BCV | ADC0841CCV  | V20A Molded Chip Carrier |

## LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMI-CONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation Americas Tel: 1-800-272-9959

Americas

Tel: 1-800-272-9959

Fax: 1-800-737-7018

Email: support@nsc.com

www.national.com

National Semiconductor Europe

Fax: +49 (0) 1 80-530 85 86

Email: europe.support@nsc.com

Deutsch Tei: +49 (0) 1 80-530 85 85

English Tei: +49 (0) 1 80-532 78 32

Français Tei: +49 (0) 1 80-532 35

Italiano Tei: +49 (0) 1 80-534 16 80

National Semiconductor Asia Pacific Customer Response Group Tel: 65-2544466 Fay: 65-2504466

Tel: 65-2544466 Fax: 65-2504466 Email: sea.support@nsc.com National Semiconductor Japan Ltd. Tel: 81-3-5639-7560 Fax: 81-3-5639-7507