National Semiconductor

## LM18293 Four Channel Push-Pull Driver

## **General Description**

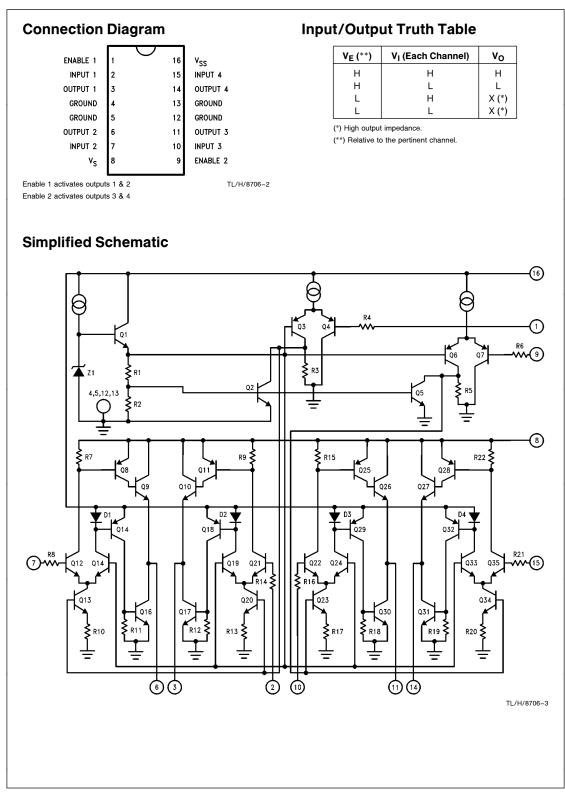

The LM18293 is designed to drive DC loads up to one amp. Typical applications include driving such inductive loads as solenoids, relays and stepper motors along with driving switching power transistors and use as a buffer for low level logic signals. The four inputs accept standard TTL and DTL levels for ease of interfacing. Two enable pins are provided that also accept the standard TTL and DTL levels. Each enable controls 2 channels and when an enable pin is disabled (tied low), the corresponding outputs are forced to the TRI-STATE® condition. If the enable pins are not connected (i.e., floating), the circuit will function as if it has been enabled. Separate pins are provided for the main power supply (pin 8), and the logic supply (pin 16). This allows a lower voltage to be used to bias up the logic resulting in reduced power dissipation. The chip is packaged in a specially designed 16 pin power DIP. The 4 center pins of this package are tied together and form the die paddle inside the package. This provides much better heat sinking capability than most other DIP packages available. The device is capable of operating at voltages up to 36 volts.

## Features

- 1A output current capability per channel

- Pin for pin replacement for L293B

- Special 16 pin power DIP package

- 36 volt operation

- Internal thermal overload protection

- Logical "0" input voltage up to 1.5 volts results in high noise immunity

© 1995 National Semiconductor Corporation

TL/H/8706

March 1995

RRD-B30M115/Printed in U. S. A.

.M18293 Four Channel Push-Pull Driver

<image><image><text><text><text>

| Absolute Maximum Ratings                                                                                                                                             |     |                                                               |               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------|---------------|

| If Military/Aerospace specified devices are required,<br>please contact the National Semiconductor Sales<br>Office/Distributors for availability and specifications. |     | Peak Output Current (Non-Repetitive $t = 5 \text{ ms}$ )      | 2A<br>+ 150°C |

|                                                                                                                                                                      |     | Junction Temperature (T <sub>J</sub> )                        |               |

|                                                                                                                                                                      |     | Thermal Resistance Junction to Case ( $\theta_{JC}$ )         | 14°C/W        |

| Output Drive Supply Voltage (V <sub>S</sub> )                                                                                                                        |     | Thermal Resistance Junction to Ambient ( $\theta_{\perp A}$ ) | 80°C/W        |

| Logic Supply Voltage (V <sub>SS</sub> )                                                                                                                              | 36V | Internal Power Dissipation Intern                             | ally Limited  |

| Input Voltage (V <sub>I</sub> )                                                                                                                                      | 7V  | Operating Temperature Range -40°C                             | to + 125°C    |

| Enable Voltage (V <sub>F</sub> )                                                                                                                                     | 7V  | Storage Temperature Range -65°C                               | to +150°C     |

| 0 ( 2)                                                                                                                                                               |     | Lead Temperature (Solder 10 seconds)                          | 260°C         |

Electrical Characteristics  $V_S$  = 24V,  $V_{SS}$  = 5V, T = 25°C, L = 0.4V, H = 3.5V, each channel, unless otherwise noted

| Symbol                  | Parameter                                           | Conditions                                                                                                                                             | Typical        | Tested Limit<br>(Note 1)                   | Design Limit<br>(Note 2) | Units                                |

|-------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------|--------------------------|--------------------------------------|

| VS                      | Main Supply (Pin 8)                                 | Maximum Supply Voltage                                                                                                                                 |                | 36                                         |                          | Vmax                                 |

| V <sub>SS</sub>         | Logic Supply (Pin 16)                               | Minimum Logic Supply Voltage<br>Maximum Logic Supply Voltage                                                                                           |                | 4.5<br>36                                  |                          | Vmin<br>Vmax                         |

| I <sub>S</sub>          | Total Quiescent<br>Supply Current                   | $ \begin{array}{lll} V_I = L & I_O = 0 & V_E = H \\ V_I = H & I_O = 0 & V_E = H \\ & & V_E = L \end{array} $                                           | 2<br>16        | 6<br>24<br>4                               |                          | mAmax<br>mAmax<br>mAmax              |

| I <sub>SS</sub>         | Total Quiescent Logic<br>Supply Current<br>(pin 16) | $ \begin{array}{ccc} V_I = L & I_O = 0 & V_E = H \\ V_I = H & I_O = 0 & V_E = H \\ & & V_E = L \end{array} $                                           | 44<br>16<br>16 | 60<br>22<br>24                             |                          | mAmax<br>mAmax<br>mAmax              |

| VI                      | Input Voltage                                       | Min Value of Low Max Value of Low Min Value of High Max Value of High (V <sub>SS</sub> $\leq$ 7) Max Value of High (V <sub>SS</sub> $>$ 7)             |                | -0.3<br>1.5<br>2.3<br>V <sub>SS</sub><br>7 |                          | Vmin<br>Vmax<br>Vmin<br>Vmax<br>Vmax |

| lı                      | Input Current                                       | $V_{I} = L$<br>$V_{I} = H$                                                                                                                             | 30             | 10<br>100                                  |                          | μAmax<br>μAmax                       |

| V <sub>E</sub>          | Enable Voltage<br>(Pins 1, 9)                       | Min Value of Low<br>Max Value of Low<br>Min Value of High<br>Max Value of High (V <sub>SS</sub> $\leq$ 7)<br>Max Value of High (V <sub>SS</sub> $>$ 7) |                | -0.3<br>1.5<br>2.3<br>V <sub>SS</sub><br>7 |                          | Vmin<br>Vmax<br>Vmin<br>Vmax<br>Vmax |

| ΙE                      | Enable Current                                      | $V_E = L$<br>$V_E = H$                                                                                                                                 | -30            | − 100<br>±10                               |                          | μAmax<br>μAmax                       |

| V <sub>CE</sub> sat Top | Source Saturation<br>Voltage                        | $I_0 = -1 \text{ amp}$                                                                                                                                 | 1.4            | 1.8                                        |                          | Vmax                                 |

| $V_{CE}$ sat Bottom     | Sink Saturation<br>Voltage                          | I <sub>o</sub> = 1 amp                                                                                                                                 | 1.2            | 1.8                                        |                          | Vmax                                 |

| t <sub>r</sub>          | Rise Time                                           | 10%–90% V <sub>o</sub>                                                                                                                                 | 250            |                                            |                          | ns                                   |

| t <sub>f</sub>          | Fall Time                                           | 90%–10% V <sub>o</sub>                                                                                                                                 | 250            |                                            |                          | ns                                   |

| t <sub>on</sub>         | Turn-On Delay                                       | 50% V <sub>I</sub> to 50% V <sub>o</sub>                                                                                                               | 450            |                                            |                          | ns                                   |

| t <sub>off</sub>        | Turn-Off Delay                                      | 50% V <sub>I</sub> to 50% V <sub>o</sub>                                                                                                               | 200            |                                            |                          | ns                                   |

Note 1: Tested limits are guaranteed and 100% production tested.

Note 2: Design limits are guaranteed (but not 100% production tested) over the full supply and temperature range. These limits are not used to calculate outgoing quality levels.