# Shared Memory Architectures

# Programming and Synchronization

Discuss paper on

Cosmic Cube (message passing)

6.173 Fall 2010

. 1 .

Agarwal

### Today's Outline

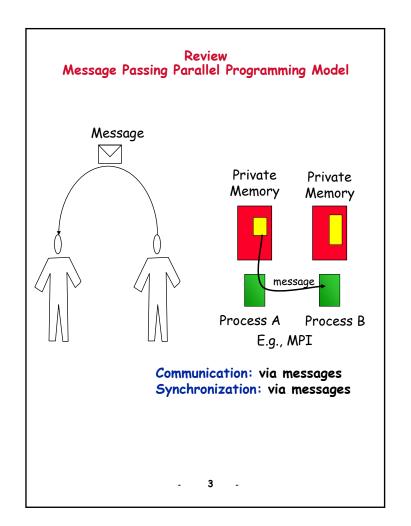

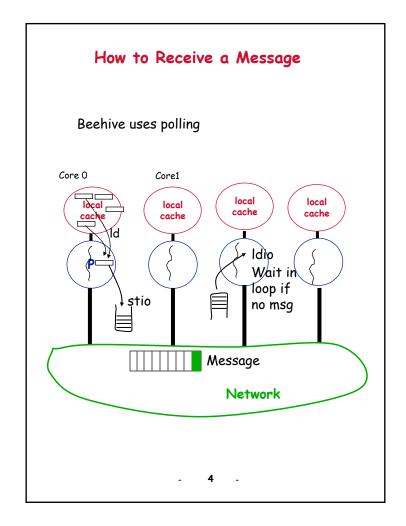

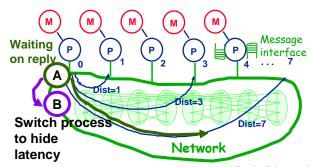

- Message passing review

- Cosmic Cube discussion

- > Message passing machine

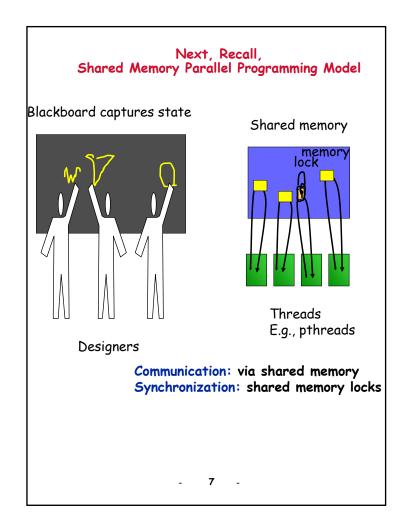

- Shared memory model

- > Communication

- > Synchronization

- Ultracomputer/RP3 discussion

- > Shared memory machine

- Shared memory programming

- Fine grain versus coarse grain parallelism

- How do caches change things

- > Improve and complicate!

- > Beehive

- 2 -

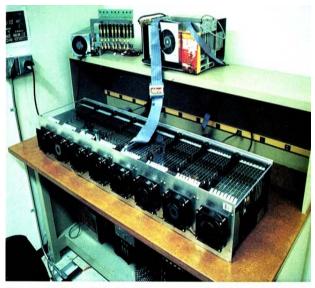

# The Cosmic Cube The Earliest Message Passing Machine

The nodes are packaged as one circuit board per node in the long card frame on the bench top. The six communication channels from each node are wired in a binary 6-cube on the backplane on the underside of the card frame. The separate

units on the shelf above the long 6-cube box are the power supply and an "intermediate host" (iH) that connects through a communication channel to node 0 in the cube.

FIGURE 6. The 64-Node Cosmic Cube in Operation

- 5

#### The Cosmic Cube

64 "nodes" (remember, multicores – on single chip – arrived circa 2000)

- · Direct network hypercube (details later in course)

- Private memories

- Message sends by calling into OS

- · Routing in software

- Sequential programming on each processor & message send/receive (much like Beehive)

- Hide comm latency by switching processes

- · Simple hardware

### Discuss paper

6

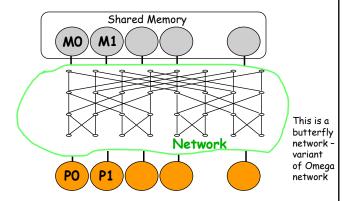

## Ultracomputer Design

- Indirect network Omega network (details later in course)

- · Shared memory machine

- · Communication/synchronization through shared memory

- · Hardware routing of memory requests

- · No latency hiding wait for memory request

Concept built as IBM RP3 machine (we will see this later)

- 8 -

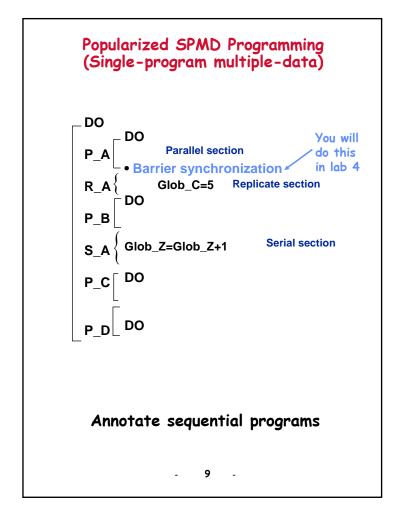

### SPMD Programming Approach Single Program Multiple Data

#### You should learn this!

Most parallel programs written for commodity multicores use this style (all commodity multicores happen to be shared memory machines!)\*

All processors run a copy of the same program (commonly a slightly modified version of the sequential program)

Processor-specific behavior created using unique processor IDs

Also need to introduce synchronization as necessary

Let's do a simple example to build intuition

\*Note that, in general, SPMD style of programming can be applied to either shared memory or message passing machines

- 11 -

### Adding a Pair of Vectors -A Sequential Program

Sequential addition of two vectors

- 12 -

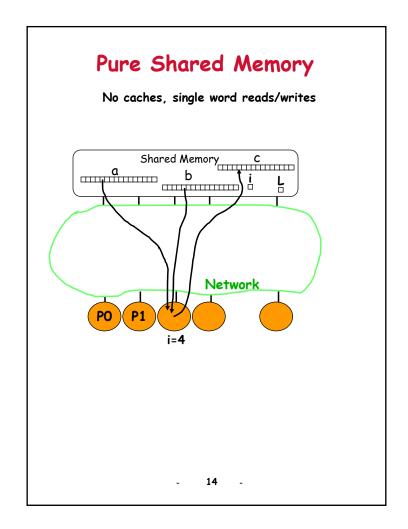

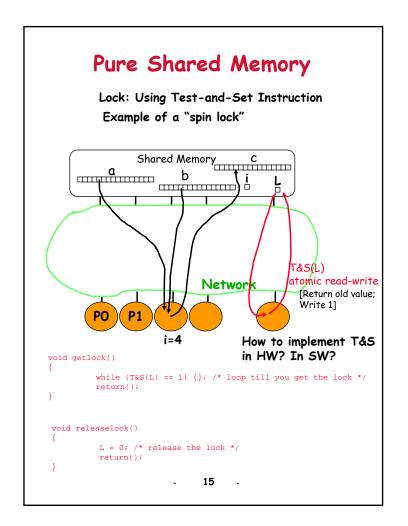

#### Parallel SPMD Version Assume Ultracomputer model. Assume no caches, single word memory access # define LENGTH 1000000 int a[LENGTH], b[LENGTH], c[LENGTH]; int i=0; int L=0;main() /\* create parallel processes \*/ Assume each process /\* Initializations \*/ runs the rest of the if (myPId == 0) .... same program /\* read in the two vectors \*/ Only process 0 if (myPID == 0) . . . runs this int myi; myi = getwork(); Get an index on while (i < LENGTH) which to work. c[myi] = a[myi] + b[myi]; Example of self myi = getwork(); scheduling /\* output the answer \*/ if (myPID == 0) int getwork() getlock(); i = i + 1; /\* increment is atomic \*/ releaselock(); return(i); Sequential addition of two vectors 13

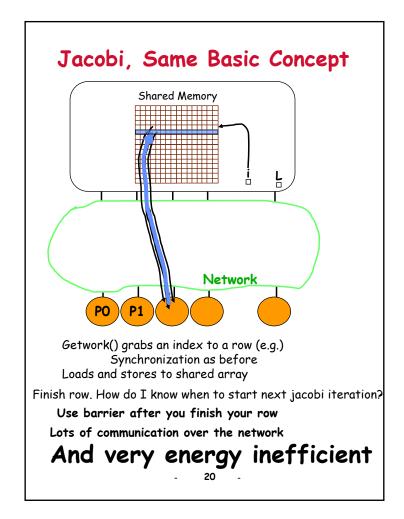

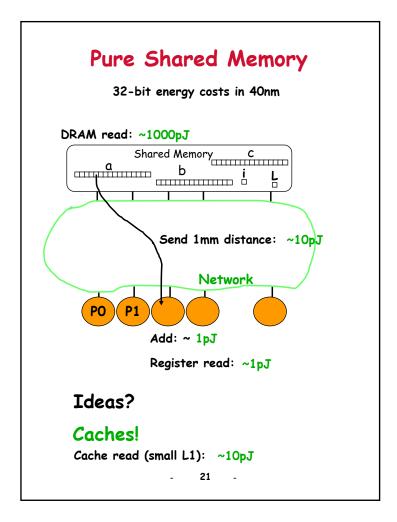

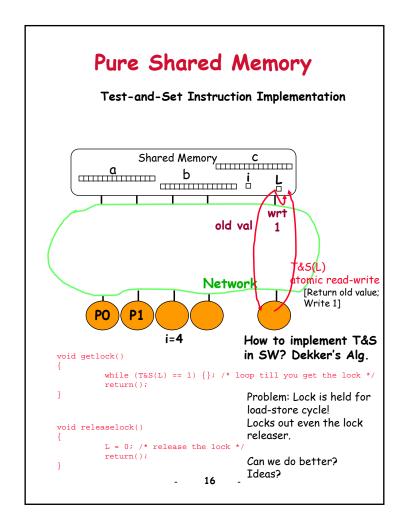

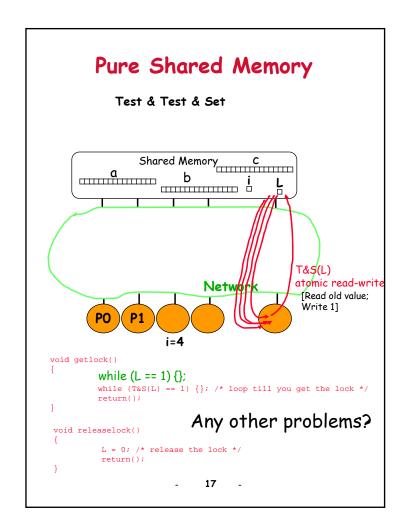

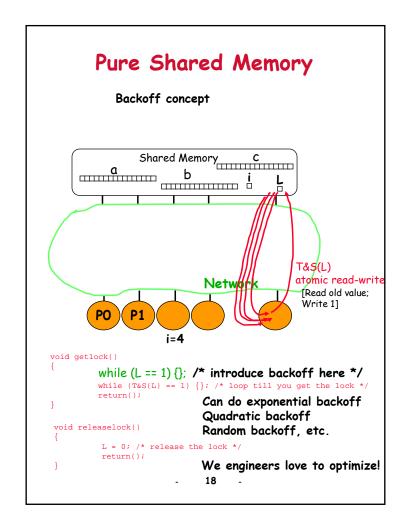

## Pure Shared Memory

So, getting a work item is not so cheap after all, is it? Any ideas?

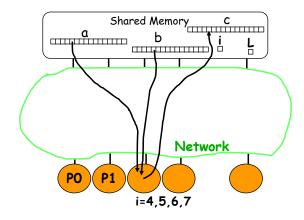

Coarse grain parallelism (versus fine grain parallelism): Get a block of 4 or 16 or more indices each time to amortize the overhead of locking

- 19 -