### Shared Memory Architectures

Software coherence Fences Intro to hardware coherence

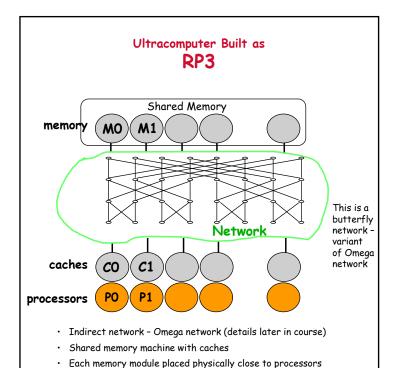

Discuss paper on RP3

6.173 Fall 2010

. 1 .

Agarwal

### Today's Outline

- RP3 discussion

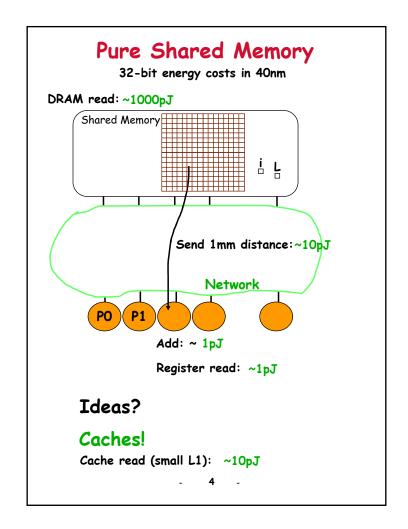

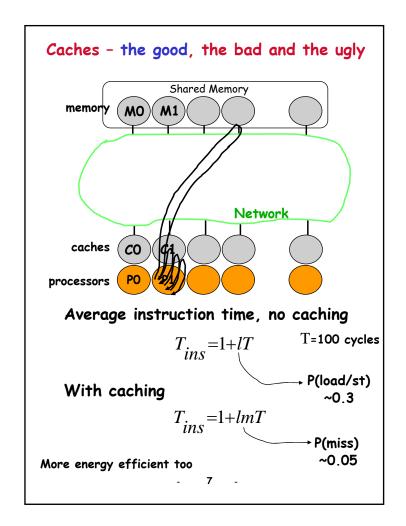

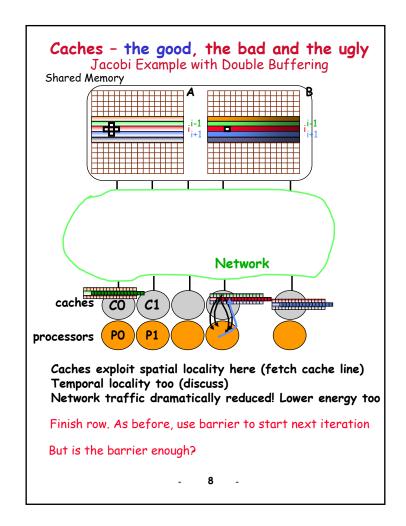

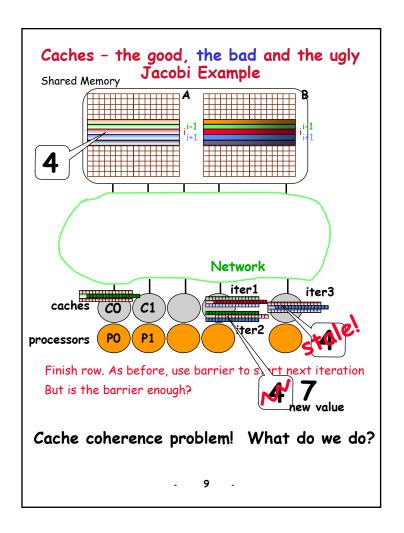

- How do caches change things

- Shared memory programming with caches

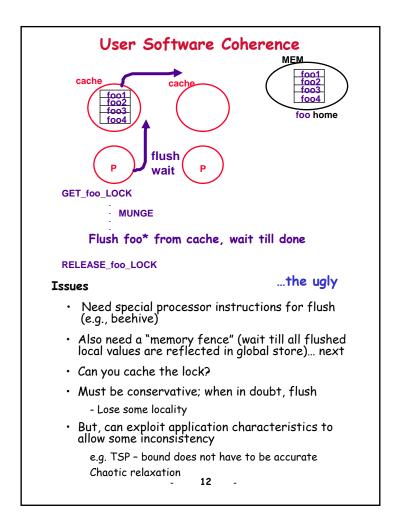

- Software coherence

- The meaning of shared memory  $% \left\{ \left( 1\right) \right\} =\left\{ \left( 1\right)$

- Hardware cache coherence

. 2 .

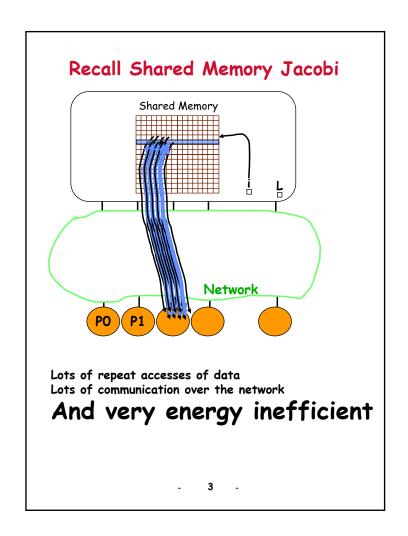

· Communication/synchronization through shared memory

SPMD FORTRAN programming (single program multiple data)

What were the

big ideas?

· Hardware routing of memory requests

• I could not find a picture of the RP3

· More complex hardware

· No latency hiding - wait for memory request

### Trivia Question

Cosmic Cube - Chuck Seitz (Prof. Caltech)

RP3 - Greg Pfister (IBM, Yorktown, NY)

Ultracomputer - Allan Gottlieb (Prof. NYU)

#### These inventors have this in common:

- (a) None finished their Bachelor's degrees

- (b) They were all Geminis

- (c) None of them is retired even today

- (d) They are all Yankees fans

- (e) None of the above

- 6 .

# Maintaining coherence in manycores Major approaches

- · User-software managed coherence

- RP3

- Beehive

- · System-software managed coherence

- Hardware managed coherence (next week)

- 10 -

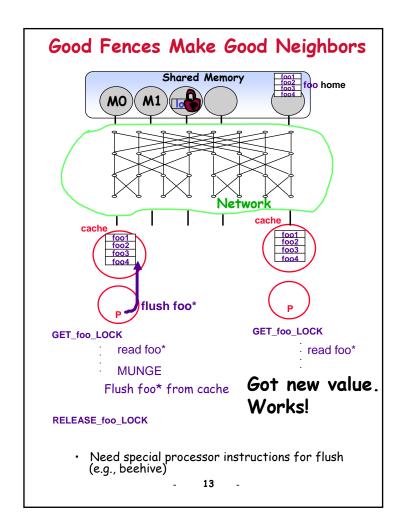

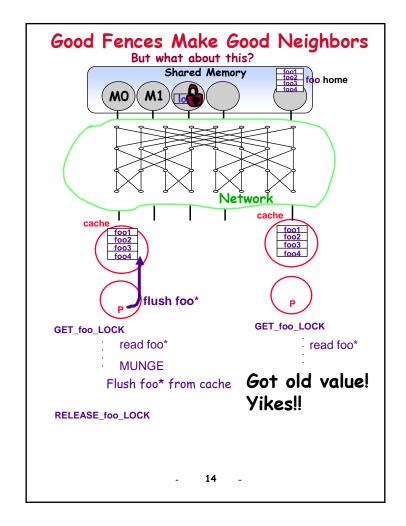

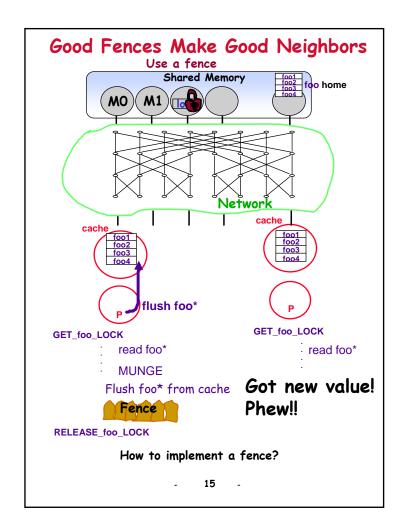

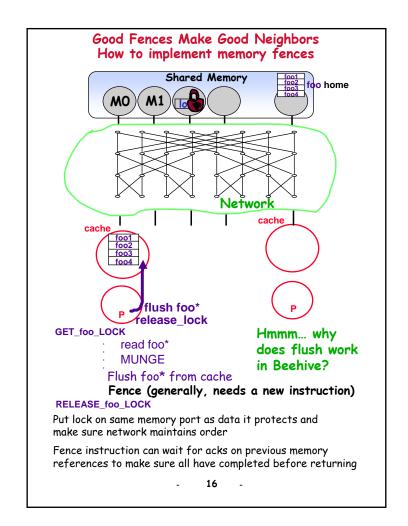

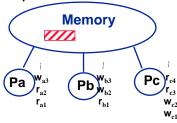

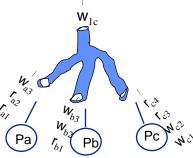

## User-software managed coherence in manycores

Typically yields weak coherence i.e. Coherence at sync points (or fence pts)

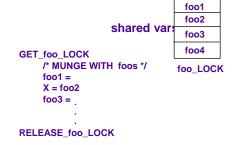

## E.g.: When using locks for shared object accesses

#### Code:

How do you make this work?

- 11 -

#### **Foundations**

What is the meaning of shared memory when you have multiple access ports into global memory?

What if you have caches?

Sequential consistency: Final state (of memory) is as if all RDs and WRTs were executed in some fixed serial order (per processor order also maintained) → Lamport

[This notion borrows from similar notions of sequential consistency in transaction processing systems.]

- 17 -

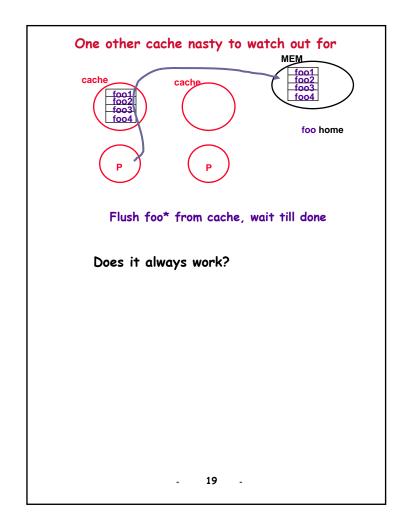

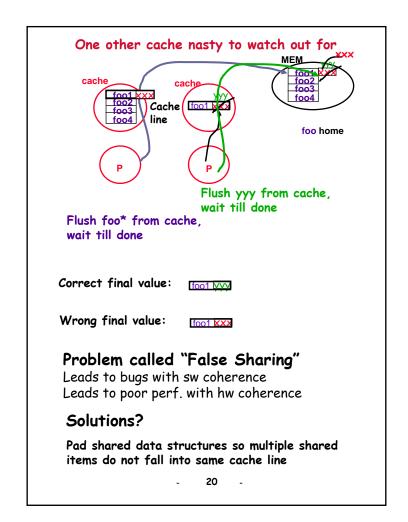

#### **Foundations**

A hardware designers physical perspective of sequential consistency

Key: Using fence to wait until flush is done is the key mechanism that guarantees sequential consistency

We will revisit this in more detail in a couple of weeks

- 18 -

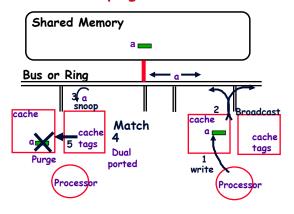

# Hardware Cache Coherence Snooping Caches

- · Works for small multicores (mem off chip)

- · Broadcast address on shared write

- Everyone listens (snoops) on bus/ring to see if any of their own addresses match

- How do you know when to broadcast, invalidate

- State associated with each cache line

- Key benefit: no global state in main mem

- 21 -

### Summary of New Multicore Instructions

- · Send message

- · Receive message

- Synchronization

- Barrier

- Test and set

- F&A and relatives (e.g., F&Op, CmpXch)

- · Flush cache line

- Memory fence

- 22 -