# **17. Formal Concurrency**

In this handout we take a more formal view of concurrency than in handout 14 on practical concurrency. Our goal is to be able to prove that a general concurrent program implements a spec.

We begin with a fairly precise account of the non-atomic semantics of Spec, though our treatment is less formal than the one for atomic semantics in handout 9. Next we explain the general method for making large atomic actions out of small ones (easy concurrency) and prove its correctness. We continue with a number of examples of concurrency, both easy and hard: mutexes, condition variables, read-write locks, buffers, and non-atomic clocks. Finally, we give fairly careful proofs of correctness for some of the examples.

## Non-atomic semantics of Spec

We have already seen that a Spec module is a way of defining an automaton, or state machine, with transitions corresponding to the invocations of external atomic procedures. This view is sufficient if we only have functions and atomic procedures, but when we consider concurrency we need to extend it to include internal transitions. To properly model crashes, we introduced the idea of atomic commands that may not be interrupted. We did this informally, however, and since a crash "kills" any active procedure, we did not have to describe the possible behaviors when two or more procedures are invoked and running concurrently. This section describes the concurrent semantics of Spec.

The most general way to describe a concurrent system is as a collection of independent atomic actions that share a collection of variables. If the actions are A1, ..., An then the entire system is just the 'or' of all these actions: A1 [] ... [] An. In general only some of the actions will be enabled, but for each transition the system non-deterministically chooses an action to execute from all the enabled actions. Thus non-determinism encompasses concurrency.

Usually, however, we find it convenient to carry over into the concurrent world as much of the framework of sequential computing as possible. To this end, we model the computation as a set of *threads* (also called 'tasks' or 'processes'), each of which executes a sequence of atomic actions; we denote threads by variables h, h', etc. To define its sequence, each thread has a state variable called its 'program counter' pc, and each of its actions has the form  $(h, pc = \alpha) => c$ , so that c can only execute when h's program counter equals  $\alpha$ . Different actions have different values for  $\alpha$ , so that at most one action of a thread is enabled at a time. Each action advances the program counter with an assignment of the form  $h, pc := \beta$ , thus enabling the thread's next action.

It's important to understand there is nothing truly fundamental about threads, that is, about organizing the state transitions into sets such that at most one action is enabled in each set. We do so because we can then carry forward much of what we know about sequential computing into the concurrent world. In fact, we want to achieve our performance goals with as little concurrency as possible, since concurrency is confusing and error-prone.

We now explain how to use this view to understand the non-atomic semantics of Spec.

#### Non-atomic commands and threads

Unlike an atomic command, a non-atomic command cannot be described simply as a relation between states and outcomes, that is, an atomic transition. The simple example, given in handout 14, of a non-atomic assignment x := x + 1 executed by two threads should make this clear: the outcome can increase x by 1 or 2, depending on the interleaving of the transitions in the two threads. Rather, a non-atomic command corresponds to a *sequence* of atomic transitions, which may be interleaved with the sequences of other commands executing concurrently. To describe this interleaving, we use *labels* and *program counters*. We also need to distinguish the various *threads* of concurrent computation.

Intuitively, threads represent sequential processes. Roughly speaking, each point in the program between two atomic commands is assigned a label. Each thread's program counter pc takes a label as its value,<sup>1</sup> indicating where that thread is in the program, that is, what command it is going to execute next.

Spec threads are created by top level THREAD declarations in a module. They make all possible concurrency explicit at the top level of each module. A thread is syntactically much like a procedure, but instead of being invoked by a client or by another procedure, it is automatically invoked in parallel initially, for every possible value of its arguments.<sup>2</sup> When it executes a RET (or reaches the end of its body), a thread simply makes no more transitions. However, threads are often written to loop indefinitely.

Spec does not have COBEGIN OF FORK constructs, as many programming languages do, these are considerably more difficult to define precisely, since they are tangled up with the control structure of the program. Also, because one Spec thread starts up for every possible argument of the THREAD declaration, they tend to be more convenient for most of the specs and code in this course. To keep the thread from doing anything until a certain point in the computation (or at all), use an initial guard for the entire body as in the Sieve example below.

A thread is named by the name in the declaration and the argument values. Thus, the threads declared by THREAD FOO(bOOl) = ..., for example, would be named FOO(true) and FOO(false) The names of local variables are qualified by both the name of the thread that is the root of the call stack, and by the name of the procedure invoked.<sup>3</sup> In other words, each procedure in each thread has its own set of local variables. So for example, the local variable p in the Sieve example appears in the state as Sieve(0).p, Sieve(1).p, .... If there were a PROC FOO called by Sieve with a local variable baz, the state might be defined at Sieve(0).FOO.baz, Sieve(1).FOO.baz, .... The pseudo-names a, a, a, b, c are qualified only by the thread.

<sup>&</sup>lt;sup>1</sup> The variables declared by a program are not allowed to have labels as their values, hence there is no Label type. <sup>2</sup> This differs from the threads in Java, in Modula 3, or in many C implementations. These languages start a computation with one thread and allow it to create and destroy threads dynamically using fork and join operations.

<sup>&</sup>lt;sup>3</sup>This works for non-recursive procedures. To accommodate recursive procedures, the state must involve something equivalent to a stack. Probably the simplest solution is to augment the state space by tacking on the nesting depth of the procedure to all the names and program counter values defined above. For example, h + ".P.v" becomes h + ".P.v" + d.enc, for every positive integer d. An invocation transition at depth d goes to depth d+1.

2004

Each atomic command defines a transition, just as in the sequential semantics. However, now a transition is enabled by the program counter value. That is, a transition can only occur if the program counter of some thread equals the label before the command, and the transition sets the program counter of that thread to the label after the command. If the command at the label in the program counter fails (for example, because it has a guard that tests for a buffer to be non-empty, and the buffer is empty in the current state), the thread is "stuck" and does not make any transitions. However, it may become unstuck later, because of the transitions of some other threads. Thus, a command failing does not necessarily (or even usually) mean that the thread fails.

We won't give the non-atomic semantics precisely here as we did for the atomic semantics in handout 9, since it involves a number of fussy details that don't add much insight. Also, it's somewhat arbitrary. You can always get exactly the atomicity you want by adding local variables and semicolons to increase the number of atomic transitions (see the examples below), or <<<...>> brackets to decrease it.

It's important, however, to understand the basic ideas.

- Each atomic command in a thread or procedure defines a transition (atomic procedures and functions are taken care of by the atomic semantics).

- The program counters enable transitions: a transition can only occur if the program counter for some thread equals the label before the command, and the transition sets that program counter to the label after the command.

Thus the state of the system is the global state plus the state of all the threads. The state of a thread is its pc, a, and x values, the local variables of the thread, and the local variables of each procedure that has been called by the thread and has not yet returned.

Suppose the label before the command c is  $\alpha$  and the one after the command is  $\beta$ , and the transition function defined by MC(c) in handout 9 is (\ s, o | rel). Then if c is in thread h, its transition function is

$(\ s, \circ | s(h+", \$pc") = \alpha / \circ (h+", \$pc) = \beta / rel')$ If c is in procedure P, that is, c can execute for any thread whose program counter has reached  $\alpha$ , its transition function is

(\ s, o | (EXISTS h: Thread | s(h+".P.\$pc") = α /\ o(h+".P.\$pc) = β /\ rel')) Here rel' is rel with each reference to a local variable v changed to h + ".v" or h + ".P.v".

#### Labels in Spec

What are the atomic transitions in a Spec program? In other words, where do we put the labels? The basic idea is to build in as little atomicity as possible (since you can always put in what you need with <<...>>). However, expression evaluation must be atomic, or reasoning about expressions would be a mess. To use Spec to model code in which expression evaluation is not atomic (C code, for example), you must add temporary variables. Thus x := a + b + c becomes

VAR t | << t := a >>; << t := t + b >>; << x := t + c >>

For a real-life example of this, see MutexImpl.acq below.

The simple commands, SKIP, HAVOC, RET, and RAISE, are atomic, as is any command in atomicity brackets <<...>>.

For an invocation, there is a transition to evaluate the argument and set the sa variable, and one to send control to the start of the body. The RET command's transition sets sa and leaves control at the end of the body. The next transition leaves control after the invocation. So every procedure invocation has at least four transitions: evaluate the argument and set sa, send control to the body, do the RET and set sa, and return control from the body. The reason for these fussy details is to ensure that the invocation of an external procedure has start and end transitions that do not change any other state. These are the transitions that appear in the trace and therefore must be identical in both the spec and the code that implements it.

Minimizing atomicity means that an assignment is broken into separate transitions, one to evaluate the right hand side and one to change the left hand variable. This also has the advantage of consistency with the case where the right hand side is a non-atomic procedure invocation. Each transition happens atomically, even if the variable is "big". Thus x := exp is

Since there are no additional labels for the c1 [] c2 command, the initial transition of the compound command is enabled exactly when the initial transition of either of the subcommands is enabled (or if they both are). Thus, the choice is made based only on the first transition. After that, the thread may get stuck in one branch (though, of course, some other thread might unstick it later). The same is true for [\*], except that the initial transition for c1 [\*] c2 can only be the initial transition of c2 if the initial transition of c1 is not enabled. And the same is also true for VAR. The value chosen for id in VAR id | c must allow c to make at least one transition; after that the thread might get stuck.

DO has a label, but OD does not introduce any additional labels. The starting and ending program counter value for c in DO c OD is the label on the DO. Thus, the initial transition of c is enabled when the program counter is the label on the DO, and the last transition sets the program counter back to that label. When c fails, the program counter is set to the label following the OD.

To sum up, there's a label on each :=, =>, ';', EXCEPT, and DO outside of <<...>. There is never any label inside atomicity brackets. It's convenient to write the labels in brackets after these symbols.

There's also a label at the start of a procedure, which we write on the = of the declaration, and a label at the end. There is one label for a procedure invocation, after the argument is evaluated; we write it just before the closing ')'. After the invocation is complete, the PC goes to the next label after the invocation, which is the one on the := if the invocation is in an assignment.

As a consequence of this labeling, as we said before, a procedure invocation has one transition to evaluate the argument expression,

one to set the program counter to the label immediately before the procedure body, one for every transition of the procedure body (using the labels of the body), one for the RET command in the body, which sets the program counter after the body, and a final transition that sets it to the label immediately following the invocation.

Here is a meaningless sequential example, just to show where the labels go. They are numbered in the order they are reached during execution.

#### External actions

In sequential Spec a module has only external actions; each invocation of a function or atomic procedure is an external action. In concurrent Spec there are two differences:

There are internal actions. These can be actions of an externally invoked PROC or actions of a thread declared and executing in the module.

There are two external actions in the external invocation of a (non-atomic) procedure: the call, which sends control from after evaluation of the argument to the entry point of the procedure, and the return, which sends control from after the RET command in the procedure to just after the invocation in the caller. These external transitions do not affect the \$a variable that communicates the argument and result values. That variable is set by the internal transitions that compute the argument and do the RET command.

There's another style of defining external interfaces in which every external action is an APROC. If you want to get the effect of a non-atomic procedure, you have to break it into two APROC's, one that delivers the arguments and sets the internal state so that internal actions will do the work of the procedure body, and a second that retrieves the result. This style is used in I/O automata<sup>4</sup>, but we will not use it.

### Examples

Here are two Spec programs that search for prime numbers and collect the result in a set primes; both omit the even numbers, initializing primes to {2}. Both are based on the *sieve of Eratosthenes*, testing each prime less than  $n^{1/2}$  to see whether it divides *n*. Since the threads may not be synchronized, we must ensure that all the numbers  $\leq n^{1/2}$  have been checked before we check *n*.

The first example is more like a spec, using an infinite number of threads, one for every odd number.

| CONST Odds         | = {i: Nat   i // 2 = 1 /\ i > 1 }                                 |                   |

|--------------------|-------------------------------------------------------------------|-------------------|

| VAR primes<br>done | : SET Nat := {2}<br>: SET Nat := {}                               | % numbers checked |

| INVARIANT (ALL 1   | Nat   n IN done /\ IsPrime(n) ==<br>/\ n IN primes ==> IsPrime(n) | 1                 |

FUNC Sqrt(n: Nat) -> Int = RET { i: Nat | i\*i <= n }.max</pre>

The second example, on the other hand, is closer to code, running ten parallel searches. Although there is one thread for every integer, only threads Sieve(0), Sieve(1), ..., Sieve(9) are "active", because of the initial guard, Differences from Sievel are boxed.

next(i) := n + 2\*nThreads

OD

## **Big atomic actions**

As we saw earlier, we need atomic actions for practical, easy concurrency. Spec lets you specify any grain of atomicity in the program just by writing << ... >> brackets.<sup>5</sup> It doesn't tell you where to write the brackets. If the environment in which the program has to run doesn't timpose any constraints, it's usually best to make the atomic actions as big as possible, because big atomic actions are easier to reason about. But big atomic actions are often too hard or too expensive to code, or the reduction in concurrency hurts performance too much, so that we have to make do with small ones. For example, in a shared-memory multiprocessor typically only the individual instructions are atomic, and we can only write one disk block atomically. So we are faced with the problem of showing that code with small atomic actions satisfies a spec with bigger ones.

## The idea

The standard way of doing this is by some kind of 'non-interference'. The idea is based on the following observation. Suppose we have a program with a thread h that contains the sequence

(1)

А; В

<sup>&</sup>lt;sup>4</sup> Nancy Lynch, *Distributed Algorithms*, Morgan Kaufmann, 1996, Chapter 8.

$<sup>^{5}</sup>$  As we have seen, Spec does treat expression evaluation as atomic. Recall that if you are dealing with an environment in which an expression like x(i) + f(y) can't be evaluated atomically, you should model this by writing VAR t1, t2 | t1 := x(i); t2 := f(y); ... t1 + t2 ....

as well as an arbitrary collection of other commands. We denote the program counter value before A by  $\alpha$  and at the semi-colon by  $\beta$ . We are thinking of the program as

h.\$pc =  $\alpha$  => A [] h.\$pc =  $\beta$  => B [] C<sub>1</sub> [] C<sub>2</sub> [] ...

where each command has an appropriate guard that enables it only when the program counter for its thread has the right value. We have written the guards for A and B explicitly.

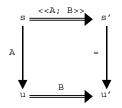

Suppose B denotes an arbitrary atomic command, and A denotes an atomic command that commutes with every command in the program (other than B) that is enabled when h is at the semicolon, that is, when  $h.\$pc = \beta$ . (We give a precise meaning for 'commutes' below.) In addition, both A and B have only internal actions. Then it's intuitively clear that the program with (1) simulates a program with the same commands except that instead of (1) it has

<< A; B >>

Informally this is true because any C's that happen between A and B have the same effect on the state that they would have if they happened before A, since they all commute with A. Note that the C's don't have to commute with B; commuting with A is enough to let us 'push' C before A. A symmetric argument works if all the C's commute with B, even if they don't commute with A.

Thus we have achieved the goal of making a bigger atomic command  $\langle A; B \rangle$  out of two small ones A and B. We can call the big command D and repeat the process on E; D to get a still bigger command  $\langle E; A; B \rangle$ .

How do we ensure that only a command c that commutes with A can execute while h. $pc = \beta$ ? The simplest way is to ensure that the variables that A touches (reads or writes) are disjoint from the variables that c writes, and vice versa; then they will surely commute. Two such commands are called 'non-interfering'. There are two easy ways to show that commands are non-interfering. One is that A touches only local variables of h. Only actions of h touch local variables of h, and the only action of h that is enabled when h.  $pc = \beta$  is B. So any sequence of commands that touch only local variables is atomic, and if it is preceded or followed by a single arbitrary atomic command the whole thing is still atomic.<sup>6</sup>

The other easy case is a critical section protected by a mutex. Recall that a critical section for v is a command with the property that if some thread's PC is in the command, then no other thread's PC can be in any critical section for v. If the only commands that touch v are in critical sections for v, then we know that only B and commands that don't touch v can execute while h. $pc = \beta$ . So if every command in any critical section for v only touches v (and perhaps local variables), then the program simulates another program in which every critical section is an atomic command. A critical section is usually coded by acquiring a *lock* or *mutex* and holding it for the duration of the section. The property of a lock is that it's not possible to acquire it when it is already held, and this ensures the mutual exclusion property for critical sections.

It's not necessary to have exclusive locks; reader/writer locks are sufficient for non-interference, because read operations all commute with each other. Indeed, any locking scheme will work in which non-commuting operations hold mutually exclusive locks; this is the basis of rules for

<sup>6</sup> See Leslie Lamport and Fred B. Schneider. Pretending atomicity. Research Report 44, Digital Equipment Corporation Systems Research Center, Palo Alto, CA, May 1989. 'lock conflicts'. See handout 14 on practical concurrency for more details on different kinds of locks.

Another important case is mutex acquire and release operations. These operations only touch the mutex, so they commute with everything else. What about these operations on the same mutex in different threads? If both can execute, they certainly don't yield the same result in either order; that is, they don't commute. When can both operations execute? We have the following cases (writing the executing thread as an explicit argument of each operation):

| A        | С         | Possible sequence?                                |

|----------|-----------|---------------------------------------------------|

| m.acq(h) | m.acq(h') | No: C is blocked by h holding m                   |

| m.acq(h) | m.rel(h') | No: C won't be reached because h' doesn't hold m  |

| m.rel(h) | m.acq(h') | OK                                                |

| m.rel(h) | m.rel(h') | No: one thread doesn't hold m, hence won't do rel |

So m.acq commutes with everything that's enabled at  $\beta$ , since neither mutex operation is enabled at  $\beta$  in a program that avoids havoc. But m.rel(h) doesn't commute with m.acq(h'). The reason is that the A; C sequence can happen, but the C; A sequence m.acq(h'); m.rel(h) cannot, because in this case h doesn't hold m and therefore can't be doing a rel. Hence it's not possible to flip every C in front of m.rel(h) in order to make A; B atomic.

What does this mean? You can acquire more locks and still keep things atomic, but as soon as you release one, you no longer have atomicity.<sup>7</sup>

A third important case of commuting operations, producer-consumer, is similar to the mutex case. A producer and a consumer thread share no state except a buffer. The operations on the buffer are put and get, and these operations commute with each other. The interesting case is when the buffer is empty. In this case get is blocked until a put occurs, just as in the mutex example when h holds the lock m.acq(h') is blocked until m.rel(h) occurs. This is why programming with buffers, or dataflow programming, is so easy.

## Proofs

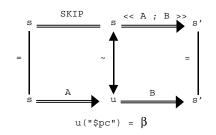

How can we make all this precise and *prove* that a program containing (1) implements the same program with (2) replacing (1), using our trusty method of abstraction relations? For easy reference, we repeat (1) and (2).

| А; [β] В   | (1) |

|------------|-----|

| << A; B >> | (2) |

As usual, we call the complete program containing (2) the spec *S* and the complete program containing (1) the code *T*. We need an abstraction relation AR between the states of *T* and the states of *S* under which every transition of *T* simulates a (possibly empty) trace of *S*. Note that the state spaces of *T* and *S* are the same, except that h.\$pc can never be  $\beta$  in *S*. We use *s* and *u* for states of *S* and *T*, to avoid confusion with various other uses of *t*.

http://gatekeeper.dec.com/pub/DEC/SRC/research-reports/abstracts/src-rr-044.html

<sup>&</sup>lt;sup>7</sup> Actually, this is not quite right. If you hold several locks, and touch data only when you hold its lock, you have atomicity until you release all the locks.

First we need a precise definition of "C is enabled at  $\beta$  and commutes with A". For any command X, we write  $u \ge u'$  for MC (X) (u, u'), that is, if x relates u to u'. The idea of 'commutes' is that <<A; C>> is the same as <<C; A>>, and the definition follows from the meaning of semicolon:

(ALL u1, u2 | (EXISTS u | u1 A u /\ u C u2 /\ u("h.\$pc") =

$$\beta$$

;

==> (EXISTS u' | u1 C u' /\ u' A u2) )

This says that any result that you could get by doing  $A_i$  C you could also get by doing C; A.

It seems reasonable to do the proof by making A simulate the empty trace and B simulate <<A; B>>, since we know more about A than about B; every other command simulates itself.

So we make AR the identity everywhere except at  $\beta$ , where it relates any state u that can be reached from s by A to s. This expresses the intention that at  $\beta$  we haven't yet done A in S, but we have done A in T. (Since A may take many states to s, this can't just be an abstraction function.) We write  $u \sim s$  for "AR relates u to s". Precisely, we say that  $u \sim s$  if

Why is this an abstraction relation? It certainly relates an initial state to an initial state, and it certainly works for any transition  $u \rightarrow u'$  that stays away from  $\beta$ , that is, in which  $u("h.\$pc") \neq \beta$  and  $u'("h.\$pc") \neq \beta$ , since the abstract and concrete states are the same. What about transitions that do involve  $\beta$ ?

• If h. \$pc changes to β then we must have executed A. The picture is

The abstract trace is empty, so the abstract state doesn't change: s = s'. Also, s' = u because only equal states are related when  $h.\$pc \# \beta$ . But we executed A, so  $u \land u'$ , so  $s' \sim u'$  because of the equalities.

• If h.  $p_C$  starts at  $\beta$  then the command must be either B or some C that commutes with A. If the command is B, then the picture is

To show the top relation, we have to show that there exists an  $s_0$  such that  $s \land s_0$  and  $s_0 \land s'$ , by the meaning of semicolon. But u has exactly this property, since s' = u'.

• If the command is c, then the picture is

But this follows from the definition of 'commutes': we are given s, u, and u' related as shown, and we need s' related as shown, which is just what the definition gives us, with u1 = s, u2 = u', and u' = s'.

## **Examples of concurrency**

This section contains a number of example specs and codes that illustrate various aspects of concurrency. The specs have large atomic actions that keep them simple. The codes have smaller atomic actions that reflect the realities of the machines on which they have to run. Some of the examples of code illustrate easy concurrency (that is, that use locks): RWLockImpl and BufferImpl. Others illustrate hard concurrency: SpinLock, Mutex2Impl, ClockImpl, MutexImpl, and ConditionImpl.

#### Incrementing a register

The first example involves incrementing a register that has Read and Write operations. Here is the unsurprising spec of the register, which makes both operations atomic:

MODULE Register EXPORT Read, Write =

VAR x : Int := 0 APROC Read() -> Int = << RET x >> APROC Write(i: Int) = << x := i >>

#### END Register

To increment the register, we could use the following procedure:

PROC Increment() = VAR t: Int | t := Register.Read(); t := t + 1; Register.Write(t)

Suppose that, starting from the initial state where x = 0, *n* threads execute Increment in parallel. Then, depending on the interleaving of the low-level steps, the final value of the register could be anything from 1 to *n*. This is unlikely to be what was intended. Certainly this code doesn't implement the spec

PROC Increment() =  $\langle x := x + 1 \rangle$

Exercise: Suppose that we weaken our atomicity assumptions to say that the value of a register is represented as a sequence of bits, and that the only atomic operations are reading and writing individual bits. Now what are the possible final states if *n* threads execute Increment in parallel?

Alternatively, consider a new module RWInc that explicitly supports Increment operations in addition to Read and Write. This might add the following (exported) procedure to the Register module:

PROC Increment() = x := x+1

Or, more explicitly:

PROC Increment() = VAR t: Int | << t := x >>; << x := t+1 >>

Because of the fine grain of atomicity, it is still true that if *n* threads execute Increment in parallel then, depending on the interleaving of the low-level steps, the final value of the register could be anything from 1 to *n*. Putting the procedure inside the Register module doesn't help. Of course, making Increment an APROC would certainly do the trick.

#### Mutexes

Here is a spec of a simple Mutex module, which can be used to ensure mutually exclusive execution of critical sections; it is copied from handout 14 on practical concurrency. The state of a mutex is nil if the mutex is free, and otherwise is the thread that holds the mutex.

CLASS Mutex EXPORT acq, rel =

VAR m : (Thread + Null) := nil

% Each mutex is either nil or the thread holding the mutex.

% The variable SELF is defined to be the thread currently making a transition.

```

APROC acq() = << m = nil => m := SELF; RET >>

APROC rel() = << m = SELF => m := nil ; RET [*] HAVOC >>

```

END Mutex

If a thread invokes acq when  $m \neq nil$ , then the body fails, This means that there's no possible transition for that thread, and the thread is blocked, waiting at this point until the guard becomes true. If many threads are blocked at this point, then when m is set to nil, one is scheduled first, and it sets m to itself atomically; the other threads are still blocked.

The spec says that if a thread that doesn't hold m does m.rel, the result is HAVOC. As usual, this means that the code is free to do anything when this happens. As we shall see in the SpinLock code below, one possible 'anything' is to free the mutex anyway.

Here is a simple use of a mutex m to make the Increment procedure atomic:

PROC Increment() = VAR t: Int |

m.acq; t := Register.Read(); t := t + 1; Register.Write(t); m.rel

This keeps concurrent calls of Increment from interfering with each other. If there are other write accesses to the register, they must also use the mutex to avoid interfering with threads executing Increment.

Spin locks

A simple way to code a mutex is to use a *spin lock*. The name is derived from the behavior of a thread waiting to acquire the lock—it "spins", repeatedly attempting to acquire the lock until it is finally successful.

Here is incorrect code:

CLASS BadSpinLock EXPORT acq, rel =

```

TYPE FH = ENUM[free, held]

VAR fh := free

PROC acq() =

D0 << fh = held => SKIP >> OD; % wait for fh = free

<< fh := held >> % and acquire it

PROC rel() = << fh := free >>

```

END BadSpinLock

This is wrong because two concurrent invocations of acq could both find fh = free and subsequently both set fh := held and return.

Here is correct code. It uses a more complex atomic command in the acq procedure. This command corresponds to the atomic "test-and-set" instruction provided by many real machines to code locks. It records the initial value of the lock, and then sets it to held. Then it tests the initial value; if it was free, then this thread was successful in atomically changing the state of the lock from free to held. Otherwise some other thread must hold the lock, so we "spin", repeatedly trying to acquire it until we succeed. The important difference in SpinLock is that the guard now involves only the local variable t, instead of the global variable fh in BadSpinLock. A thread acquires the lock when it is the one that changes it from free to held, which it checks by testing the value returned by the test-and-set.

CLASS SpinLock EXPORT acq, rel =

```

TYPE FH = ENUM[free, held]

VAR fh := free

PROC acq() = VAR t: FH |

DO << t := fh; fh := held >>; IF t = free => RET [*] SKIP FI OD

PROC rel() = << fh := free >>

END SpinLock

```

#### END RWLock

The following simple code is similar to ForgetfulMutex. It has the same atomicity as RWLock, but uses a different data structure to represent possession of the lock. Specifically, it uses a single integer variable rw to keep track of the number of readers (positive) or the existence of a writer (-1).

CLASS ForgetfulRWL EXPORT rAcq, rRel, wAcq, wRel =

VAR rw := 0 % >0 gives number of readers, 0 means free, -1 means one writer

APROC rAcq() = << rw >= 0 => rw + := 1 >> APROC wAcq() = << rw = 0 => rw := -1 >> APROC rRel() = << rw - := 1 >> APROC wRel() = << rw := 0 >>

END ForgetfulRWL

We will see later how to code ForgetfulRWL using a mutex.

#### Condition variables

Mutexes are used to protect shared variables. Often a thread h cannot proceed until some condition is true of the shared variables, a condition produced by some other thread. Since the variables are protected by a lock, and can be changed only by the thread holding the lock, h has to release the lock. It is not efficient to repeatedly release the lock and then re-acquire it to check the condition. Instead, it's better for h to *wait* on a *condition variable*, as we saw in handout 14. Whenever any thread changes the shared variables in such a way that the condition might become true, it *signals* the threads waiting on that variable. Sometimes we say that the waiting threads 'wake up' when they are signaled. Depending on the application, a thread may signal one or several of the waiting threads.

Here is the spec for condition variables, copied from handout 14 on practical concurrency.

CLASS Condition EXPORT wait, signal, broadcast =

Of course this code is not practical in general unless each thread has its own processor; it is used, however, in the kernels of most operating systems for computers with several processors. Later, in MutexImpl, we give practical code that queues a waiting thread.

The SpinLock code differs from the Mutex spec in another important way. It "forgets" which thread owns the mutex. The following ForgetfulMutex module is useful in understanding the SpinLock code—in ForgetfulMutex, the threads get forgotten, but the atomicity is the same as in Mutex.

#### CLASS ForgetfulMutex EXPORT acq, rel =

TYPE FH = ENUM[free, held]

VAR fh := free

PROC acq() = << fh = free => fh := held >>

PROC rel() = << fh := free >>

#### END ForgetfulMutex

Note that ForgetfulMutex releases a mutex regardless of which thread acquired it, and it does a SKIP if the mutex is already free. This is one of the behaviors permitted by the Mutex spec, which allows anything under these conditions.

Later we will show that SpinLock implements ForgetfulMutex and that ForgetfulMutex implements Mutex, from which it follows that SpinLock implements Mutex. We don't give the abstraction function here because it involves the details of program counters.

#### Read/write locks

Here is a spec of a module that provides locks with two modes, read and write, rather than the single mode of a mutex. Several threads can hold a lock in read mode, but only one thread can hold a lock in write mode, and no thread can hold a lock in read mode if some thread holds it in write mode. In other words, read locks can be shared, but write locks are exclusive; hence the locks are also known as 'shared' and 'exclusive'.

CLASS RWLock EXPORT rAcq, rRel, wAcq, wRel =

```

TYPE ST

= SET Thread

: ST := {}

: ST := {}

: ST := {}

VAR r

W

% Acquires r if no current write locks

APROC rAcq() =

<< SELF IN (r \setminus w) => HAVOC [*] w

= {} => r \/ := {SELF} >>

% Acquires w if no current locks

APROC wAcq() =

<< SELF IN (r \/ w) => HAVOC [*] (r \/ w) = {} => w := {SELF} >>

% Releases r if the thread has it

APROC rRel() =

<< ~ (SELF IN r) => HAVOC [*]

r - := {SELF} >>

APROC wRel() =

<< ~ (SELF IN w) => HAVOC [*]

:= {}

w

>>

```

As we saw in handout 14, it's not necessary to have a single condition for each set of shared variables. We want enough condition variables so that we don't wake up too many threads whose conditions are not yet satisfied, but not so many that the cost of doing all the signals is excessive.

### Coding read/write lock using condition variables

This example shows how to use easy concurrency to make more complex locks and scheduling out of basic mutexes and conditions. We use a single mutex and condition for all the read-write locks here, but we could have separate ones for each read-write lock, or we could partition the locks into groups that share a mutex and condition. The choice depends on the amount of contention for the mutex.

Compare the code with ForgetfulRWL; the differences are highlighted with boxes. The <<...>> in ForgetfulRWL have become m.acq ... m.rel; this provides atomicity because shared variables are only touched while the lock is held. The other change is that each guard that could block (in this example, all of them) is replaced by a loop that tests the guard and does c.wait if it doesn't hold. The release operations do the corresponding signal or broadcast operations.

CLASS RWLockImpl EXPORT rAcq, rRel, wAcq, wRel = % implements ForgetfulRWL

VAR rw : Int := 0 m := m.new() c := c.new()

% ABSTRACTION FUNCTION ForgetfulRWL.rw = rw

| $ \begin{array}{llllllllllllllllllllllllllllllllllll$      |  |

|------------------------------------------------------------|--|

| PROC rRel(1) =                                             |  |

| m.acq; rw - := 1; IF rw = 0 => c.signal [*] SKIP FI; m.rel |  |

| PROC wRel(1) =                                             |  |

| <pre>m.acq; rw := 0; c.broadcast; m.rel</pre>              |  |

|                                                            |  |

END RWLockImpl

This is the prototypical example for scheduling resources. There are mutexes (just m in this case) to protect the scheduling data structures, conditions (just c in this case) on which to delay threads that are waiting for a resource, and logic that figures out when it's all right to allocate a resource (the read or write lock in this case) to a thread.

Note that this code may starve a writer: if readers come and go but there's always at least one of them, a waiting writer will never acquire the lock. How could you fix this?

### An unbounded FIFO buffer

In this section, we give a spec and code for a simple unbounded buffer that could be used as a communication channel between two threads. This is the prototypical example of a *producer-consumer* relation between threads. Other popular names for Produce and Consume are Put and Get.

## MODULE Buffer[T] EXPORT Produce, Consume =

VAR b : SEQ T := {}

APROC Produce(t) = << b + := {t} >>

APROC Consume() -> T = VAR t | << b # {} => t := b.head; b := b.tail; RET t >>

END Buffer

The code is another example of easy concurrency.

MODULE BufferImpl[T] EXPORT Produce, Consume =

| VAR | b | :  | SEQ T := | { } |

|-----|---|----|----------|-----|

|     | m | := | m.new()  |     |

|     | C | := | c.new()  |     |

% ABSTRACTION FUNCTION Buffer.b = b

PROC Produce(t) = m.acq; IF b = {} => c.signal [\*] SKIP FI; b + := {t}; m.rel

PROC Consume() -> T = VAR t | m.acq; D0 b = {} => c.wait(m) OD; t := b.head; b := b.tail; m.rel; RET t

END BufferImpl

Coding Mutex with memory

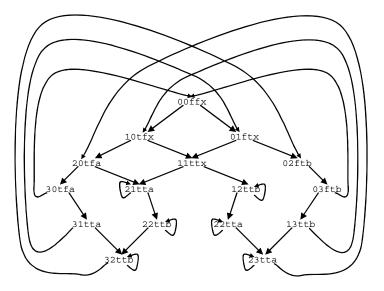

The usual way to code Mutex is to use an atomic test-and-set operation; we saw this in the MutexImpl module above. If such an operation is not available, however, it's possible to code Mutex using only atomic read and write operations on memory. This requires an amount of storage linear in the number of threads, however. We give a fair algorithm due to Peterson<sup>8</sup> for two threads; if thread h is competing for the mutex, we write h\* for its competitor.

### CLASS Mutex2Impl EXPORT acq, rel =

```

VAR req : Thread -> Bool := {* -> false}

lastReq : Int

PROC acq() =

[a_0] req(SELF) := true;

[a_1] lastReq := SELF;

DO [a_2] (req(SELF*) /\ lastReq = SELF) => SKIP OD [a_3]

PROC rel() = req(SELF) := false

```

END Mutex2Impl

This is hard concurrency, and it's tricky to show that it works. To see the idea, consider first a simpler version of acq that ensures mutual exclusion but can deadlock:

PROC acq0() =  $[a_0]$  req(SELF) := true;

<sup>&</sup>lt;sup>8</sup> G. Peterson, A new solution to Lamport's concurrent programming problem using small shared variables. *ACM Trans. Programming Languages and Systems* **5**, 1 (Jan. 1983), pp 56-65.

% busy wait

DO  $[a_2]$  reg(SELF\*) => SKIP OD  $[a_3]$

We get mutual exclusion because once req(h) is true,  $h* can't get from <math>a_2$  to  $a_3$ . Thus req(h) acts as a lock that keeps the predicate  $h*.\$pc = a_2$  true once it becomes true. Only one of the threads can get to  $a_3$  and acquire the lock. We might call the algorithm 'polite' because each thread defers to the other one at  $a_2$ .

Of course, acq0 is no good because it can deadlock—if both threads get to  $a_2$  then neither can progress. acq avoids this problem by making it a little easier for a thread to progress: even if  $req(h^*)$ , h can take  $(a_2, a_3)$  if lastReq # h. Intuitively this maintains mutual exclusion because:

If both threads are at  $a_2$ , only the one  $\neq lastReq$ , say h, can progress to  $a_3$  and acquire the lock. Since lastReq won't change, h\* will remain at  $a_2$  until h releases the lock.

Once h has acquired the lock with h\* not at  $a_2$ , h\* can only reach  $a_2$  by setting lastReq := h\*, and again h\* will remain at  $a_2$  until h releases the lock.

It ensures progress because the DO is the only place to get stuck, and whichever thread is not in lastReq will get past it. It ensures fairness because the first thread to get to  $a_2$  is the one that will get the lock first.

Abstractly, h has the mutex if req(h) / h. pc #  $a_2$ , and the transition from  $a_2$  to  $a_3$  simulates the body of Mutex.acq. Precisely, the abstraction function is

Mutex.m = (Holds0.set = {} => nil [\*] Holds0.set.choose)

We sketch the proof that Mutex2Impl implements Mutex later.

There is lots more to say about coding Mutex efficiently, especially in the context of sharedmemory multiprocessors.<sup>9</sup> Even on a uniprocessor you still need an implementation that can handle pre-emption; often the most efficient implementation gets the necessary atomicity by modifying the code for pre-emption to detect when a thread is pre-empted in the middle of the mutex code and either complete the operation or back up the state.

## Multi-word clock

Often it's possible to get better performance by avoiding locking. Algorithms that do this are called 'wait-free'; we gave a brief discussion in handout 14. Here we present a wait-free algorithm due to Lamport<sup>10</sup> for reading and incrementing a clock, even if clock values do not fit into a single memory location that can be read and written atomically.

We begin with the spec. It says that a Read returns some value that the clock had between the beginning and the end of the Read. As we saw in handout 8 on generalized abstraction functions,

where this spec is called LateClock, it takes a prophecy variable to show that this spec is equivalent to the simpler spec that just reads the clock value.

MODULE Clock EXPORT Read =

| VAR t :                            | Int := 0                                                 | % the current time                     |

|------------------------------------|----------------------------------------------------------|----------------------------------------|

| THREAD Tick() = D                  | O << t + := 1 >> OD                                      | % demon thread advances <code>t</code> |

| PROC Read() -> In<br><< tl := t >> | t = VAR t1: Int  <br>; << VAR t2   t1 <= t2 /\ t2 <= t = | > RET t2 >>                            |

|                                    |                                                          |                                        |

END Clock

The code below is based on the idea of doing reads and writes of the same multi-word data in opposite orders. Tick writes hi2, then lo, then hi1. Read reads hi1, then lo, then hi2; if it sees different values in hi1 and hi2, there must have been at least one carry during the read, so t must have taken on the value hi2 \* base. The function T expresses this idea. The atomicity brackets in the code are the largest ones that are justified by big atomic actions.

### MODULE ClockImpl EXPORT Read =

| CONST base           | := 2**32                                  |

|----------------------|-------------------------------------------|

| TYPE Word            | = Int SUCHTHAT (\ i: Int   i IN base.seq) |

| VAR lo<br>hil<br>hi2 | : Word := 0<br>: Word := 0<br>: Word := 0 |

% ABSTRACTION FUNCTION Clock.t = T(lo, hi1, hi2), Clock.Read.t1 = Read.t1Hist, Clock.Read.t2 = T(Read.tLo, Read.tH1, read.tH2)

Given this code for reading a two-word clock atomically starting with atomic reads of the low and high parts, it's obvious how to apply it recursively n-1 times to read an n word clock.

### User and kernel mutexes and condition variables

This section presents code for mutexes and condition variables based on the Taos operating system from DEC SRC. Instead of spinning like SpinLock, it explicitly queues threads waiting for locks or conditions. The code for mutexes has a fast path that stays out of the kernel in acq

<sup>&</sup>lt;sup>9</sup> J. Mellor-Crummey and M. Scott, Algorithms for scalable synchronization of shared-memory multiprocessors. *ACM Transactions on Computer Systems* **9**, 1 (Feb. 1991), pp 21-65. A. Karlin et al., Empirical studies of competitive spinning for a shared-memory multiprocessor. *ACM Operating Systems Review* **25**, 5 (Oct. 1991), pp 41-55.

<sup>&</sup>lt;sup>10</sup> L. Lamport, Concurrent reading and writing of clocks. ACM Transactions on Computer Systems 8, 4 (Nov. 1990), pp 305-310.

when the mutex is free, and in rel when no other thread is waiting for the mutex. There is also a fast path for signal, for the common case that there's nobody waiting on the condition. There's no fast path for wait, since that always requires the kernel to run in order to reschedule the processor (unless a signal sneaks in before the kernel gets around to the rescheduling).

Notes on the code for mutexes:

- 1. MutexImpl maintains a queue of waiting threads, blocks a waiting thread using Deschedule, and uses Schedule to hand a ready thread over to the scheduler to run.

- 2. SpinLock and ReleaseSpinLock acquire and release a global lock used in the kernel to protect thread queues. This is OK because code running in the kernel can't be pre-empted.

- 3. The loop in acq serves much the same purpose as a loop that waits on a condition variable. If the mutex is already held, the loop calls KernelQueue to wait until it becomes free, and then tries again. rel calls KernelRelease if there's anyone waiting, and KernelRelease allows just one thread to run. That thread returns from its call of KernelQueue, and it will acquire the mutex unless another thread has called acq and slipped in since the mutex was released (roughly).

- 4. There is clumsy code in KernelQueue that puts the thread on the queue and then takes it off if the mutex turns out to be free. This is not a mistake; it avoids a race with rel, which calls KernelRelease to take a thread off the queue only if it sees that the queue is not empty. KernelQueue changes q and looks at s; rel uses the opposite order to change s and look at q.

This opposite-order access pattern often works in hard concurrency, that is, when there's not enough locking to do the job in a straightforward way. We saw another version of it in Mutex2Impl, which sets req(h) before reading req(h\*). In this case req(h) acts like a lock to keep h\*. $pc = a_2$  from changing from true to false. We also saw it in ClockImpl, where the reader and the writer of the clock touch its pieces in the opposite order.

The boxes show how the state, acq, and rel differ from the versions in SpinLock.

| CLASS MutexImpl                                                                                                                                                                                                                                                                                                     | EXPORT acq, rel =                              | % implements ForgetfulMutex           |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------------|--|--|

|                                                                                                                                                                                                                                                                                                                     | Mutex.FH<br>= free<br>SEQ Thread := {}         |                                       |  |  |

| <pre>PROC acq() = VAR t DO &lt;&lt; t := fh;</pre>                                                                                                                                                                                                                                                                  | : FH  <br>; fh := held >>; IF t#held => RET    | [*] SKIP FI; KernelQueue() OD         |  |  |

| <pre>PROC rel() = fh :=</pre>                                                                                                                                                                                                                                                                                       | <pre>free; IF q # {} =&gt; KernelRelease</pre> | () [*] SKIP FI                        |  |  |

| % KernelQueue and Ke                                                                                                                                                                                                                                                                                                | rnelRelease run in the kernel so they can hold | the spin lock and call the scheduler. |  |  |

| <ul> <li>PROC KernelQueue() =</li> <li>% This is just a delay until there's a chance to acquire the lock. When it returns acq will retry.</li> <li>% Queuing SELF before testing fh ensures that the test in rel doesn't miss us.</li> <li>% The spin lock keeps KernelRelease from getting ahead of us.</li> </ul> |                                                |                                       |  |  |

% The spin lock keeps KernelRelease from getting ahead of us. SpinLock(); % indented code holds the lock

```

q + := {SELF};

IF fh = free => q := q.reml % undo previous line; will retry at acq

[*] Deschedule(SELF) % wait, then retry at acq

FI;

ReleaseSpinLock()

PROC KernelRelease() = % indented code holds the lock

IF q # {} => Schedule(q.head); q := q.tail [*] SKIP FI;

ReleaseSpinLock()

% The newly scheduled thread competes with others to acquire the mutex.

```

END MutexImpl

Now for conditions. Note that:

The 'event count' ecsig deals with the standard 'wakeup-waiting' race condition: the signal arrives after the m.rel but before the thread is queued. Note the use of the global spin lock as part of this. It looks as though signal always schedules exactly one thread if the queue is not empty, but other threads that are in wait but have not yet acquired the spin lock may keep running; in terms of the spec they are awakened by signal as well.

signal and broadcast test for any waiting threads without holding any locks, in order to avoid calling the kernel in this common case. The other event count ecWait ensures that this test doesn't miss a thread that is in KernelWait but hasn't yet blocked.

**CLASS ConditionImpl** EXPORT wait, signal, broadcast = % implements Condition

| TYPE M                                                  | = Mutex                                                                                                                   |                                                                              |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| VAR ecSig<br>ecWait<br>q                                | : Int := 0<br>: Int := 0<br>: SEQ Thread := {}                                                                            |                                                                              |

| PROC wait(m) =                                          | <pre>VAR i := ecSig   m.rel; KernelWait(i);</pre>                                                                         | m.acq                                                                        |

|                                                         | <pre>VAR i := ecWait   1; IF q # 0 \/ i # ecWait =&gt; KernelSig</pre>                                                    | 3                                                                            |

|                                                         | ) = VAR i := ecWait  <br>1; IF q # 0 \/ i # ecWait => KernelBro                                                           | padcast                                                                      |

| % if ecs                                                | <pre>+ := 1;<br/>ig changed, there must have been a Signal, so return,<br/>ecSig =&gt; q + := {SELF}; Deschedule(SE</pre> |                                                                              |

| PROC KernelSig(<br>SpinLock();<br>IF q #<br>ReleaseSpir | <pre>{} =&gt; Schedule(q.head); q := q.tail [</pre>                                                                       | % internal kernel procedure<br>% indented code holds the lock<br>*] SKIP FI; |

| PROC KernelBroa<br>SpinLock();                          |                                                                                                                           | % indented code holds the lock                                               |

DO q # {} => Schedule(q.head); q := q.tail OD; ReleaseSpinLock()

END ConditionImpl

The code for mutexes and conditions are quite similar; in fact, both are cases of a general semaphore.

## **Proving concurrent modules correct**

This section explains how to prove the correctness of concurrent program modules. It reviews the simulation method that we have already studied, which works just as well for concurrent as for sequential modules. Then several examples illustrate how the method works in practice. Things are more complicated in the concurrent case because there are many more atomic transitions, and because the program counters of the threads are part of the state.

Before using this method in its full generality, you should first apply the theorem on big atomic actions as much as possible, in order to reduce the number of transitions that your proofs need to consider. If you are programming with easy concurrency, that is, if your code uses a standard locking discipline, this will get rid of nearly all the work. If you are doing hard concurrency, there will still be lots of transitions, and in doing the proof you will probably find bugs in your program.

## The formal method

We use the same simulation technique that we used for sequential modules, as described in handouts 6 and 8 on abstraction functions. In particular, we use the most general version of this method, presented near the end of handout 8. This version does not require the transitions of the code to correspond one-for-one with the transitions of the spec. Only the external behavior (invocations and responses) must be the same—there can be any number of internal steps. The method proves that every trace (external behavior sequence) produced by the code can also be produced by the spec.

Of course, the utility of this method depends on an assumption that the external behavior of a module is all that is of interest to callers of the module. In other words, we are assuming here, as everywhere in this course, that the only interaction between the module and the rest of the program is through calls to the external routines provided by the module.

We need to show that each transition of the code simulates a sequence of transitions of the spec. An external transition must simulate a sequence that contains exactly one instance of the same external transition and no other external transitions; it can also contain any number of internal transitions. An internal transition must simulate a sequence that contains only internal transitions.

Here, once again, are the definitions:

Suppose *T* and *S* are modules with same external interface. An abstraction function *F* is a function from states(T) to states(S) such that:

Start: If u is any initial state of T then F(u) is an initial state of S.

*Step*: If *u* and *F*(*u*) are reachable states of *T* and *S* respectively, and (*u*,  $\pi$ , *u*') is a step of *T*, then there is an execution fragment of *S* from *F*(*u*) to *F*(*u*'), having the same trace.

Thus, if  $\pi$  is an invocation or response, the fragment consists of a single  $\pi$  step, with any number of internal steps before and/or after. If  $\pi$  is internal, the fragment consists of any number (possibly 0) of internal steps.

As we saw in handout 8, we may have to add history variables to T in order to find an abstraction function to S (and perhaps prophecy variables too). The values of history variables are calculated in terms of the actual variables, but they are not allowed to affect the real steps.

An alternative to adding history variables is to define an abstraction relation instead of an abstraction function. An abstraction relation AR is a relation between states(T) and states(S) such that:

*Start*: If *u* is any initial state of *T* then there exists an initial state *s* of *S* such that  $(u, s) \in AR$ .

Step: If *u* and *s* are reachable states of *T* and *S* respectively,  $(u, s) \in AR$ , and  $(u, \pi, u')$  is a step of *T*, then there is an execution fragment of *S* from *s* to some *s'* having the same trace, and such that  $(u', s') \in AR$ .

**Theorem:** If there exists an abstraction function or relation from T to S then T implements S; that is, every trace of T is a trace of S.

## Proof: By induction.

The strategy

The formal method suggests the following strategy for doing hard concurrency proofs.

- 1. Start with a spec, which has an abstract state.

- 2. Choose a concrete state for the code.

- 3. Choose an abstraction function, perhaps with history variables, or an abstraction relation.

- 4. Write code, identifying the critical actions that change the abstract state.

- 5. While (checking the simulation fails) do

Add an invariant, checking that all actions of the code preserve it, or

Change the abstraction function (step 3), the code (step 4), the invariant (step 5), or more than one, or

Change the spec (step 1).

This approach always works. The first four steps require creativity; step 5 is quite mechanical except when you find an error. It is somewhat laborious, but experience shows that if you are doing hard concurrency and you omit any of these steps, your program won't work. Be warned.

## Owicki-Gries proofs

Owicki and Gries invented a special case of this general method that is well known and sometimes useful.<sup>11</sup> Their idea is to do an ordinary sequential proof of correctness for each thread h, annotating each atomic command in the usual style with an assertion that is true at that point if h is the only thread running. This proof shows that the code of h establishes each assertion. Then you show that each of these assertions remains true after any command that any other thread can execute while h is at that point. This condition is called 'non-interference'; meaning not that other threads don't interfere with *access* to shared variables, but rather that they don't interfere with the *proof*.

The Owicki-Gries method amounts to defining an invariant of the form

h.\$pc =

$$\alpha \implies A_{\alpha} / h.$$

\$pc =  $\beta \implies A_{\beta} / \dots$

and showing that it's an invariant in two steps: first, that every step of h maintains it, and then that every step of any other thread maintains it. The hope is that this decomposition will pay because the most complicated parts of the invariant have to do with private variables of h that aren't affected by other threads.

## Prospectus for proofs

The remainder of this handout contains example proofs of correctness for several of the examples above: the RWLockImpl code for a read/write lock, the BufferImpl code for a FIFO buffer, the SpinLock code for a mutex (given in two versions), the Mutex2Impl code for a mutex used by two threads, and the ClockImpl code for a multi-word clock.

The amount of detail in these proofs is uneven. The proof of the FIFO buffer code and the second proof of the Spinlock code are the most detailed. The others give the abstraction functions and key invariants, but do not discuss each simulation step.

## **Read/write locks**

We sketch how to prove directly that the module RWLockImpl implements ForgetfulRWL.This could be done by big atomic actions, since the code uses easy concurrency, but as an easy introduction discuss how to do it directly. The two modules are based on the same data, the variable rw. The difference is that RWLockImpl uses a condition variable to prevent threads in acq from busy-waiting when they don't see the condition they require. It also uses a mutex to restrict accesses to rw, so that a series of accesses to rw can be done atomically.

An abstraction function maps RWLockImpl to ForgetfulRWL. The interesting part of the state of ForgetfulRWL is the rw variable. We define that by the identity mapping from RWLockImpl.

The mapping for steps is mostly determined by the rw identity mapping: the steps that assign to rw in RWLockImpl are the ones that correspond to the procedure bodies in ForgetfulRWL Then the checking of the state and step correspondences is pretty routine.

There is one subtlety. It would be bad if a series of rw steps done atomically in ForgetfulRWL were interleaved in RWLockImpl. Of course, we know they aren't, because they are always done by a thread holding the mutex. But how does this fact show up in the proof?

The answer is that we need some invariants for RWLockImpl. The first, a "dominant thread invariant", says that only a thread whose name is in m (a 'dominant thread') can be in certain portions of its code (those guarded by the mutex). The dominant thread invariant is in turn used to prove other invariants called "data protection invariants".

For example, one data protection invariant says that if a thread (in RWLockImpl) is in middle of the assignment statement rw + := 1, then in fact  $rw \ge 0$  (that is, the test is still true). We need this data protection invariant to show that the corresponding abstract step (the body of rAcq in ForgetfulRWLock) is enabled.

## BufferImpl implements Buffer

The FIFO buffer is another example of easy concurrency, so again we don't need to do a transition-by-transition proof for it. Instead, it suffices to show that a thread holds the lock m whenever it touches the shared variable b. Then we can treat the whole critical section during which the lock is held as a big atomic action, and the proof is easy. We will work out the important details of a low-level proof, however, in order to get some practice in a situation that is slightly more complicated but still straightforward, and in order to convince you that the theorem about big atomic actions can save you a lot of work.

First, we give the abstraction function; then we use it to show that the code simulates the spec. We use a slightly simplified version of Produce that always signals, and we introduce a local variable temp to make explicit the atomicity of assignment to the shared variable b.

## Abstraction function

The abstraction function on the state must explain how to interpret a state of the code as a state of the spec. Remember that to prove a concurrent program correct, we need to consider the entire state of a module, including the program counters and local variables of threads. For sequential programs, we can avoid this by treating each external operation as a single atomic action.

To describe the abstraction function, we thus need to explain how to construct a state of the spec from a state of the code. So what is a state of the Buffer module above? It consists of:

• A sequence of items b (the buffer itself);

Handout 17. Formal Concurrency

- for each thread that is active in the module, a program counter; and

- for each thread that is active in the module, values for local variables.

A state of the code is similar, except that it includes the state of the  ${\tt Mutex}$  and  ${\tt Condition}$  modules.

To define the mapping, we need to enumerate the possible program counters. For the spec, they are:

23

<sup>&</sup>lt;sup>11</sup> S. Owicki and D. Gries, An axiomatic proof technique for parallel programs. *Acta Informatica* 6, 1976, pp 319-340.

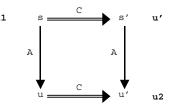

$P_1$  — before the body of Produce  $P_2$  — after the body of Produce  $C_1$  — before the body of Consume  $C_2$  — after the body of Consume

## or as annotations to the code:

PROC Produce(t) =  $[P_1] << b + := \{t\} >> [P_2]$

PROC Consume() -> T =  $[C_1] << b \# \{\} => VAR t := b.head | b := b.tail; RET t >> <math>[C_2]$

#### For the code, they are:

• For a thread in Produce:

$\begin{array}{l} p_1 & \longrightarrow \text{ before } \texttt{m.acq} \\ \text{ in } \texttt{m.acq} & \longrightarrow \text{ either before or after the action} \\ p_2 & \longrightarrow \text{ before temp } := \texttt{b} + \{\texttt{t}\} \\ p_3 & \longrightarrow \text{ before } \texttt{b} := \texttt{temp} \\ p_4 & \longrightarrow \text{ before } \texttt{c.signal} \\ \text{ in } \texttt{c.signal} & \longrightarrow \text{ either before or after the action} \\ p_5 & \longrightarrow \text{ before } \texttt{m.rel} \\ \text{ in } \texttt{m.rel} & \longrightarrow \text{ either before or after the action} \\ p_6 & \longrightarrow \text{ after } \texttt{m.rel} \end{array}$

• For a thread in Consume:

$\begin{array}{l} c_1 & \longrightarrow \text{ before } \texttt{m.acq} \\ \texttt{in } \texttt{m.acq} & \longrightarrow \text{ either before or after action} \\ c_2 & \longrightarrow \text{ before the test b } \# \; \{\} \\ c_3 & \longrightarrow \text{ before } \texttt{c.wait} \\ \texttt{in } \texttt{c.wait} & \longrightarrow \text{ at beginning, in middle, or at end} \\ c_4 & \longrightarrow \text{ before } \texttt{t.} \texttt{= b.head} \\ c_5 & \longrightarrow \text{ before temp } \texttt{:= b.tail} \\ c_6 & \longrightarrow \text{ before } \texttt{b.temp} \\ \texttt{c_7} & \longrightarrow \text{ before } \texttt{m.rel} \\ \texttt{in } \texttt{m.rel} & \longrightarrow \text{ either before or after action} \\ c_8 & \longrightarrow \text{ before } \texttt{RET } \texttt{t} \\ c_9 & \longrightarrow \text{ after } \texttt{RET } \texttt{t} \end{array}$

#### or as annotations to the code:

PROC Produce(t) = VAR temp |  $[p_1]$  m.acq;  $[p_2]$  temp = b + {t};  $[p_3]$  b := temp;  $[p_4]$  c.signal;  $[p_5]$  m.rel  $[p_6]$

PROC Consume() -> T = VAR t, temp  $\mid$

2004

Notice that we have broken the assignment statements into their constituent atomic actions, introducing a temporary variable temp to hold the result of evaluating the right hand side. Also, the PC's in the Mutex and Condition operations are taken from the specs of those modules (*not* the code; we prove their correctness separately). Here for reference is the relevant code.

```

APROC acq() = << m = nil => m := SELF; RET >> APROC rel() = << m = SELF => m := nil ; RET [*] HAVOC >>

```

APROC signal() = << VAR hs: SET Thread | IF hs <= c /\ hs # {} => c - := hs [\*] SKIP FI >>

Now we can define the mapping on program counters:

- If a thread h is not in Produce or Consume in the code, then it is not in either procedure in the spec.

- If a thread h is in Produce in the code, then:

If h.spc is in  $\{p_1, p_2, p_3\}$  or is in m.acq, then in the spec h.spc =  $P_1$ .

If h.  $p_{c}$  is in  $\{p_{4}, p_{5}, p_{6}\}$  or is in m.rel or c. signal then in the spec h.  $p_{c} = P_{2}$ .

• If a thread h is in Consume in the code, then:

If h. $pc \in \{c_1, ..., c_6\}$  or is in m.acq or c.wait then in the spec h. $pc = C_1$ .

If h. spc is in  $\{c_7, c_8, c_9\}$  or is in m.rel then in the spec h. spc =  $C_2$ .

The general strategy here is to pick, for each atomic transition in the spec, some atomic transition in the code to simulate it. Here, we have chosen the modification of b in the code to simulate the corresponding operation in the spec. Thus, program counters before that point in the code map to program counters before the body in the spec, and similarly for program counters after that point in the code.

This choice of the abstraction function for program counters determines how each transition of the code simulates transitions of the spec as follows:

- If  $\pi$  is an external transition,  $\pi$  simulates the singleton sequence containing just  $\pi$ .

- If  $\pi$  takes a thread from a PC of  $p_3$  to a PC of  $p_4$ ,  $\pi$  simulates the singleton sequence containing just the body of Produce.

- If  $\pi$  takes a thread from a PC of  $c_6$  to a PC of  $c_7$ ,  $\pi$  simulates the singleton sequence containing just the body of Consume.

- All other transitions  $\pi$  simulate the empty sequence.

2004

This example illustrates a typical situation: we usually find that a transition in the code simulates a sequence of either zero or one transitions in the spec. Transitions that have no effect on the abstract state simulate the empty sequence, while transitions that change the abstract state simulate a single transition in the spec. The proof technique used here works fine if a transition simulates a sequence with more than one transition in it, but this doesn't show up in most examples.

In addition to defining the abstract program counters for threads that are active in the module, we also need to define the values of their local variables. For this example, the only local variables are temp and the item t. For threads active in either Produce or Consume, the abstraction function on temp and t is the identity; that is, it defines the values of temp and t in a state of the spec to be the value of the identically named variable in the corresponding operation of the code.

Finally, we need to describe how to construct the state of the buffer b from the state of the code. Given the choices above, this is simple: the abstraction function is the identity on b.

## Proof sketch

To prove the code correct, we need to prove some invariants on the state. Here are some obvious ones; the others we need will become clear as we work through the rest of the proof.

First, define a thread h to be *dominant* if h.pc is in Produce and h.pc is in  $\{p_2, p_3, p_4, p_5\}$  or is at the end of m.acq, in c.signal, or at the beginning of m.rel, or if h.pc is in Consume and h.pc is in  $\{c_2, c_3, c_4, c_5, c_6, c_7\}$  or is at the end of m.acq, at the beginning or end of c.wait (but not in the middle), or at the beginning of m.rel.

Now, we claim that the following property is invariant: a thread h is dominant if and only if Mutex.m = h. This simply says that h holds the mutex if and only if its PC is at an appropriate point. This is the basic mutual exclusion property. Amazingly enough, given this property we can easily show that operations are mutually exclusive: for all threads h, h' such that  $h \neq h'$ , if h is dominant then h' is not dominant. In other words, at most one thread can be in the middle of one of the operations in the code at any time.

Now let's consider what needs to be shown to prove the code correct. First, we need to show that the claimed invariants actually are invariants. We do this using the standard inductive proof technique: Show that each initial state of the code satisfies the invariants, and then show that each atomic action in the code preserves the invariants. This is left as an exercise.

Next, we need to show that the abstraction function defines a simulation of the spec by the code. Again, this is an inductive proof. The first step is to show that an initial state of the code is mapped by the abstraction function to an initial state of the spec. This should be straightforward, and is left as an exercise. The second step is to show that the effects of each transition are preserved by the abstraction function. Let's consider a couple of examples.

• Consider a transition  $\pi$  from *r* to *r'* in which an invocation of an operation occurs for thread h. Then in state *r*, h was not active in the module, and in *r'*, its PC is at the beginning of the operation. This transition simulates the identical transition in the spec, which has the effect of moving the PC of this thread to the beginning of the operation. So AF(r) is taken to AF(r') by the transition.

Consider a transition in which a thread h moves from h. \$pc = p<sub>3</sub> to h. \$pc = p<sub>4</sub>, setting b to the value stored in temp. The corresponding abstract transition sets b to b + {t}. To show that this transition does the right thing, we need an additional invariant:

If h. $pc = p_3$ , then temp = b + {t}.

To prove this, we use the fact that if  $h.\$pc = p_3$ , then no other thread is dominant, so no other transition can change b. We also have to show that any transition that puts h.\$pc at this point establishes the consequent of the implication — but there is only one transition that does this (the one that assigns to temp), and it clearly establishes the desired property.

The transition in Consume that assigns to b relies on a similar invariant. The rest of the transitions involve straightforward case analyses. For the external transitions, it is clear that they correspond directly. For the other internal transitions, we must show that they have no abstract effect, i.e., if they take *r* to *r*', then AF(r) = AF(r'). This is left as an exercise.

## SpinLock implements Mutex, first version

The proof is done in two layers. First, we show that ForgetfulMutex implements Mutex. Second, we show that SpinLock implements ForgetfulMutex. For convenience, we repeat the definitions of the two modules.

#### CLASS Mutex EXPORT acq, rel =

VAR m : (Thread + Null) := nil

PROC acq() = << m = nil => m := SELF; RET >>

PROC rel() = << m = SELF => m := nil ; RET [\*] HAVOC >>

END Mutex

#### CLASS ForgetfulMutex EXPORT acq, rel =

| TYPE M | =  | ENUM[free, | held] |

|--------|----|------------|-------|

| VAR m  | := | free       |       |

PROC acq() = << m = free => m := held; RET >>

PROC rel() = << m := free; RET >>

END ForgetfulMutex

## Proof that ForgetfulMutex implements Mutex

These two modules have the same atomicity. The difference is that ForgetfulMutex forgets which thread owns the mutex, and so it can't check that the "right" thread releases it. We use an abstraction relation *AR*. It needs to be multi-valued in order to put back the information that is forgotten in the code. Instead of using a relation, we could use a function and history variables to keep track of the owner and havoc. The single-level proof given later on that Spinlock implements Mutex uses history variables.

The main interesting relationship that AR must express is:

## s.m is non-nil if and only if u.m = held.

In addition, *AR* must include less interesting relationships. For example, it has to relate the  $p_{C}$  values for the various threads. In each module, each thread is either not there at all, before the body, or after the body. Thus, *AR* also includes the condition:

The pc value for each thread is the same in both modules.

Finally, there is the technicality of the special  $\frac{1}{2} = true$  state that occurs in Mutex. We handle this by allowing *AR* to relate all states of ForgetfulMutex to any state with  $\frac{1}{2} = true$ .

Having defined AR, we just show that the two conditions of the abstraction relation definition are satisfied.

The start condition is obvious. In the unique start states of both modules, no thread is in the module. Also, if u is the state of ForgetfulMutex and s is the state of Mutex, then we have u.m = free and s.m = nil. It follows that  $(u, s) \in AR$ , as needed.