## DYNAMIC RECONFIGURATION IN A MODULAR COMPUTER SYSTEM

Roger R. Schell

June 1971

PROJECT MAC

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

Cambridge

Massachusetts 02139

### ACKNOWLEDGEMENT

I especially express my appreciation to my thesis supervisor, Professor Jerome H. Saltzer, for the substantial time and effort he spent supervising this thesis, and in particular for his helpful comments which greatly improved the presentation of this thesis.

Thanks are also due my readers, Professors F. J. Corbato and R. M. Fano, for their review and comments.

Appreciation is extended to Project MAC for making the Multics system available to the author both for conducting the research reported in this thesis, and for composing and reproducing this thesis document on-line.

A special note of thanks is due my wife, LaVonne for her assistance in typing this thesis, and for her patience and understanding throughout my years of graduate study at M.I.T.

Work reported herein was supported in part by Project MAC, an M.I.T. research project sponsored by the Advanced Research Projects Agency, Department of Defense, under Office of Naval Research Contract Nonr-4102(01).

#### DYNAMIC RECONFIGURATION IN A MODULAR COMPUTER SYSTEM\*

#### Abstract

This thesis presents an orderly design approach for dynamically changing the configuration of constituent physical units in a modular computer system. Dynamic reconfiguration contributes to high system availability by allowing preventive maintenance, development of new operating systems, and changes in system capacity on a noninterference basis. The design presented includes the operating system primitives and hardware architecture for adding and removing any (primary or secondary) storage module and associated processing modules while the system is running. Reconfiguration is externally initiated by a simple request from a human operator and is accomplished automatically without disruption to users of the system. This design allows the modules in an installation to be partitioned into separate noninterfering systems. The viability of the design approach has been demonstrated by employing it for a practical implementation of processor and primary memory dynamic reconfiguration in the Multics system at M.I.T.

<sup>\*</sup>This report reproduces a thesis of the same title submitted to the Department of Electrical Engineering, Massachusetts Institute of Technology, in partial fulfillment of the requirements for the degree of Doctor of Philosophy, May 1971.

# TABLE OF CONTENTS

| SEC | TION             | I                                               | PAGE          |  |  |

|-----|------------------|-------------------------------------------------|---------------|--|--|

|     |                  | ble of Contents<br>lustrations                  | <b>4</b><br>8 |  |  |

| 1.  | INTRODUCTION     |                                                 |               |  |  |

|     | 0.               | Modular Computer Systems                        | 9             |  |  |

|     | 1.               | Statement of the Problem                        | 10            |  |  |

|     |                  | 1. The Environment                              | 10            |  |  |

|     |                  | 2. The Nature of the Problem                    | 12            |  |  |

|     | 2.               | Background                                      | 15            |  |  |

|     | 3.               | Method of Presentation                          | 20            |  |  |

| 2.  | SYSTEM STRUCTURE |                                                 |               |  |  |

|     | 0.               | A General Model for Reconfiguration             | 22            |  |  |

|     |                  | 1. Resource Management Model                    | 22            |  |  |

|     |                  | 2. Reconfiguration Model                        | 28            |  |  |

|     |                  | 3. Design Approach for Reconfiguration          | 34            |  |  |

|     | 1.               | Modular Characteristics of System               | 37            |  |  |

|     |                  | 1. Processing Modules                           | 39            |  |  |

|     |                  | 2. Memory Modules                               | 40            |  |  |

|     | 2.               | Structure for Intermodule Communication         | 42            |  |  |

|     |                  | 1. Intermodule Links                            | 43            |  |  |

|     |                  | 2. Module Interface Ports                       | 44            |  |  |

|     | 3.               | Summary of System Structure for Reconfiguration | 46            |  |  |

| SEC | TION                        | 1                                                  | PAGE |  |  |  |

|-----|-----------------------------|----------------------------------------------------|------|--|--|--|

| 3.  | CHANGING MODULE UTILIZATION |                                                    |      |  |  |  |

|     | 0.                          | Dynamically Changing Resource Usage                | 48   |  |  |  |

|     | 1.                          | Storage Resource Management Environment            | 50   |  |  |  |

|     |                             | 1. Allocation With Unlimited Storage Capacity      | 51   |  |  |  |

|     |                             | 2. The Storage Utilization Problem                 | 53   |  |  |  |

|     |                             | 3. The Effect of Limited Storage Capacity          | 57   |  |  |  |

|     |                             | 4. The Storage Allocator                           | 58   |  |  |  |

|     | 2.                          | Removing a Storage Module                          | 63   |  |  |  |

|     |                             | 1. Freeing Demand Managed Storage                  | 70   |  |  |  |

|     |                             | 2. Freeing Wired Storage                           | 73   |  |  |  |

|     |                             | 1. Relocating Wired Information                    | 74   |  |  |  |

|     |                             | 2. Avoiding Conflict                               | 76   |  |  |  |

|     |                             | 3. Self-reference Problems                         | 80   |  |  |  |

|     |                             | 4. Implications of External I/O                    | 81   |  |  |  |

|     |                             | 3. Freeing a Storage Module Used as a Relay        | 85   |  |  |  |

|     |                             | 4. Summary of Storage Module Removal               | 87   |  |  |  |

|     | 3.                          | Adding a Storage Module                            | 88   |  |  |  |

|     | 4.                          | Removing a Processing Module                       | 90   |  |  |  |

|     | 5.                          | Adding a Processing Module                         |      |  |  |  |

|     | 6.                          | Summary of Changing Module Utilization             | 99   |  |  |  |

| 4.  | СНА                         | NGING THE HARDWARE CONFIGURATION                   | 101  |  |  |  |

| -•  | 0.                          | Dynamically Changing Physical Module Configuration |      |  |  |  |

|     | 1.                          |                                                    | 104  |  |  |  |

| SEC | TION |                                            | PAGE |  |

|-----|------|--------------------------------------------|------|--|

|     | 2.   | Changing Module Binding                    | 109  |  |

|     |      | 1. Storage Module Configuration            | 116  |  |

|     |      | 2. Processing Module Configuration         | 118  |  |

|     | 3.   | Partition-system Initialization            | 123  |  |

|     | 4.   | Review                                     | 125  |  |

| 5.  | THE  | MULTICS IMPLEMENTATION                     | 127  |  |

|     | 0.   | Background                                 | 127  |  |

|     | 1.   | Removing a CPU                             | 133  |  |

|     | 2.   | Adding a CPU                               | 139  |  |

|     | 3.   | Removing a Memory                          | 143  |  |

|     | 4.   | Adding a Memory                            | 148  |  |

|     | 5.   | Experience With the Multics Implementation | 150  |  |

| 6.  | CON  | CONCLUSIONS                                |      |  |

|     | 0.   | Summary of Results                         | 153  |  |

|     | 1.   | Implications                               | 154  |  |

|     |      | 1. Module Interchangeability               | 155  |  |

|     |      | 2. Operator Participation                  | 156  |  |

|     |      | 3. Automatic Configuration Control         | 156  |  |

|     |      | 4. Resource Utilization                    | 157  |  |

|     | 2.   | Additional Research                        | 158  |  |

|     | 3.   | Remarks                                    | 160  |  |

| SECTION   |     |                                                                  | PAGE |

|-----------|-----|------------------------------------------------------------------|------|

| BIBLIOGRA | ЪНХ |                                                                  | 161  |

| Appendix  | I   | <br>Multics Operator Instructions                                | 163  |

| Appencix  | II  | <br>Summary of Multics Supervisor Changes<br>For Reconfiguration | 170  |

| Appendix  | III | <br>Analysis of Current Hultics Hardware For Reconfiguration     | 174  |

| Appendix  | IV  | <br>Multics Hardware Design Proposal For Reconfiguration         | 183  |

# ILLUSTRATIONS

| FIGURE |                                                | PAGE |

|--------|------------------------------------------------|------|

| 2.1    | Fixed Configuration Resource Model             | 25   |

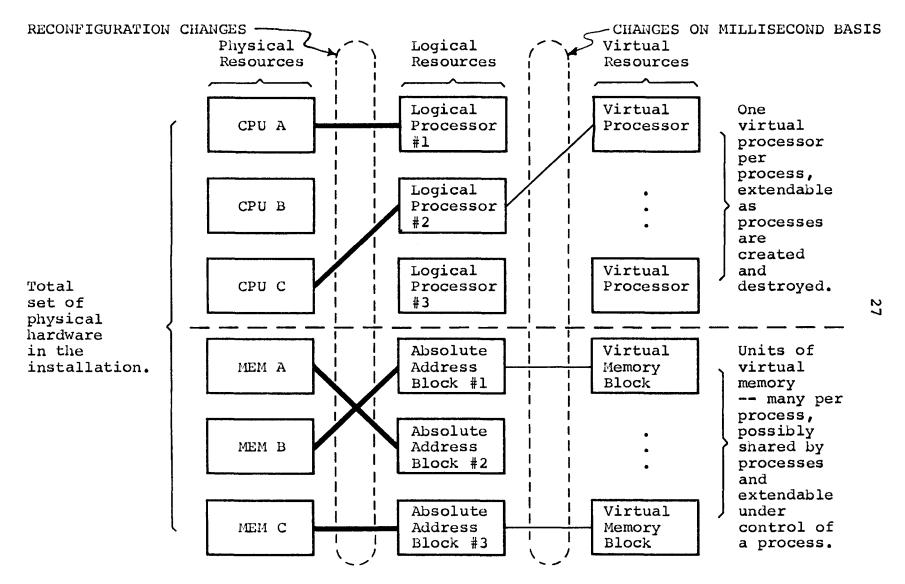

| 2.2    | Model of Resource Management                   | 27   |

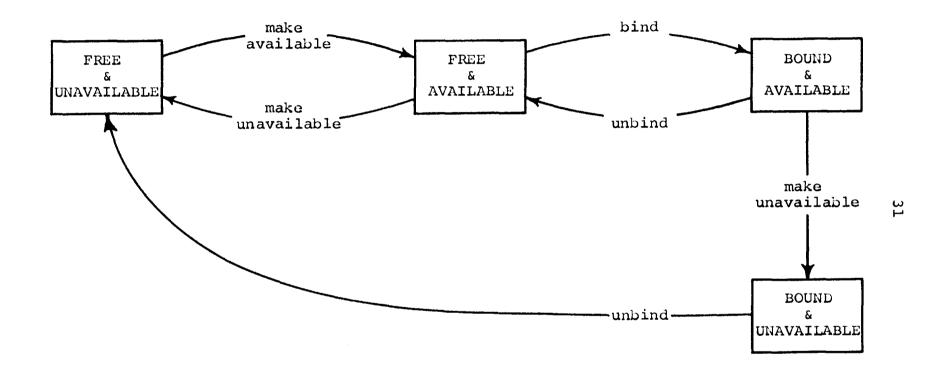

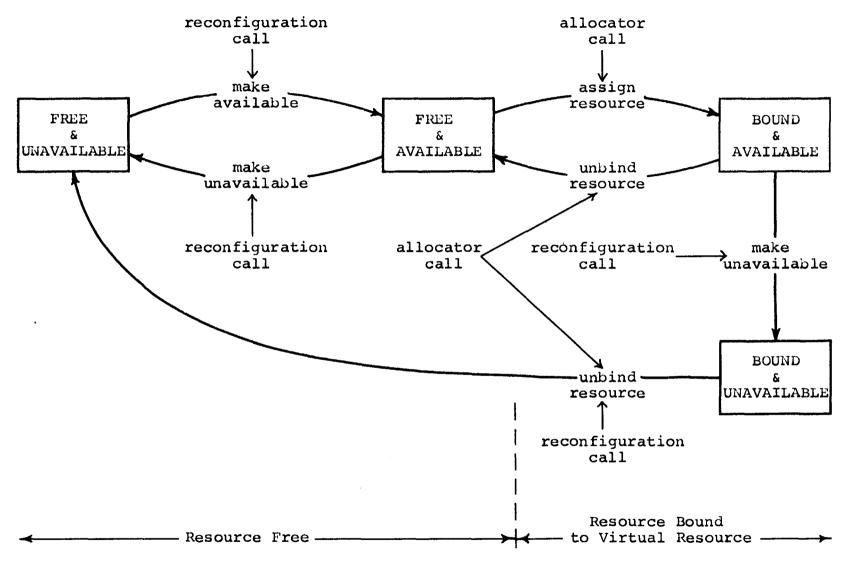

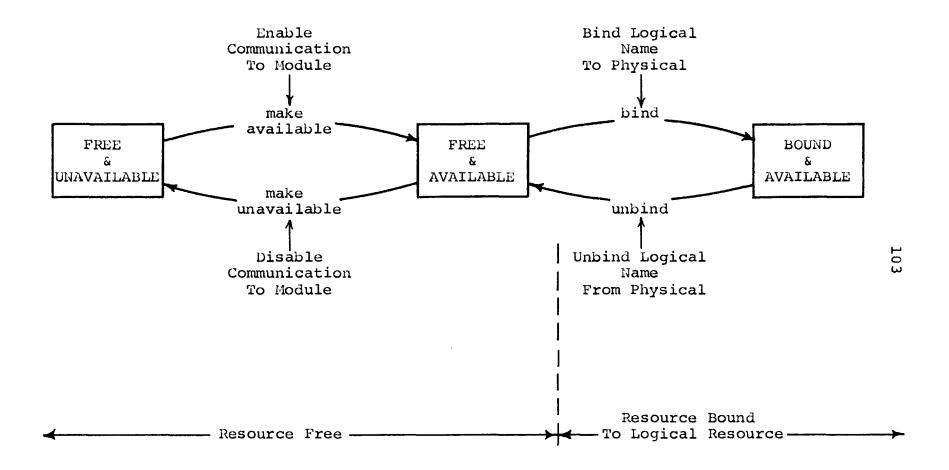

| 2.3    | Usage State Transitions                        | 31   |

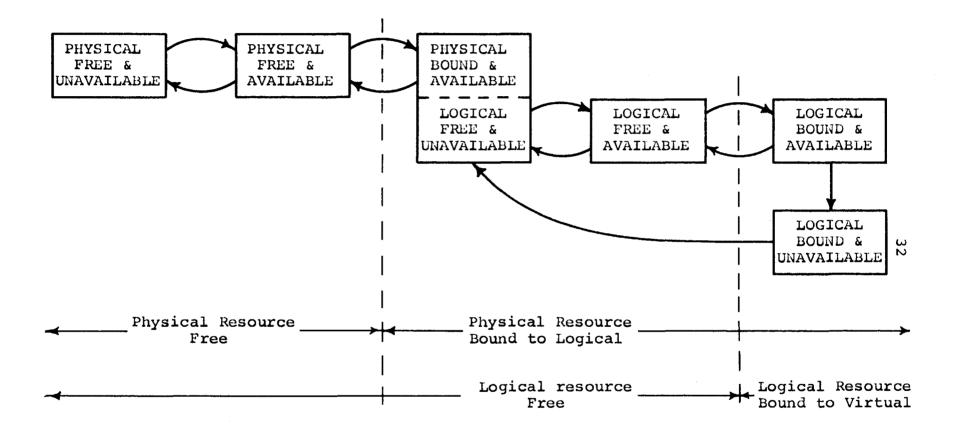

| 2.4    | Resource State Transitions for Reconfiguration | 32   |

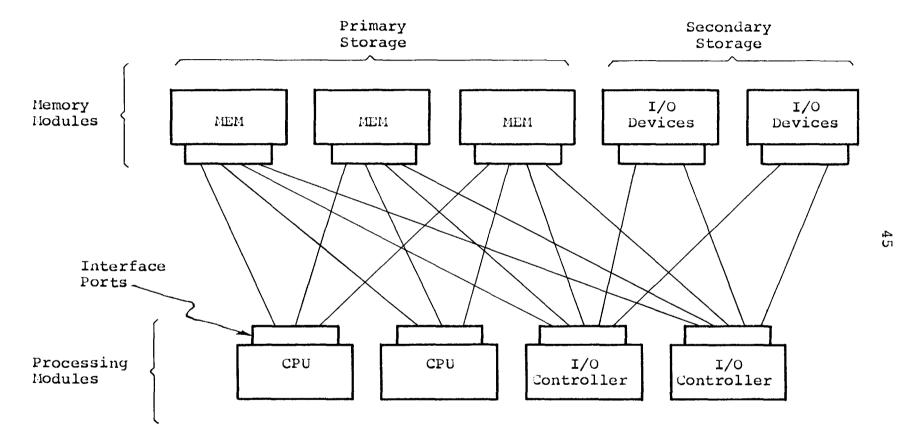

| 2.5    | Typical Module Interconnection Network         | 45   |

| 3.1    | Usage State Transitions of Logical Resources   | 49   |

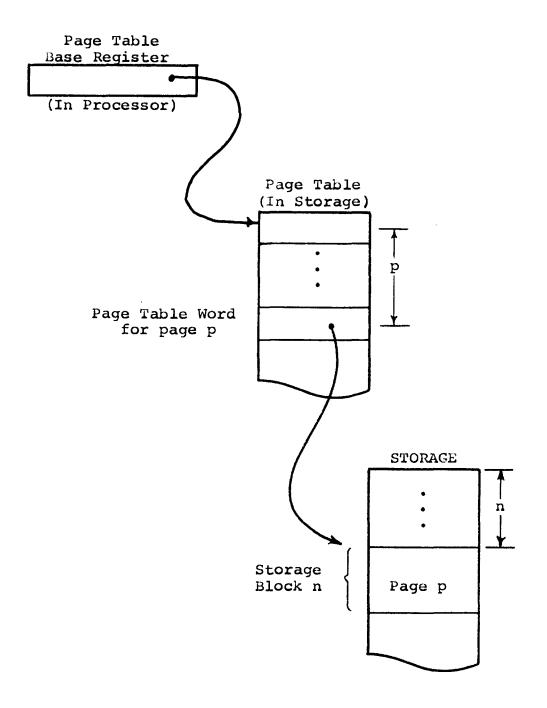

| 3.2    | Address Translation for Paging                 | 56   |

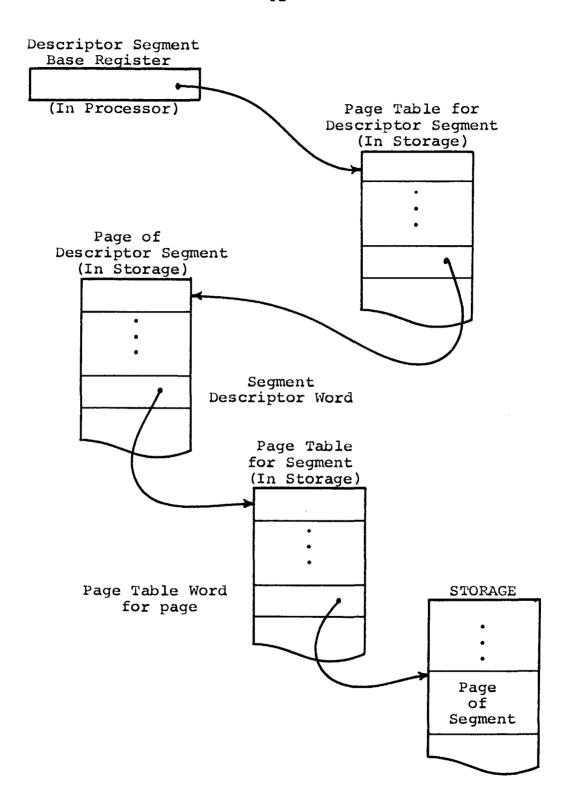

| 3.3    | Address Translation for Segmentation           | 62   |

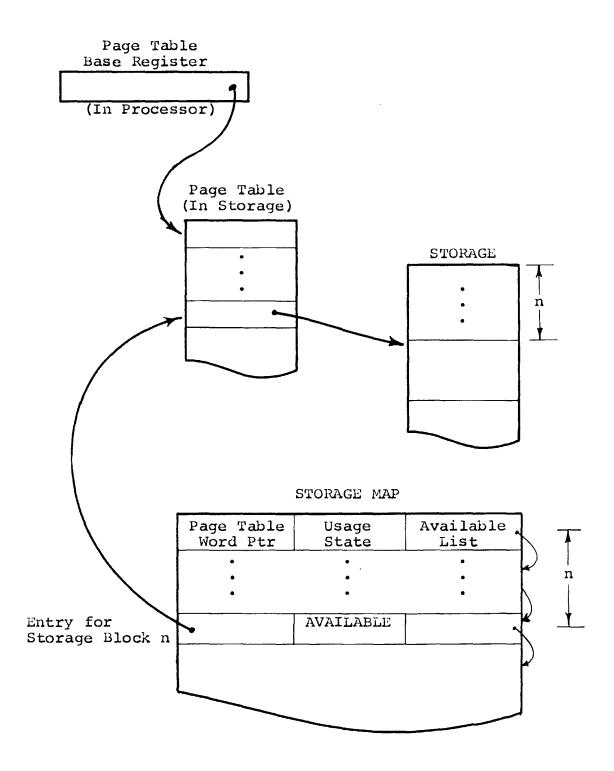

| 3.4    | Example of a Storage Map                       | 67   |

| 3.5    | Example of Making Storage Unavailable          | 68   |

| 3.6    | Environment for Moving Wired Storage           | 75   |

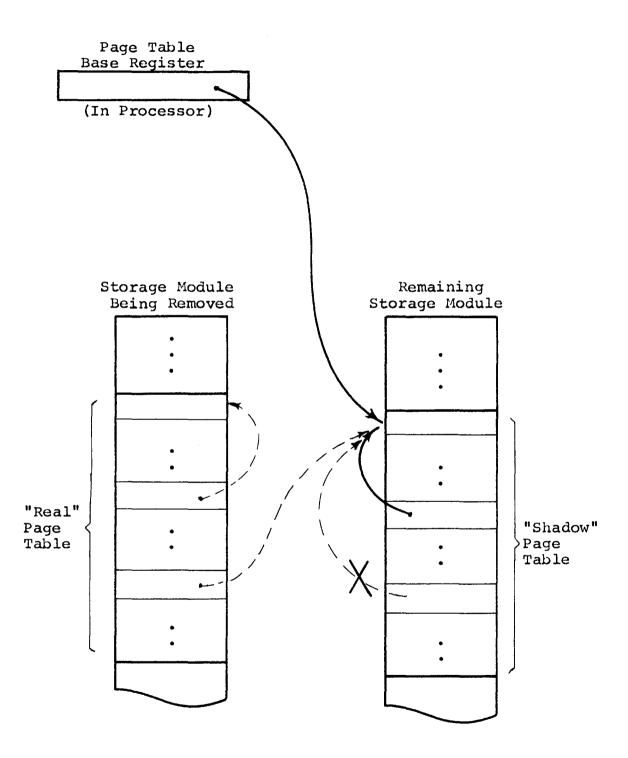

| 3.7    | Environment Before Relocating Page Table       | 82   |

| 3.8    | Environment After Relocating Page Table        | 83   |

| 4.1    | Usage State Transitions of Physical Resources  | 103  |

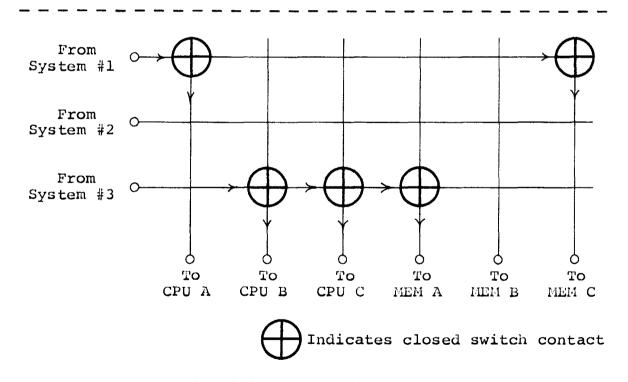

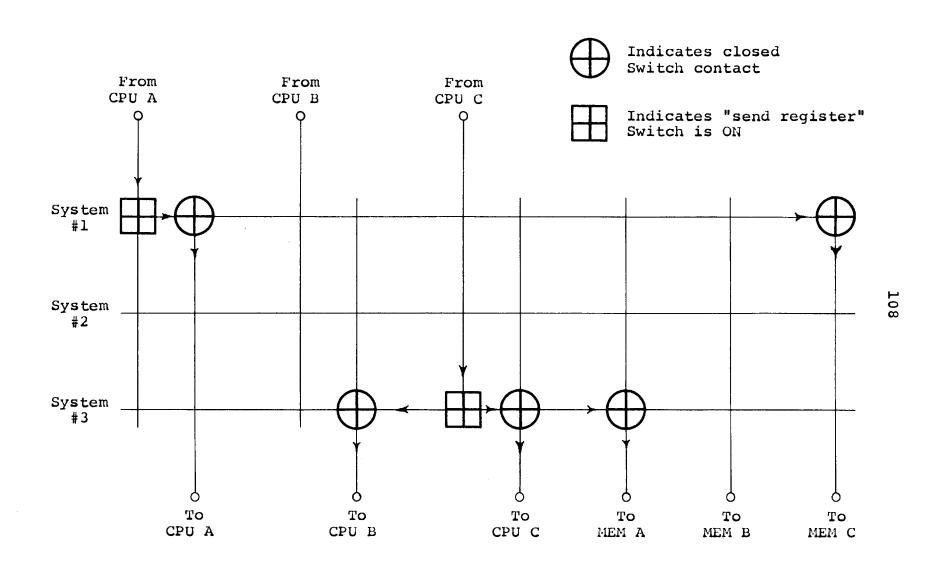

| 4.2    | Operator Interface Matrix                      | 106  |

| 4.3    | Operator Interface Matrix Schematic            | 108  |

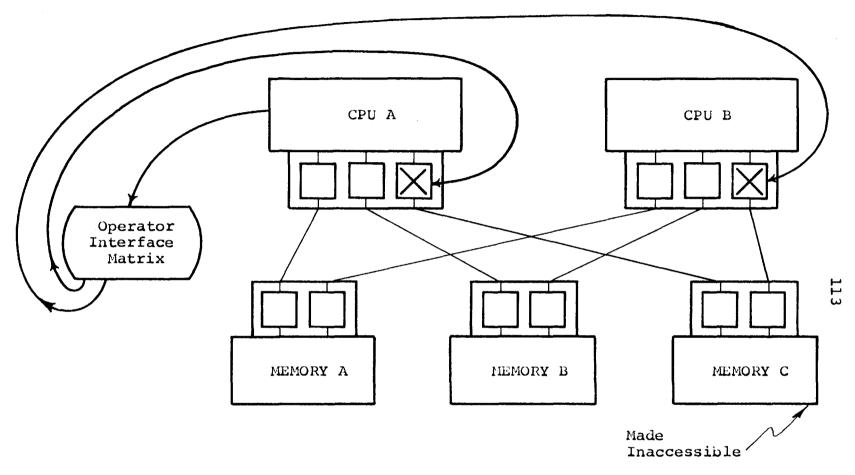

| 4.4    | Typical Intermodule Communication              | 112  |

| 4.5    | Disabling Intermodule Communication            | 113  |

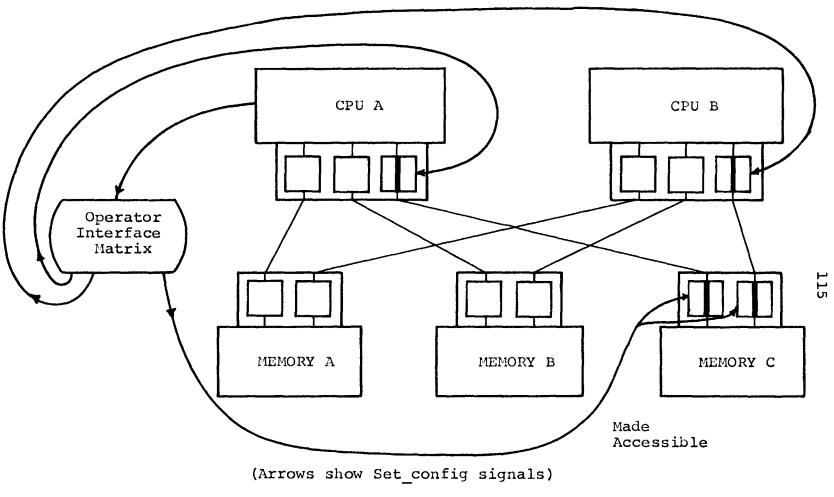

| 4.6    | Enabling Intermodule Communication             | 115  |

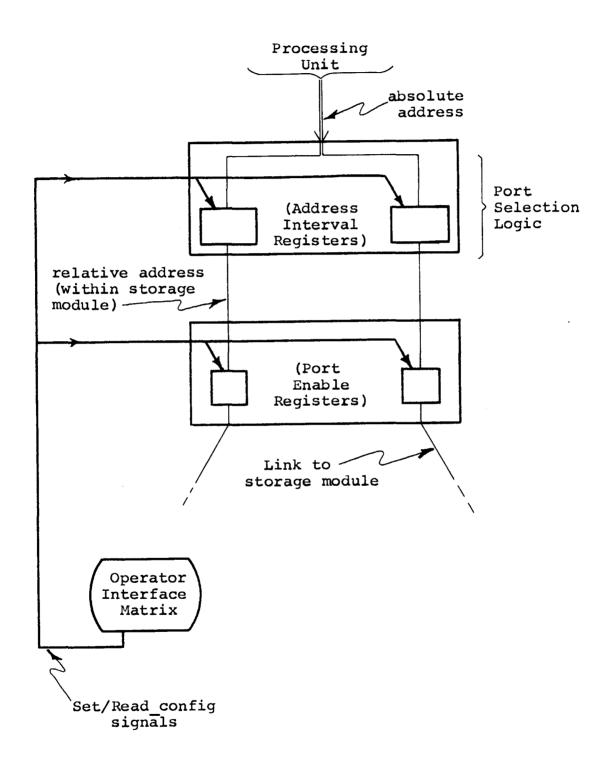

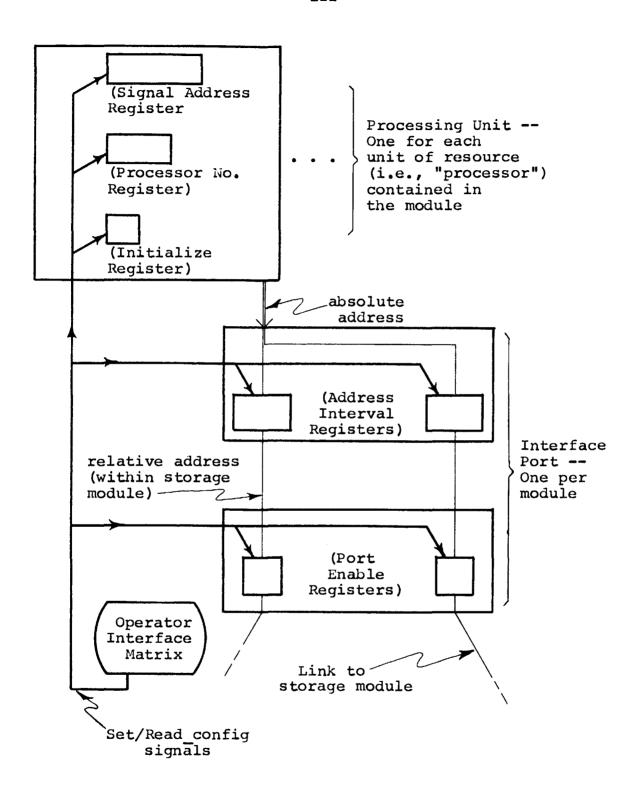

| 4.7    | Model of Processing Module Port                | 117  |

| 4.8    | Model of Processing Module                     | 121  |

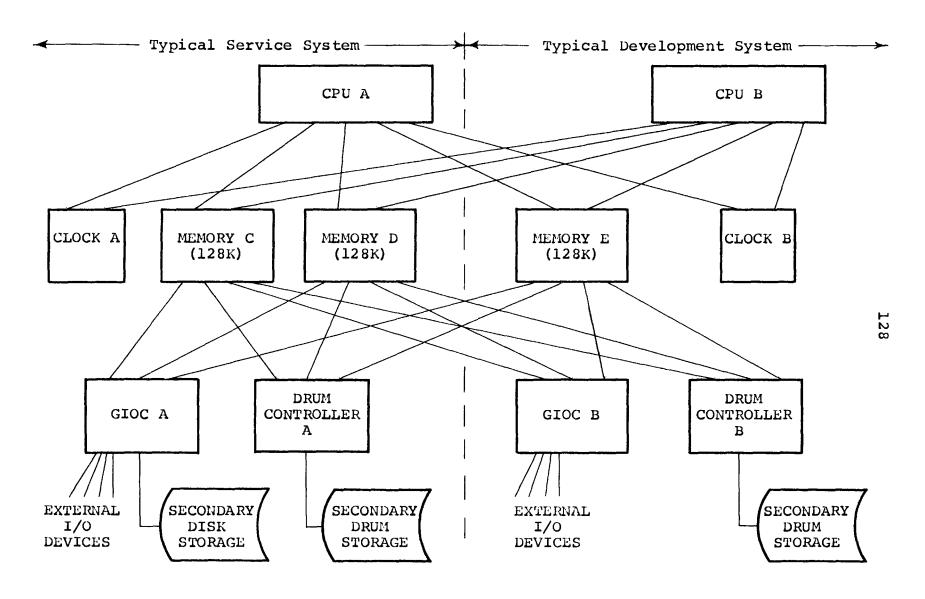

| 5.1    | Multics Hardware Installation                  | 128  |

#### CHAPTER ONE

### INTRODUCTION

# 1.0 Modular Computer Systems

The digital computer has evolved from a single processing unit dedicated to one sequential task at a time to the modern computer utility simultaneously serving many users. As the and complexity of computers have grown, a modular hardware design has commonly been employed. As with other utilities (such as electrical power and telephone services), the computer utility must be able to change its hardware configuration without disrupting the services provided. This thesis model of reconfiguration presents an abstract operations, and thus provides a discipline for designing operating systems and hardware modules for a computer utility so that the configuration of constituent modules can be dynamically changed. The research reported here also includes a practical processor and memory module reconfiguration capability for the Multics system [1] at MIT.

The complexity of a large computer has naturally led designers to view the system as being composed of a number of smaller modules. Not only is such a modular viewpoint indicated for purposes of system design and analysis, but also the practical problems of maintenance, operation and system evolution have made it desirable to construct large systems

from a small number of distinct types of physical modules. These individual types of physical modules typically reflect the primary functions of the design -- memory modules, processor modules, input/output channels and input/output devices are common examples. The total system is formed by interconnecting a collection of these modules in a particular configuration, and the quantity of each type of module determines the system capacity.

## 1.1 Statement of the Problem

This thesis considers basically the following design problem for reconfiguration in the modular computer system: provide an architecture for the modules and their interfaces and a design for the operating system that permits a computer operator to dynamically (viz., automatically and without interrupting the service provided to users of the system) add modules to and remove modules from the system. This design must be flexible enough to apply to all modules of a given type, and must minimize the potential for disastrous errors.

### 1.1.1 The Environment

The ability to dynamically modify the configuration of hardware modules in a computer system is primarily of interest where a large data processing capacity is required and where a high system availability is desired. Over the last few years

substantial work has been directed towards systems providing multible users easy access to common information. A <u>single</u>, high-capacity system is required to serve many users with common information. To serve many users effectively, the information (and thus the system) must be available on the demand of the user: this type of computer system has been referred to as a "computer utility".

As with other utilities, the computer utility must have substantially greater resources than those required by any one user. Furthermore, as with other utilities, the system must be able to, without becoming unavailable, withstand the removal of any module for maintenance. It is this need for a large, concentrated, continuously available computational capacity that underlies many of the more significant design features of a computer utility such as the Multics [1] system.

In the early development of digital computers, the need for more powerful machines was met by building faster machines with more storage capacity; however, as technological and economic limitations were approached, multiple units were used to increase capacity. For example, processor speeds are limited by the velocity of propagation and the physical dimensions between computational logic and the instruction storage medium; therefore, additional total capability is sought by including multiple processors in the system. Similarly, storage and input/output capabilities have been increased by the use of multiple modules.

An interconnection of various different of types computers can also provide an increased capacity; for example a small computer for reading cards and driving a printer can be connected to a larger computer for more compute-bound portions of a job. However, a single modular system with a number of each of a very few distinct types of modules reduces the complexity since there is only one operating system, provides a higher availability since only a few modules are required to provide a spare for every type of module, easily expands to a larger system since modules are merely added without removing the previous system, and is simpler to maintain due to the commonality between similar modules. Various commercial systems have used a modular interconnection scheme including the Univac 1108 Multi-processor System [2], the Burroughs D825 [3], the GE 635 [4], and the IBM 360 Model M65MP [5].

## 1.1.2 The Nature of the Problem

One problem is matching the demands of the load to the capacity of the system. The computer utility must always have enough capacity to provide a response within a few seconds, since people tend to stop working if they have to wait. To be fully effective the services must be continuously available, since the stored information must be accessible when the user wants it. Utilization efficiency would indicate that during

the greatest load, a major portion of the processing capacity (viz., essentially all the modules) would be used to meet customer demands, while during lighter loads it is desirable to remove unneeded modules.

Some of the objectives to be achieved by modifying the configuration are to reduce costs associated with operating the modules, forming an independent processing unit with some of the modules, allowing periodic and preventive maintenance to be performed, and reducing the amount of hardware in the system in order to decrease the probability of hardware failure, i.e., increase the reliability. These include the basic reconfiguration goals that were considered important for the Multics computer utility; these goals have been given elsewhere [6,7,8], but are briefly reviewed here:

- 1. An essential requirement is that the reconfiguration (addition or deletion) of a module be accomplished dynamically, i.e., rapidly and without disruption of the service provided.

- 2. The reconfiguration design should treat all identical modules in the same way -- for example, it should be possible to add or remove any primary memory module. Maintenance requirements can be expected to apply to every module, so no specific physical unit should be allowed to be indispensable, either by hardware constraint or software convention. Continuous service can only be approached by a reconfiguration design in which no single module is essential for continued

system operation.

3. It must be possible to partition the modules of the installation into separate noninterfering systems. These independent partition systems may be used for providing service to users, for development of changes to the operating system, or for maintenance testing of the hardware. This partitioning of modules should be possible without massive physical effort, such as changing of cable connections, which is slow and prone to errors.

In this thesis dynamic reconfiguration is considered as a response to a request from outside the system -- specifically a computer operator. Therefore, an important consideration is In particular, an operator should be the human interface. able to initiate a reconfiguration that is completed rapidly (within a few seconds) and automatically (without further operator intervention), and there should be no possibility for operator errors to cause disastrous results. This thesis will not address the more difficult problem of in response to an observed component reconfiguration (e.g., failure); however, the results presented here provide a basis for future research in this area.

For simplicity of design and implementation reconfiguration should be provided by applying the normal capabilities of the system whenever possible. The operator controlling reconfiguration should be just another user of the system who has been given the privilege of using the required

system primitives. The processing and storage overhead required when reconfiguration is not in progress should be minimal.

This thesis will explicitly consider only the modules that make up the central data processing capacity of the system. In particular, modules associated with input/output to devices external to the system itself are excluded. addition, it has been pointed out by Dennis [9] that modular interconnection schemes do not readily generalize to very large numbers (e.g., hundreds) of modules. However, practical systems for the present and foreseeable future can find a modular design very useful, since systems can reap the major benefits of simplicity, high availability, expandability, and commonality with quite a small number (e.g., a few tens) of modules -- clearly a few modules are enough when each module provides a significant portion of the total capacity. thesis will confine itself to such contemporary modular structures.

## 1.2 Background

As pointed out above, the importance of dynamic reconfiguration was clearly appreciated in developing the goals of Multics; however, the initial design did not include this capability, attesting to the non trivial nature of the problem. Although past systems have included (limited)

reconfiguration capabilities, a general solution has not previously been available.

A modular hardware organization is of course not new, and modular systems have frequently been applied to general The need to operate general purpose computational tasks. purpose systems with a variety of configurations has been widely recognized in the past. The manufacturer's description 360 Model 67 [10] points out that the duplex IBM configuration of this system can be partitioned into two isolated subsystems -manual switches and processor capabilities are provided for making part of the system unavailable for program control. Not only has the need for partitioning been previously recognized but also the need uniform treatment of similar modules has been considered. The GE 635 [4] and the IBM 360 Model 67 both include manual switches to provide "floating addressing", i.e., any memory module can be used for any required address interval, so that any memory module can have maintenance performed on it without disabling the entire system. It has also been noted that the ability to operate with various configurations of modules permits changing the system capacity to meet changing demands example, the manufacturer's description of the for Burroughs B6500 [11] points out the expansion capability implied by a modular structure.

Although systems have previously been developed to operate with a variety of configurations, a significant

interruption of service is usually required to change the configuration. In most cases the configuration is specified loading system on a raw machine, and prior to the reconfiguration is accomplished by essentially reloading with a new configuration. This was generally the operation of the initial Multics design. Limited reconfiguration capabilities have been provided for general purpose computer systems, most notably the IBM 360 Model M65MP [5]; however, without a general design model these systems have left unsolved some of the more difficult problems, such as removal of the memory modules containing the "resident supervisor".

Although dynamic reconfiguration is important for general purpose computer systems principally in the computer utility environment, special purpose systems have in the past used modular reconfiguration to enhance reliability. Although quite successful in their intended application, the design in these systems is so permeated with the peculiarities of the particular application and specific hardware that little general structure is evident.

A form of reconfiguration has been provided in special purpose systems using redundant modules. With this technique identical processing and storage functions of the system are simultaneously performed using separate physical modules — the reliability motivation is that if one module fails it can be removed from the configuration, and the results of a good duplicate module can still be used. An example of this type

of reconfiguration can be found in the Bell (Telephone) System Electronic Switching System [12]. Also the American Airlines' SABRE system [13] used duplicate (viz., on-line and standby) IBM 7090's, redundant I/O terminal interchanges, and multiple copies of vital records on storage modules in order to achieve the capability for rapid restart of the system with minimum risk of information loss in case of failures. Not only is it costly to provide duplicate hardware, but also this type of reconfiguration does not allow the capacity of the system to be dynamically changed.

Special purpose systems have also frequently used a "snapshot" reconfiguration technique that is not acceptable for the general purpose computer utility. Periodically a "snapshot" is made of a small amount of data from which all computations can be restarted. The system can then be stopped (destroying the computations in progress), the configuration changed, and the system restarted from the snapshot data. This technique requires a detailed knowledge of computation being performed, and requires that it acceptable to destroy a portion of the computation. A related technique takes advantage of a carefully designed cyclic behavior for the computation by changing the configuration only at a fixed point in the cycle where the computation can be continued from a small amount of saved data. On the other hand in a computer utility the user can specify computations whose nature is unknown to the system and for which any

disruption may be totally unacceptable.

This "snapshot" technique has been used in various command and control systems. The SAGE [14] air defense system, one of the earliest (about 1958) large scale computer systems, had an embryonic reconfiguration capability to obtain greater reliability: its "users" were approximately 100 operators at display consoles, and its vacuum tube central computer (logically a single "module") was duplexed so that when there was a hardware failure, the entire spare computer would be put on line to continue service to the "users" from a periodically saved snapshot. A backup to this system, known as BUIC [15], used the modular, transistorized Burrough D825 BUIC used online fault detection and an automatic modular reconfiguration capability to provide an operational failure rate much less than the inherent hardware failure rate.

One of the largest and most recent of these special purpose real-time systems is the IBM 9020 developed for the FAA air traffic control system, which gives attention to special hardware features to facilitate reconfiguration for increased reliability. Although these systems and others like demonstrate the key role of dynamic them serve to reconfiguration in approaching the goal of "continuous operation", the observation made for the IBM 9020 system places the specific achievements of this type of system in perspective: "It deserves emphasis that the multiprocessing system under discussion is application-oriented in the sense that many of its functional capabilities are designed to meet explicit requirements. It would be another matter to formulate such capabilities for a general purpose environment" [24].

# 1.3 Method of Presentation

A substantial portion of the research effort reported here has been directed towards the design and implementation of a dynamic reconfiguration capability for the "Multics" system (Multiplexed Information and Computing Service) at MIT. This early engineering design gives Multics the capability to dynamically add and remove central processing units and memory modules with no disruption to the users. These capabilities are regularly used in the normal operation of this system currently supports more than 50 simultaneous which time-sharing users. Although the author has found this experience invaluable in gaining insight and practical understanding of the issues involved, this thesis is not intended to be a description of a bag of programming tricks to arrive at a particular initial reconfiguration capability for Multics: the primary goal of the research has been to develop a design approach that can be applied to the evaluation of an existing system or the design of a new system where dynamic reconfiguration is desired. The successful

application of this orderly design approach to Multics demonstrates its viability, and specific examples are drawn from Multics to aid in the explanation of the design approach.

In chapter two we first develop a general model of reconfiguration -- the concept of binding is used to model the operations of reconfiguration. We show how this model can be interpreted in terms of contemporary modular computer systems.

Next the general model is used to develop a specific design procedure for an operating system and hardware architecture to provide reconfiguration. In chapter three we identify a design for the program oriented primitives required to dynamically change the set of modules actually being used by the operating system. Then in chapter four we develop a hardware oriented structure that allows dynamically changing the set of modules actually accessible to the system — this structure is directly influenced by the need for automatic reconfiguration, viz., without human operator participation.

Chapter five presents the experience with experimental Multics version of the ideas presented. the tradeoffs involved and the compromises required in the specific Multics implementation are presented. An appendix is also included that, based on the ideas of this thesis, proposes specific hardware design for an improved a reconfiguration capability for Multics.

### CHAPTER TWO

#### SYSTEM STRUCTURE

## 2.0 A General Model for Reconfiguration

A primary task of any computer system is to transform the capabilities of the hardware units into resources that can be used to perform desired computation for users of the system. The concept of binding, defined below, can be used to model the system functions which organize the raw hardware capabilities into a usable form. In this chapter such a model constructed and then augmented to provide a model of the reconfiguration operations. The model is used to identify the structure of computer systems for which reconfiguration as presented in this thesis is applicable, and it is shown that the architecture of contemporary modular computer systems is representable by this structure. In the following chapters the generalized model is used to develop a specific model of the individual functions needed for reconfiguration.

### 2.0.1 Resource Management Model

The model developed here is based on the observation by Dijkstra [17] and others that in a sequential process only the time succession of the various states has logical meaning, but not the actual speed with which the sequential process is performed. In particular to develop our model for

reconfiguration we use the concept of the state of a process represented as stored information which is subjected to functional transformations as a process proceeds. The view of computation as asynchronous does not completely represent real computer systems since synchronous computations also occur. However, for purposes of reconfiguration the operation of most computer systems is asynchronous enough that this view of a sequential process is adequate.

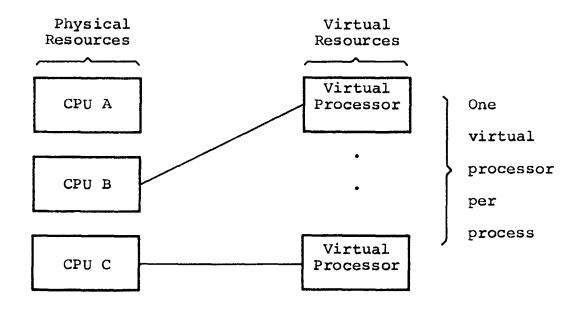

In the computer utility environment there may be a number of computations (i.e., processes) in progress at the same time, although at any instant in time many of these may not actually be executing on a hardware processor. However, since all the computations are in the long term view proceeding, each and every process can be considered as the execution of a program on a "virtual processor" with its instructions and data stored in a portion of a "virtual memory". These processor and memory resources required by a process will be termed virtual resources — virtual resources are used to model demands for actual processing and memory capability. At any point in time the set of virtual resources of all processes in the system represents the demand for system resources.

The actual processing and memory capability of the system is provided by some (usually fixed) configuration of <a href="physical resources">physical resources</a>, viz., hardware devices. Since a process can proceed only when the physical resources are actually

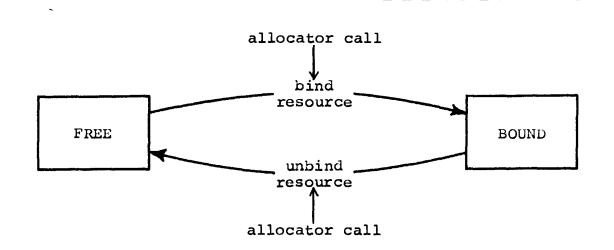

available to it, the system must include an allocator which assigns the available physical resources to meet the demands of the processes. If binding is considered as an operation of establishing a correspondence between objects, then in this model a primitive function of the allocator is to bind some subset of the virtual resources to physical resources: we define these resources to be in a bound state. The allocator also includes a primitive to unbind (typically on a millisecond basis) the available resources so they can be used to meet other demands. At any given time, a physical resource may not actually be bound to a virtual resource due to either the lack of demand or due to allocator transients: we define such resources to be in a <u>free</u> state. Figure 2.1 illustrates this model of resource management.

In the above model we have identified processing and memory capability with the actual hardware units. In a real system a given hardware unit represents a useful resource only when electrically connected to other hardware units of the system in a known way. In studying reconfiguration of resources we must consider such connections in some detail; therefore, we explicitly distinguish between a physical component and the capability actually available from it. Furthermore, we introduce the notion of logical resources to represent the abstract processing and memory capacity. It is logical resources that are managed by the allocator. For each available logical resource there must be some physical

Lines show binding that exists -- changed on millisecond basis by allocator

Example of Resource Allocation

State Transitions of an Available Resource

Figure 2.1 -- Fixed Configuration Resource Model

resource, viz., a hardware device. The binding of the logical resources to the physical resources represents what is commonly called the configuration of the system: it changes only through reconfiguration. With this model, hardware capabilities being applied to a process are represented by physical resources bound to logical resources which are in turn bound to virtual resources of the process.

At this point a few observations can be made about binding as a model of the system's resource management. redraw the resource allocation illustration of Figure 2.1 to take into account logical resources -- Figure 2.2 indicates the relationships that can exist between physical, logical and virtual resources. This shows the simplified case where each hardware unit contains a single unit of resource -- in Multics parlance, when each memory module can store only a single page "binding" of information. In this context refers establishing a mapping or correspondence between the names of physical and logical resources and of logical and virtual resources. The total set of physical resources is determined by the physical hardware present in the installation. physical resource has a name used (for example by a human operator) to identify the specific hardware: a central processing unit is an example of a physical resource. A subset of the physical resources is included in any given configuration, i.e., is bound to logical resources. physical components are electrically interconnected so that

Figure 2.2 -- Model of Resource Management

their capabilities are accessible to the system.

The total set of logical resources is determined by the set of permissible names. For example, an absolute address is a name for a logical memory resource — the total set of logical memory resources in the system is determined by the range of absolute addresses provided in the design. The computation capacity available to meet the demands represented by virtual resources is modeled by those logical resources bound to physical resources in the configuration. A subset of these available logical resources is actually bound to virtual resources and the remainder is free to be used for future allocation. The current set of virtual resources (i.e., demands for resources) changes dynamically as processes proceed with their computation.

In the above model, the state of resource management for the system at any point in time is represented by physical resources bound to logical resources and logical resources bound to virtual resources. This model is sufficiently general that, with an appropriate interpretation, it can represent a wide variety of computer systems. Next this model will be used to consider the problem of reconfiguration.

## 2.0.2 Reconfiguration Model

In the typical computer system the configuration (represented here as the binding of physical resources to

logical resources) is established during the initialization of system operation and remains fixed until the system is shutdown and reinitialized with a new configuration. In contrast, dynamic reconfiguration is the adding and removing of physical resources while the system is running, and the model developed above allows us to view binding as the central issue in reconfiguration. In particular, the problem of removing physical resources from the configuration concerns the reversibility of binding, and adding physical resources to the configuration is an example of delayed binding.

We have previously observed that physical and logical resources can be either bound or free. When reconfiguration is introduced we need the notion of available and the inverse, We will introduce this concept in terms of the unavailable. operations of the allocator on logical resources. In our model, any logical resource bound to a physical resource is accessible to the system; with a static configuration all these logical resources are available to the allocator and may be either bound or free. All logical resources not bound to physical resources are unavailable to the allocator, and they must be free, since clearly they cannot be used to meet resource demands. To add logical resources at reconfiguration time, an unavailable (and thus free) resource is made available. To remove an available logical resource (which may be either bound or free), it must be made both unavailable and free. If we attempt to insure that the resource is free

before making it unavailable, we can have a race condition with the normal allocator functions asynchronously attempting to bind free resources; therefore, we make the resource unavailable for future allocation before insuring that it is free. Now the state transitions shown in Figure 2.1 can be redrawn in Figure 2.3 to include the resource usage state transitions introduced by reconfiguration.

These state transitions can be applied to physical well as logical resources. For a physical resource the usage state reflects binding to a logical resource. A physical resource is available when the system is able to change its binding to logical resources. An available physical resource is bound when it is associated with the name of a logical resource. Since the is changed only state through reconfiguration, race conditions can occur only if there are simultaneously executing reconfiguration routines. For example, a system spontaneously adding free modules to meet a peak in load could race with an operator trying to remove a specific module; however, recall that in this thesis we are considering only (strictly sequential) operator initiated Therefore, for physical resources we can reconfiguration. omit the "bound and unavailable" state added in the previous discussion of logical resources.

The relationship between physical resources and logical resources is illustrated in Figure 2.4, which shows all the resource state transitions that are involved in dynamic

Figure 2.3 -- Usage State Transitions

Figure 2.4 -- Resource State Transitions for Reconfiguration

reconfiguration. State transitions for a logical resource are defined only when there is an available physical resource bound to this logical resource, as illustrated in Figure 2.4 by a single state for both "physical bound and available" and "logical free and unavailable".

Based on the model that has been developed we can identify the primitive reconfiguration operations required to change the usage states when <u>removing</u> a resource from the system. The following sequence of steps is required:

- 1. The corresponding logical resource is removed from the set of logical resources available to the allocator for future binding to virtual resources.

- 2. The logical resource is made free by removing any existing binding to a virtual resource.

- 3. The physical resource is made free by removing the binding to the (free) logical resource.

- 4. The physical resource is made unavailable for binding to logical resources.

When a physical resource is added to the configuration the corresponding logical resource is initially free. The following sequence of steps is required to <a href="mailto:add">add</a> a physical resource:

- 1. The physical resource is made available for binding to logical resources.

- 2. The physical resource is bound to a logical resource not currently available to the allocator.

- 3. This logical resource is added to the set of logical resources available to the allocator for binding to virtual resources, viz., is added as a free and available logical resource.

- 4. The system then binds the logical resource to virtual resources as a result of the normal operation of the allocator.

We have now developed a complete model for all the reconfiguration operations. In chapter three and four this simple model will be applied in detail to, respectively, logical and physical resources.

## 2.0.3 Design Approach for Reconfiguration

Throughout this thesis reconfiguration is viewed changes in binding. This view of reconfiguration allows us to general form of a design procedure for recognize the implementing dynamic reconfiguration. First, it is clear that reconfiguration is directly related to the design of the allocator for the resources to be reconfigured. For reasons reconfiguration, substantial research other than has previously been done in the area of allocating a computer of user system's logical resources to meet the demands processes; therefore, when applicable, currently available technology will be summarized rather than reinvented.

We will now define allocator primitives to implement the

logical resource state transitions that have been identified. First, the allocator must have primitives which can be invoked to add and remove elements from the set of available logical resources being managed by the allocator. This means, of course, that the allocator must be able to properly manage changing amounts of resources, although there may be bounds on the allowable size of the set of resources, e.g., a system with no processor will probably not work at all. Using the notation of the PL/I language, we introduce these allocator primitives as generic closed subroutines of the operating system:

call Make available (resource);

call Make unavailable (resource);

where "resource" is the name of the unit of logical resource affected. These primitives affect the binding of logical resources to virtual resources that can occur in the future, but they do not change the current state of resource binding.

In addition, the allocator needs a primitive for freeing logical resources. For reconfiguration to be dynamic it must not disrupt (viz., change the outcome of) user processes, and the change in configuration must be completed in a period of time that is responsive to an operator request (viz., on the order of a few seconds). If the system can assure that a logical resource will be made free within a short period of time, then when removing a resource it is satisfactory to merely wait until the resource is free. In the more usual

unbinding physical resources. While computer programs provide the allocator functions, the availability and binding state of physical resources is a model for the more hardware oriented mechanisms that establish electrical connections between the physical hardware components of the system. In systems not operator dynamic reconfiguration, an typically accomplishes such connections by switches and cable connectors which cannot be changed without disrupting the computations in progress. For dynamic reconfiguration the system invokes primitives that, without disrupting user computations, change the connections between hardware units. Chapter four will consider in detail the primitive functions needed to change the configuration of the system.

We have identified the primitive functions necessary to provide a dynamic reconfiguration capability for a computer system. Although the model just presented did not explicitly distinguish between the various elements of resource, in a typical contemporary computer system there are clearly distinct classes of resources, e.g., processors and memories. The remainder of this chapter is primarily devoted to making those distinctions relevant to modular reconfiguration.

# 2.1 Modular Characteristics of System

As indicated in chapter one we are primarily concerned with computer systems composed of distinct physical modules.

From the viewpoint of reconfiguration, a "module" is a subset of the physical resources of the system which comprise an identifiable hardware unit. To reconfigure a module, all the physical resources comprising the module are added or removed using the design just outlined in the preceding section.

For convenience we assume that a module contains an integral number of units of physical resource. This approach is further suggested by the observation that nearly all contemporary modular computer systems are designed in this way, with each unit of physical resource in a single module, as illustrated by the store protection blocks of the IBM 360 series [18] and the memory pages of the GE-645 [19].

significance of this modular constraint is illustrated by an example from Multics. Primary memory allocated in blocks of 1024 words. A hardware core memory unit has a capacity that is a multiple of 1024 words and is usually considered as a module. However, in an attempt to reduce conflicts between multiple devices simultaneously referencing the same physical memory, it is possible to interlace two or four of these memories -- with interlace, consecutive double word addresses are located in different physical memories. This means that a single unit of resource (viz., a 1024 word block) is contained in more than one memory; therefore, for purposes of reconfiguration the set of interlaced memories must be considered as a single module, and these memories can be added to or removed from the

configuration only as a single entity. If individual memories are to be reconfigured when interlace is needed, then the interlace feature should be designed so that only locations within a single memory are interlaced.

module is reconfigured by individually reconfiguring each of its component physical resources, no loss of generality results from assuming that a module contains only a single type of resource. It is also observed that many contemporary systems are designed with such homogeneous modules -- for instance the IBM 360 Model 67 [10], the GE-635 [4] and the Burroughs Model B6500 [11]. This assumption allows a computer system to be viewed as an interconnection of processing and storage modules, which convenient for considering reconfiguration.

### 2.1.1 Processing Modules

A processing module primarily performs functional transformations on data stored external to the module. Therefore, a processing module must be able to read its instructions and/or data from and write its results into external storage in the system. At any point in time a processing resource is executing in behalf of only one process—the process to which the system has allocated this resource is moving through a time succession of states as a result of the transformations being performed. The state of this

process is represented by information stored in two places: data stored internal to the processing module (e.g., in registers) and data stored externally. We will assume (as is typical of contemporary processing hardware) that, conditional only on explicit locks, it is always assured that the internal data are of importance only to the process currently executing.

This model of a processing module is easily understood as a representation of the typical central processing unit (CPU) of a computer system. However, most computer systems have other devices manipulating stored information that can also be considered as processing modules. The most common examples are channels used to access storage managed by the system, such as magnetic disks or drums used for on-line storage. his discussion of traffic control Saltzer [20] has noted that a channel is really nothing more than a simple processor with a wired-in program. However, recall that channels with interfaces outside the direct control of the system (viz., "source" and "sink" input/output) are not specifically considered in this thesis.

# 2.1.2 Memory Modules

A memory module provides some physical medium for the storage of data that is used by the processing modules of the system, and it is required that memory modules never modify stored data. A significant characteristic of a memory module is that it may often be referenced in parallel by multiple processing modules, and uncoordinated data references can potentially produce conflicts. The reconfiguration primitives must provide for avoiding any additional potential conflicts which they introduce.

Primary storage contains information which must always be accessible to some processing module, in particular some instruction or command that can be referenced to control the next processing action. This information is commonly termed the "resident supervisor" or "wired down" programs and data. Primary memory is usually provided by a relatively fast, random access storage medium such as core or semiconductor memory: due to relatively high cost primary memory can usually meet only a small portion of the total demand for storage.

Potential conflicts in primary memory are often avoided by providing areas reserved for use by a single processing module. Since there may be no system primitives to prevent conflicting access to primary memory, reconfiguration primitives may require additional mechanisms to prevent conflict. For instance, when removing primary memory, reconfiguration primitives will be required to copy (and therefore access) all the information in a memory module -- including that reserved for use by other processing modules.

The memory of the system that does not require immediate

access is generally known as <u>secondary</u> storage, and is typically provided by slow, high capacity devices such as rotating magnetic disks and drums or even magnetic tape. The significant implication for reconfiguration is that a system will typically have storage allocator primitives to move data to and from secondary storage without risking conflicts.

# 2.2 Structure for Intermodule Communication

Although the total computation capacity of a modular system is provided by a collection of processing and storage modules, it is clear that the system design must include an interconnection network to satisfy the requirements for communication between the modules. This network is of direct concern to reconfiguration since communication paths between modules reflect the binding between the physical resources contained in the module and logical resources of the system.

Rather than dilute the discussion by considering each basic idea in terms of many possible structures, a general form for the interconnection network will be developed here and used throughout this thesis. This structure of communication links between modules, and ports to provide an interface between these links and the individual modules, is representative of contemporary modular systems.

#### 2.2.1 Intermodule Links

Intermodule links are required between modules that need communicate with each other. It. is clear that, for transfer of data, every memory module must have a link to at least one processing module and every processing module must have a link to at least one memory module. Since a module is completely passive, there is no need for communication between memory modules. However, communication is needed between processing modules. Common examples are the use of interrupts for signals from a channel to a central processing unit, and a central processing unit issuing commands to a channel. In addition, interrupts are often used control the allocation of processing resources (viz., for traffic control), as examined in detail by Saltzer [20].

A direct link could be provided for communication between processing modules. However, in some systems (Multics in particular) a memory module is used to relay signals, using the processing/memory link. One motivation for such a structure, with links only between processing and memory modules, is that the total number of links is reduced. In addition, by using a memory module for a relay, signals can easily be broadcast to multiple processing modules -- say to permit a channel interrupt to be processed by the first CPU that is available, thus giving the fastest possible response to the interrupt signal.

#### 2.2.2 Module Interface Ports

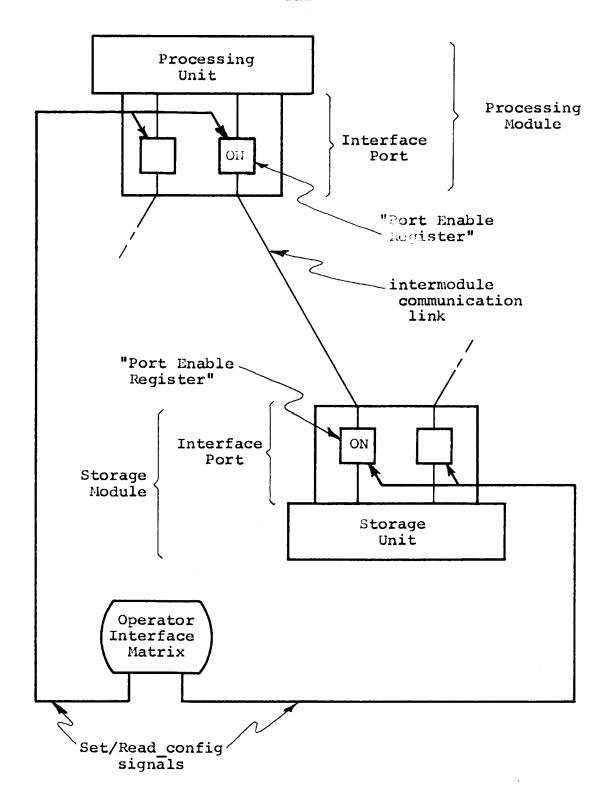

The links between modules can be thought of as the data transmission paths between modules. To complete the interconnection network there must be a "port" which provides an interface between each link and the physical resources within the module. Figure 2.5 shows a typical modular system that reflects this interconnection network structure.

As we have seen, a processing module must make references to external storage for instructions and data. For each reference, the port of the processing module uses some "selection logic" to map an absolute address for the desired type of storage (viz., a reference to a logical resource) into a reference through a link to a particular storage module and a particular location within that module (viz., a reference to a physical resource). In addition the processing module port must be able to send and receive signals for communication with other processing modules. In chapter four we will examine specific alternatives for the implementation of a processing module port.

The port for each storage module will respond to references from processing modules. The storage module port will receive over a communication link commands to read/write and will receive the corresponding address within the module: data that are to be read/written will also be passed over the link. In addition, the port must receive commands which cause

(Lines represent intermodule communication links)

Figure 2.5 -- Typical Module Interconnection Network

signals to be relayed to processing modules (e.g., send an interrupt or mask an interrupt).

Although we have developed a structure representative of current modular computer technology, it is pointed out that this structure has only been applied to systems with something in the order of ten modules. Because of the communication network "crossbar" problem it is doubtful if this structure would be effective for more than a few tens of modules in a system, and this thesis will not attempt to develop new structures for a larger number of modules.

# 2.3 Summary of System Structure for Reconfiguration

We have, in this chapter, used changes in binding between physical, logical. virtual and resources to model reconfiguration. Based on this model we have identified the computer system structure for which this thesis will consider the problem of dynamic modular reconfiguration. considered a computer system as made up of a collection of physical modules (each containing an integral number of units of processing and storage resources) interconnected by a communication network of links and interface ports. This framework has been developed so that the following chapters will have a firm conceptual foundation on which to build detailed solutions to the particular problems of dynamically adding modules to and removing modules to modules from a

computer system.

#### CHAPTER THREE

#### CHANGING MODULE UTILIZATION

# 3.0 Dynamically Changing Resource Usage

In this chapter we assume a static hardware configuration and make a detailed study of how to dynamically change the resources the system is actually using; we defer until the next chapter the problems of changing the hardware configuration. The usual operating system has initialization phase during which the processing and storage modules used by the system are established by operator inputs and system conventions (e.g., assuming a zero-based contiguous range of absolute core addresses). We will now examine in detail how the system can stop using a module currently in use and start using an additional module without reinitializing the entire system.

In terms of the model introduced in chapter two, we must basically develop a design for changing the usage state of logical resources. Figure 3.1 illustrates the operations that are required -- notice that this is just the specific instance for logical resources of the state transitions presented in chapter two (Figure 2.3). In this chapter we develop specific reconfiguration primitives for the storage resource allocator and processing resource manager, viz., the traffic controller. We first clearly identify the critical properties that,

Figure 3.1 -- Usage State Transitions of Logical Resources

regardless of reconfiguration capabilities, we expect to find.

Then the reconfiguration primitives are presented in terms of closed subroutines and system-wide data bases.

# 3.1 Storage Resource Management Environment

The purpose of this section is to provide a fairly extensive review of the technology currently available for storage management. This review focuses on those features which tend to solve storage reconfiguration problems.

The strategy used to manage the use of storage resources has a significant impact on the feasibility of reconfiguration -- particularly on the ability to remove a storage module. Removing a storage module removes some range of absolute addresses (which are modeled as logical resources) from use, and the system must provide, in some other module, a valid copy of the stored information. A basic problem is insuring that all references to this information are directed to the new location. We will consider some common examples of (primary) memory management to illustrate the storage allocator characteristics important for reconfiguration. To identify the intrinsic problems we first assume an unbounded amount of available primary memory, and then we consider the technological problems introduced when there is a limited

storage capacity.

### 3.1.1 Allocation With Unlimited Storage Capacity

First we examine one of the simplest examples of storage management — the textbook batch processing system. The system loads a program into a contiguous block of primary memory at a known absolute address, and binds all relocatable addresses to the absolute addresses that resulted from loading: typically the program is modified by inserting the required absolute addresses. We now consider the problem of removing the primary memory module containing this program, after this program has begun execution.

One might naively think that the necessary steps are merely interrupting the execution, moving the instructions and data by some increment of absolute address to a new location, execution. Obviously the absolute restarting the addresses originally generated by the binder are going to be incorrect; on the other hand, since the binder initially found where absolute addresses were needed, the system should now be able to go back and add to these addresses the appropriate address increment. However, the previous execution may also stored addresses elsewhere as data (e.g., return points for subroutine calls) for future use. Thus we conclude that the system needs a method for causing the absolute address of all future memory references to be incremented by the amount the program was moved. To do this the operating system must be able to locate and modify every occurrence of a stored absolute address that may be used in the future.

We need not invent methods of doing this since various relocation techniques have already been developed for reasons other than reconfiguration. Multiprogrammed batch processing systems provide a common example. These systems are designed to execute one program until the process cannot proceed (e.g., until the process must wait for some input/output operation), and then switch the processor to the execution of some other process that is able to proceed. To this end, the system loads more than one program into primary memory at once and chooses the "best" one to run. If one program waits for a long time (for example while an operator locates and mounts a magnetic tape) then for efficiency the system may unload this program from storage so some other program can be loaded; however, when ready to continue the execution the same block of memory may not be available, so the system must relocate the program to a different absolute address in core. One way to accomplish this relocation is with a relocation base register in the processor hardware: all addresses generated for instruction fetches and data are relative to relocation base. The addresses appearing in the program are longer absolute addresses but are virtual addresses -- the relocation base register provides an address mapping that binds virtual addresses to absolute addresses.

We note that the relocation base register is the <u>only</u> memory of any absolute address in the system, and therefore in terms of our model completely specifies the binding of virtual storage resources to logical storage resources (named by absolute addresses). The system can relocate an executing program by the following steps:

- 1. Stop the execution of the program so that the data and instructions in this block of memory will not be accessed, viz., stop the progress of the process so its state will not change.

- 2. Make a copy of the block of instructions and data at a new absolute address outside the memory module being removed.

- 3. Reset the relocation base register to reflect the address of the new copy.

- 4. Resume the execution of the program, viz., continue the progress of the process from this new state which is equivalent to the state when it was interrupted.

### 3.1.2 The Storage Utilization Problem

So far we have seen that the intrinsic problem in removing a storage module is <u>reversing the binding</u> of a virtual address to an absolute address, and then binding to a new absolute address -- in the example, the relocation base register provides this ability. Although the basic issue has

memory the system assigns the number of storage blocks required. These blocks may not be contiguous even though the virtual addresses in the corresponding pages of the program are.

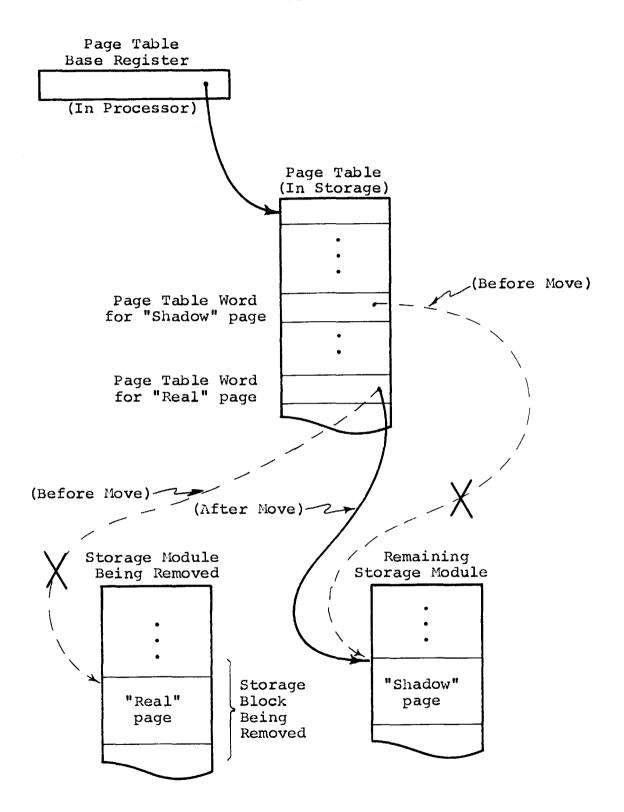

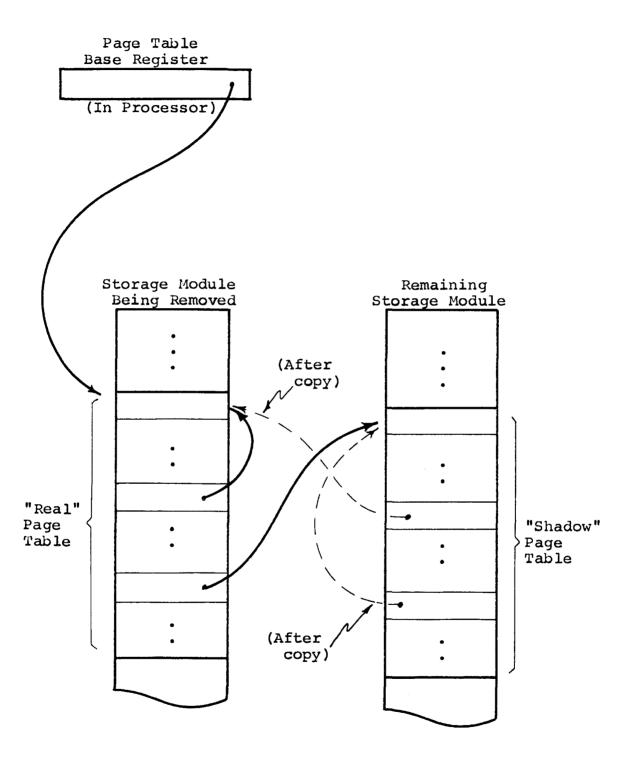

The processor requires a page table accessed by page number that gives the absolute address of the corresponding block of storage (typically the page size is a power of that the page number consists of some high order bits of each virtual address). Each page table word provides a mapping virtual addresses in that page to of addresses in exactly the same manner that the relocation base register did. The page table may itself be located in storage if the processor has a page table base register containing the page table's absolute address. For each instruction fetch or data reference the processor consults the appropriate page table word to arrive at the correct absolute address. Figure 3.2 illustrates the address translation for paging. The system can remove a memory module by making a copy of just the pages stored in it: the page table word for each page moved (rather than just the value of a single relocation base register) must be updated to the new absolute address. emphasized that paging is not essential again reconfiguration; however, for simplicity we will continue to use paging to decouple the problem of storage utilization, allowing a clearer view of the basic issues

Figure 3.2 -- Address Translation for Paging

reconfiguration.

### 3.1.3 The Effect of Limited Storage Capacity

Although paging answers the technological problems of storage utilization, there remains the problem of limited storage capacity. Similar modules may not have adequate storage for a copy of the information in the module being Again we note that similar problems exist and have been solved for reasons not related to reconfiguration. Recall that in our earlier discussion of multiprogrammed batch systems, when a program not yet in primary storage was ready to run, the operating system could get space for it by unloading some other program currently in primary storage but not able to continue execution. Implicit in this is the existence of what we have called secondary storage modules (typically magnetic drums or disks) which have adequate room for copies of the programs "in progress" whose execution has been interrupted. Similarly, to remove a primary memory module the system can either unload programs in the module or unload programs from other modules to make room for a copy of the information from the module being removed.

Where paging is used, reconfiguration can benefit from the technique of <u>demand</u> <u>paging</u>. In a system with demand paging, an entire program is not necessarily loaded at once, but the storage allocator loads only selected pages. One

common design has a "fault tag" in each page table word without a valid absolute address (viz., the page is missing in primary storage). Any attempt by the processor to reference a "missing page" will cause a hardware fault. As a result of the fault, the allocator retrieves the page from secondary storage, places the absolute address in the page table word, removes the "fault tag", and then allows the execution to If no free storage block is available, then the continue. allocator copies some page currently in primary storage (for example the least recently used page) to secondary storage, so its storage block can be allocated to meet the new demand. Similarly when removing primary memory, demand paging provides a tool for pushing out excess pages so that the number of pages in primary memory does not exceed the storage left after removing the module. Thus the basic solution to the problem of limited primary storage capacity is moving information to secondary storage modules, and a storage allocator with demand paging can make this easier. Secondary storage must, of course, have enough capacity to hold the information moved from primary storage.

### 3.1.4 The Storage Allocator

Recall that the objective of the above discussion of storage allocator designs has been to identify characteristics that are relevant to reconfiguration. This has been motivated

by a desire to benefit from the existing state of the art rather than reinventing existing features. In addition, the significance of the storage allocator to reconfiguration should now be clearer. For simplicity the discussion so far has been primarily directed to primary memory — this needs to be generalized to encompass any other type of storage module.

Although the previous discussion of demand paging was framed in terms of primary memory, the essential concepts are in fact common to other types of storage modules; however, the somewhat different. usual terminology is File systems typically manage secondary disk and drum storage, for example, by considering each module to be composed of a number of independent fixed length "records" -- the records are directly analogous to the blocks of primary memory. To store the information contained in a "file", the required number of records are assigned and a "file map" is maintained to show address of each record of the file -- a file map is the directly analogous to the page table for a program, and a file be just a secondary storage copy of a program. may the system copy information from primary storage to device such as a drum, but also various types of storage modules may be arranged in a hierarchy. The file system may move records from one secondary storage module down to another secondary storage module in order to make room higher up in the hierarchy. For example the least recently used record may be kept on the type of module with the longest access time.

The significant observation is that the storage allocator characteristics identified as relevant to reconfiguration are applicable to both primary and secondary storage modules.

Since the above discussion has identified the allocator characteristics important to reconfiguration, it is now appropriate to introduce a very specific allocator model to facilitate our discussion. The Multics file system will be used as a case study, and we will discover that it has all the desired characteristics. This particular design is chosen because it includes a practical and currently working example of a demand paging storage allocator whose motivation and details are available to the interested reader from several sources [1, 6, 21, 22], and because the research reported in this thesis includes implementation of reconfiguration capabilities for this specific system.

The Multics storage allocation design includes a feature known as <u>segmentation</u>: rather than considering a process in terms of a single program (with instructions and data), a Multics process has multiple <u>segments</u>. Therefore, each virtual address has two dimensions — a segment number and an offset (address) within the segment. Each segment has its own page table, and the two-dimensional address space of each process is defined by a <u>descriptor segment</u>, which is basically a table (indexed by segment number) of <u>segment descriptor words</u> giving the absolute address of the page table (in the same manner as a page table base register) for each segment.

The descriptor segment is itself a segment in primary memory and the processor has a <u>descriptor segment base register</u> containing the absolute address of the page table for the descriptor segment. Figure 3.3 illustrates the address translation for segmentation. Although segmentation itself does not solve any reconfiguration problems, the significant observation is that segmentation specifically contains the relocation capabilities needed for reconfiguration.

Now an understandable reaction might be that with all these levels of indirection it is certainly inefficient for the processor to translate a logical address into a reference to the ultimate absolute address of interest. Multics reduces the number of memory references needed to complete the indirection by providing a high speed associative memory within the processor. This memory maintains the sixteen most recently used page table words or segment descriptor words [23].

First we note that the associative memory distorts our model of a processing module as a module with no memory of data common to more than one process: we will see later that this is a problem that has to be specifically dealt with. Aside from this one problem area, all absolute addresses in the system for the location of instructions and data are still in page table words as discussed for demand paging. In addition there are absolute addresses of page tables in segment descriptor words and the descriptor segment base

Figure 3.3 -- Address Translation for Segmentation

register. However, the file system maintains all absolute addresses and can locate and update them if required. The file system maintains for each type of storage module a storage map that allows the system, for any absolute address, to determine that the storage block is either in use and the appropriate page table (or file map) entry can be found, or is free and can be used to meet demands for storage, or is not part of the available resources managed by the file system.

Although the Multics file system includes storage allocator features not directly applicable to reconfiguration, in this case study we have seen that Multics does provide the relocation capability essential to reconfiguration, and demand paging is available to solve the technological problems of limited storage capacity. We will refer to the Multics file system as a specific model of storage allocator design when useful as an aid to the presentation.

# 3.2 Removing a Storage Module

The preceding discussion has established a storage management environment for reconfiguration. We now develop a design for removing a storage module from the resources being used by the system. Basically, while the system is running, reconfiguration primitives move the stored information and then locate and update absolute addresses to reflect the new location. A major goal is providing a general design which is

(as much as possible) independent of the kind of information stored in the removed module.

We digress moment to observe that during reconfiguration the system needs information about each module in the configuration. Therefore, we introduce the module configuration table as the primary reconfiguration data base, and we will identify the information contained in it as we discover the need. The system creates this module configuration table during initialization and updates it during reconfiguration. From our general model we can anticipate that the module configuration table will reflect the binding of physical resources to logical resources -- in the case at hand, the table relates each physical storage module to a range of absolute addresses.

Now let us suppose that an operator requests removal of a specific storage module. The reconfiguration procedures of the operator's process must first verify that a viable configuration will remain. For example, after removing the module the minimum amount of storage for this type of device must remain, and the module must not be essential for relaying signals between processing modules. Since motivations, such as preventive maintenance, for removing a module are associated with physical hardware entities, it is convenient for the operator to identify the module by a (usually arbitrary) physical name; therefore, we extend the module configuration table to include for each module the name used

by the operator.

To remove a storage module in response to the operator request, first the system makes certain that the storage is not available to meet any future storage demands, and then the system frees any storage already in use, by moving the information to another module. In terms of the model outlined in chapter two and illustrated in Figure 3.1, the system invokes reconfiguration primitives to change the usage state of the logical storage resources to "free and unavailable". For each unit of resource in the module, the system first invokes the generic subroutine Make\_unavailable (defined in chapter two), and then invokes the generic subroutine Unbind (also defined in chapter two).

From the notion of a logical resource usage state of "available" we may invent immediately the "available list", a list of all logical storage resources available to the allocator for use in meeting storage demands. The Make\_unavailable primitive prevents future allocation of storage by removing it from the available list. Using the notation of the PL/I language, we now introduce the first specific instance of the generic closed subroutines for reconfiguration:

call Make\_unavailable (addr);

where "addr" is the name (e.g., the absolute address) of the unit of logical storage resource to be moved from the available list to a "removing list". The unit of storage

resource must, of course, be uniquely identified: if the names themselves are not unique (e.g., the same absolute address may occur in different types of storage devices), there may in fact be more than one distinct Make\_unavailable subroutine (e.g., one for each type of storage), but without loss of generality we will consider only one.

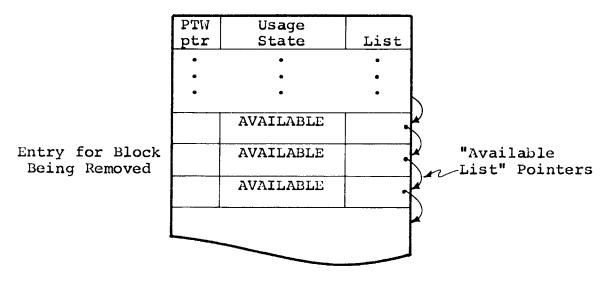

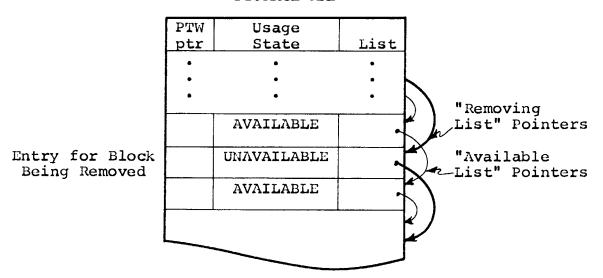

For example of the Make unavailable primitive, consider systems that use paging, such as Multics, where the potential set of logical storage resources are easily represented by a storage map -- a table indexed by storage block number (computed as the absolute address of the base of the block divided by the block size). As illustrated Figure 3.4, each entry in the storage map either has a pointer to the page table word containing the storage block address, or has a "null" pointer indicating that the storage block is free. Since there may be some absolute addresses that cannot be referenced (i.e., are unavailable), a threaded "available list" is constructed from the storage map entries to reflect the pool of storage blocks actually available to allocator. The Make unavailable subroutine simply threads the indicated storage block entry out of the "available list" and threads it into a "removing list". The usage state (viz., "unavailable") must be recorded; for example, when the allocator frees the storage block for a deleted page. "unavailable" entry is not threaded onto the "available list" as might otherwise be the case. Figure 3.5 illustrates the

Figure 3.4 -- Example of a Storage Map

### STORAGE MAP

Before Call to Make unavailable

### STORAGE MAP

After Call to Make\_unavailable

Figure 3.5 -- Example of Making Storage Unavailable

bound storage -- "demand allocated" and "wired". This class is recorded in each entry of the removing (or available) list. The techniques Unbind uses to free the storage depend on the class and are discussed in detail in the following two sections. These possible classes of bound storage are defined as follows:

- 1. <u>Demand</u> <u>allocated</u> storage is currently used to store information in response to the demand of some process, but the allocator may without the explicit "consent" of this process move the information (viz., reverse the binding to storage).