# *Parallel and Distributed Computation:*

## *Numerical Methods*

Dimitri P. Bertsekas and John N. Tsitsiklis

Massachusetts Institute of Technology

WWW site for book information and orders

<http://world.std.com/~athenasc/>

Athena Scientific, Belmont, Massachusetts

**Athena Scientific

Post Office Box 391

Belmont, Mass. 02178-9998

U.S.A.**

**Email: athenasc@world.std.com

WWW information and orders: <http://world.std.com/~athenasc/>**

Cover Design: *Ann Gallager*

© 1997 Dimitri P. Bertsekas and John N. Tsitsiklis

All rights reserved. No part of this book may be reproduced by any electronic or mechanical means (including photocopying, recording, or information storage and retrieval) without the publisher's permission in writing.

Originally published by Prentice-Hall, Inc., in 1989. Corrections listed at the end.

**Publisher's Cataloging-in-Publication Data**

Bertsekas, Dimitri P.

Parallel and Distributed Computation: Numerical Methods

Includes bibliographical references and index

1. Parallel processing (Electronic computers)

I. John Tsitsiklis N., joint author. II. Title.

QA76.5.B457 1997      004'.35      97-70648

**ISBN 1-886529-01-9**

*To Joanna and Daphne*

# Contents

|                                                                    |           |

|--------------------------------------------------------------------|-----------|

| <b>PREFACE</b>                                                     | <b>xv</b> |

| <b>1 INTRODUCTION</b>                                              | <b>1</b>  |

| 1.1 Parallel and Distributed Architectures                         | 2         |

| 1.1.1 <i>The Need for Parallel and Distributed Computation</i> ,   | 2         |

| 1.1.2 <i>Parallel Computing Systems and their Classification</i> , | 3         |

| 1.2 Models, Complexity Measures, and Some Simple Algorithms        | 8         |

| 1.2.1 <i>Models</i> ,                                              | 8         |

| 1.2.2 <i>Complexity Measures</i> ,                                 | 10        |

| 1.2.3 <i>Examples: Vector and Matrix Computations</i> ,            | 16        |

| 1.2.4 <i>Parallelization of Iterative Methods</i> ,                | 19        |

| 1.3 Communication Aspects of Parallel and Distributed Systems      | 27        |

| 1.3.1 <i>Communication Links</i> ,                                 | 30        |

| 1.3.2 <i>Data Link Control</i> ,                                   | 33        |

|       |                                                                                      |

|-------|--------------------------------------------------------------------------------------|

| 1.3.3 | <i>Routing</i> , 37                                                                  |

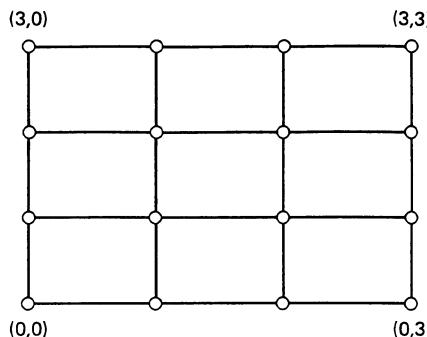

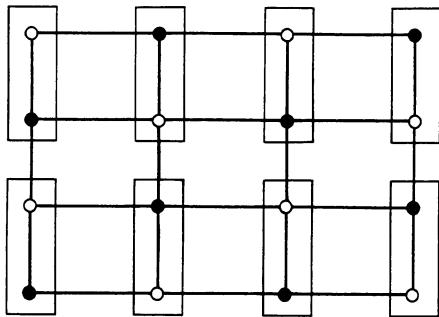

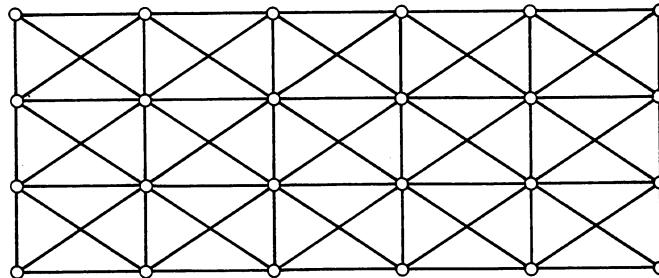

| 1.3.4 | <i>Network Topologies</i> , 39                                                       |

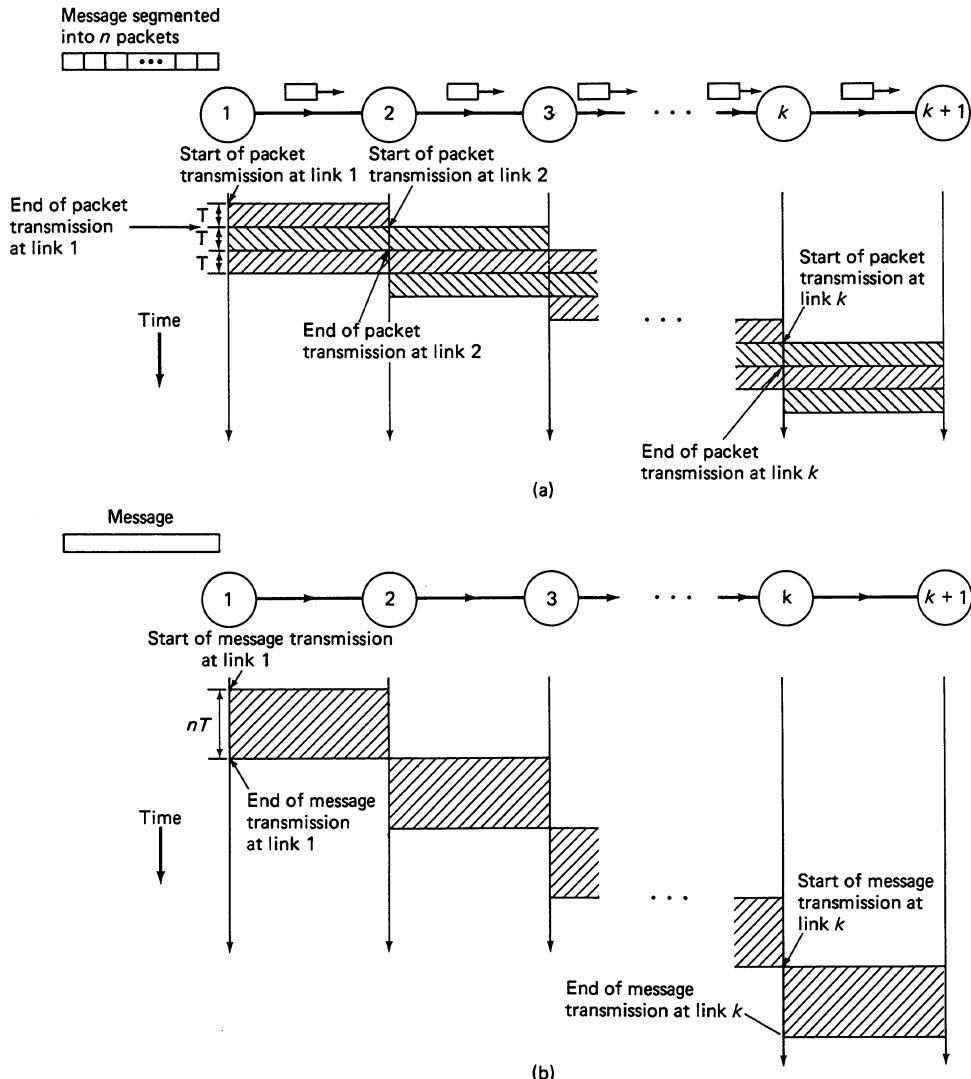

| 1.3.5 | <i>Concurrency and Communication Tradeoffs</i> , 68                                  |

| 1.3.6 | <i>Examples of Matrix–Vector Calculations</i> , 71                                   |

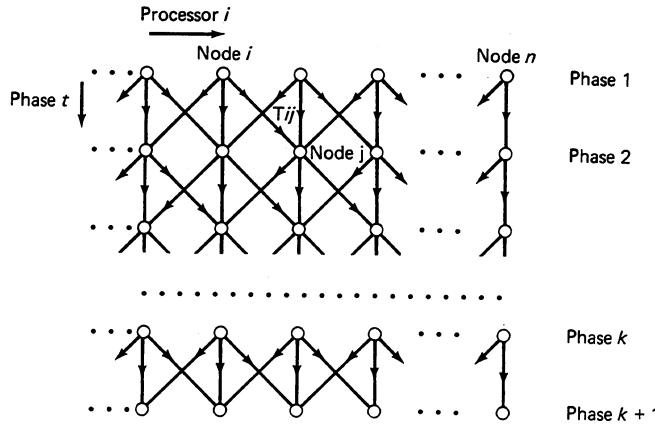

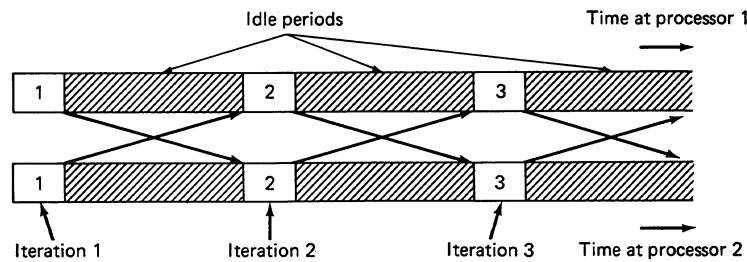

| 1.4   | Synchronization Issues in Parallel and Distributed Algorithms 88                     |

| 1.4.1 | <i>Synchronous Algorithms</i> , 88                                                   |

| 1.4.2 | <i>Asynchronous Algorithms and the Reduction of the Synchronization Penalty</i> , 95 |

|               |                               |            |

|---------------|-------------------------------|------------|

| <b>Part 1</b> | <b>Synchronous Algorithms</b> | <b>109</b> |

|---------------|-------------------------------|------------|

|          |                                                                        |            |

|----------|------------------------------------------------------------------------|------------|

| <b>2</b> | <b>ALGORITHMS FOR SYSTEMS OF LINEAR EQUATIONS AND MATRIX INVERSION</b> | <b>109</b> |

|----------|------------------------------------------------------------------------|------------|

|       |                                                                   |

|-------|-------------------------------------------------------------------|

| 2.1   | Parallel Algorithms for Linear Systems with Special Structure 110 |

| 2.1.1 | <i>Triangular Matrices and Back Substitution</i> , 110            |

| 2.1.2 | <i>Tridiagonal Systems and Odd–Even Reduction</i> , 113           |

| 2.2   | Parallel Direct Methods for General Linear Equations 118          |

| 2.2.1 | <i>Gaussian Elimination</i> , 119                                 |

| 2.2.2 | <i>Triangularization Using Givens Rotations</i> , 124             |

| 2.3   | A Fast Direct Matrix Inversion Algorithm 128                      |

| 2.4   | Classical Iterative Methods For Systems of Linear Equations 130   |

| 2.5   | Parallel Implementation of Classical Iterative Methods 135        |

| 2.5.1 | <i>An Example: Poisson’s Equation</i> , 137                       |

| 2.5.2 | <i>Multigrid Methods</i> , 139                                    |

| 2.6   | Convergence Analysis of Classical Iterative Methods 143           |

| 2.6.1 | <i>Background on Maximum Norms and Nonnegative Matrices</i> , 144 |

| 2.6.2 | <i>Convergence Analysis Using Maximum Norms</i> , 151             |

| 2.6.3 | <i>Convergence Analysis Using a Quadratic Cost Function</i> , 153 |

| 2.6.4 | <i>The Poisson Equation Revisited</i> , 155                       |

| 2.7   | The Conjugate Gradient Method 158                                 |

| 2.7.1 | <i>Description of the Algorithm</i> , 160                         |

| 2.7.2 | <i>Speed of Convergence</i> , 162                                 |

|                                                                                   |            |

|-----------------------------------------------------------------------------------|------------|

| 2.7.3 <i>Preconditioned Conjugate Gradient Method</i> , 164                       |            |

| 2.7.4 <i>Parallel Implementation</i> , 165                                        |            |

| 2.8 Computation of the Invariant Distribution of a Markov Chain 166               |            |

| 2.9 Fast Iterative Matrix Inversion 173                                           |            |

| <b>3 ITERATIVE METHODS FOR NONLINEAR PROBLEMS</b>                                 | <b>180</b> |

| 3.1 Contraction Mappings 181                                                      |            |

| 3.1.1 <i>General Results</i> , 182                                                |            |

| 3.1.2 <i>Contractions Over Cartesian Product Sets</i> , 185                       |            |

| 3.1.3 <i>Some Useful Contraction Mappings</i> , 191                               |            |

| 3.2 Unconstrained Optimization 198                                                |            |

| 3.2.1 <i>The Main Algorithms</i> , 198                                            |            |

| 3.2.2 <i>Convergence Analysis Using the Descent Approach</i> , 202                |            |

| 3.2.3 <i>The Case of a Convex Cost Function</i> , 206                             |            |

| 3.2.4 <i>Nonlinear Algorithms</i> , 207                                           |            |

| 3.3 Constrained Optimization 210                                                  |            |

| 3.3.1 <i>Optimality Conditions and the Projection Theorem</i> , 210               |            |

| 3.3.2 <i>The Gradient Projection Algorithm</i> , 212                              |            |

| 3.3.3 <i>Scaled Gradient Projection Algorithms</i> , 215                          |            |

| 3.3.4 <i>The Case of a Product Constraint Set: Parallel Implementations</i> , 217 |            |

| 3.3.5 <i>Nonlinear Algorithms</i> , 219                                           |            |

| 3.4 Parallelization and Decomposition of Optimization Problems 224                |            |

| 3.4.1 <i>Quadratic Programming</i> , 225                                          |            |

| 3.4.2 <i>Separable Strictly Convex Programming</i> , 229                          |            |

| 3.4.3 <i>The Proximal Minimization Algorithm</i> , 232                            |            |

| 3.4.4 <i>Augmented Lagrangian Methods</i> , 243                                   |            |

| 3.5 Variational Inequalities 264                                                  |            |

| 3.5.1 <i>Examples of Variational Inequality Problems</i> , 264                    |            |

| 3.5.2 <i>Preliminaries</i> , 267                                                  |            |

| 3.5.3 <i>The Projection Algorithm</i> , 269                                       |            |

| 3.5.4 <i>Linearized Algorithms</i> , 273                                          |            |

| 3.5.5 <i>The Cartesian Product Case: Parallel Implementations</i> , 275           |            |

| 3.5.6 <i>Nonlinear Algorithms</i> , 278                                           |            |

| 3.5.7 <i>Decomposition Methods for Variational Inequalities</i> , 281             |            |

**4 SHORTEST PATHS AND DYNAMIC PROGRAMMING** **291**

- 4.1 The Shortest Path Problem 293

- 4.1.1 *The Bellman–Ford Algorithm*, 294

- 4.1.2 *Other Parallel Shortest Path Methods*, 302

- 4.2 Markov Chains with Transition Costs 308

- 4.3 Markovian Decision Problems 312

- 4.3.1 *Discounted Problems*, 316

- 4.3.2 *Undiscounted Problems—Stochastic Shortest Paths*, 317

- 4.3.3 *Parallel Implementation of the Dynamic Programming Iteration*, 323

**5 NETWORK FLOW PROBLEMS** **331**

- 5.1 The Linear Network Flow Problem and its Dual 332

- 5.2 The Relaxation Method 340

- 5.2.1 *Application to the Shortest Path Problem*, 343

- 5.2.2 *Multiple Node Relaxation Method*, 345

- 5.3 The  $\epsilon$  – Relaxation Method 355

- 5.3.1 *The Auction Algorithm for the Assignment Problem*, 364

- 5.3.2 *Parallel Versions of the  $\epsilon$ –Relaxation and the Auction Algorithms*, 371

- 5.4 Complexity Analysis of the  $\epsilon$ –Relaxation Method and its Scaled Version 376

- 5.4.1 *The Scaled Version of the Algorithm*, 384

- 5.4.2 *Application to the Assignment Problem*, 386

- 5.5 Network Flow Problems with Strictly Convex Cost 390

- 5.5.1 *The Relaxation Method*, 397

- 5.5.2 *Convergence Analysis*, 398

- 5.5.3 *The Problem without Arc Flow Bounds*, 406

- 5.5.4 *An Example: Constrained Matrix Problems*, 408

- 5.5.5 *Parallel Implementations of the Relaxation Method*, 410

- 5.6 Nonlinear Multicommodity Flow Problems—Routing Applications 414

|                                                                                                          |            |

|----------------------------------------------------------------------------------------------------------|------------|

| Contents                                                                                                 | xi         |

| <b>Part 2 Asynchronous Algorithms</b>                                                                    | <b>425</b> |

| <b>6 TOTALLY ASYNCHRONOUS ITERATIVE ALGORITHMS</b> <span style="float: right;">425</span>                |            |

| 6.1 The Totally Asynchronous Algorithmic Model                                                           | 426        |

| 6.2 A General Convergence Theorem                                                                        | 431        |

| 6.3 Applications to Problems Involving Maximum Norm<br>Contraction Mappings                              | 434        |

| 6.3.1 <i>Solution of Linear Systems of Equations</i> ,                                                   | 434        |

| 6.3.2 <i>Unconstrained Optimization</i> ,                                                                | 437        |

| 6.3.3 <i>Constrained Optimization and Variational Inequalities</i> ,                                     | 440        |

| 6.3.4 <i>Dynamic Programming</i> ,                                                                       | 440        |

| 6.3.5 <i>Convergence Rate Comparison of Synchronous and Asynchronous<br/>Algorithms</i> ,                | 441        |

| 6.4 Applications to Monotone Mappings and the Shortest Path<br>Problem                                   | 445        |

| 6.5 Linear Network Flow Problems                                                                         | 451        |

| 6.6 Nonlinear Network Flow Problems                                                                      | 457        |

| 6.7 Asynchronous Relaxation for Ordinary Differential Equations<br>and Two-Point Boundary Value Problems | 469        |

| 6.7.1 <i>The Asynchronous Relaxation Algorithm</i> ,                                                     | 470        |

| 6.7.2 <i>Two-Point Boundary Value Problems</i> ,                                                         | 477        |

| 6.7.3 <i>The Discrete Time Case</i> ,                                                                    | 478        |

| <b>7 PARTIALLY ASYNCHRONOUS ITERATIVE METHODS</b> <span style="float: right;">481</span>                 |            |

| 7.1 The Partially Asynchronous Algorithmic Model                                                         | 483        |

| 7.2 Algorithms for Fixed Points of Nonexpansive Mappings                                                 | 490        |

| 7.2.1 <i>A Convergence Result</i> ,                                                                      | 490        |

| 7.2.2 <i>Weakly Diagonally Dominant Systems of Linear Equations</i> ,                                    | 498        |

| 7.2.3 <i>Strictly Convex Network Flow Problems</i> ,                                                     | 501        |

| 7.3 Algorithms for Agreement and for Markov Chain<br>Problems                                            | 508        |

| 7.3.1 <i>The Agreement Algorithm</i> ,                                                                   | 508        |

| 7.3.2 <i>An Asynchronous Algorithm for the Invariant Distribution of a<br/>Markov chain</i> ,            | 515        |

|          |                                                                                     |            |

|----------|-------------------------------------------------------------------------------------|------------|

| 7.4      | Load Balancing in a Computer Network                                                | 519        |

| 7.5      | Gradient–Like Optimization Algorithms                                               | 527        |

| 7.5.1    | <i>The Algorithm and its Convergence,</i>                                           | 527        |

| 7.5.2    | <i>The Role of the Various Parameters,</i>                                          | 532        |

| 7.5.3    | <i>Block–Iterative Algorithms,</i>                                                  | 533        |

| 7.5.4    | <i>Gradient Projection Algorithms,</i>                                              | 534        |

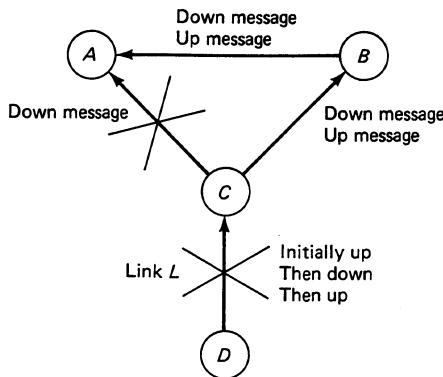

| 7.6      | Distributed Asynchronous Routing in Data Networks                                   | 536        |

| 7.6.1    | <i>Problem Definition,</i>                                                          | 536        |

| 7.6.2    | <i>The Algorithm and its Convergence,</i>                                           | 538        |

| 7.6.3    | <i>Discussion,</i>                                                                  | 546        |

| 7.7      | A Model in Which Several Processors Update the Same Variables                       | 550        |

| 7.8      | Stochastic Gradient Algorithms                                                      | 556        |

| 7.8.1    | <i>Description of the Algorithm and Assumptions,</i>                                | 558        |

| 7.8.2    | <i>A Convergence Result,</i>                                                        | 559        |

| 7.8.3    | <i>Discussion and Extensions,</i>                                                   | 567        |

| <b>8</b> | <b>ORGANIZING AN ASYNCHRONOUS NETWORK OF PROCESSORS FOR DISTRIBUTED COMPUTATION</b> | <b>570</b> |

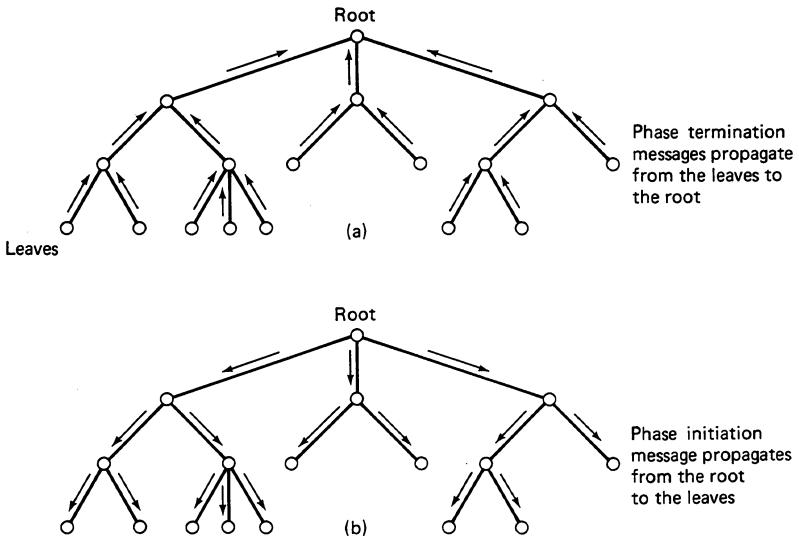

| 8.1      | Detecting Termination of a Distributed Algorithm                                    | 571        |

| 8.2      | Snapshots                                                                           | 579        |

| 8.3      | Resource Scheduling                                                                 | 587        |

| 8.4      | Synchronization Using Rollback: Asynchronous Simulation                             | 592        |

| 8.5      | Maintaining Communication with a Center                                             | 605        |

| <b>A</b> | <b>LINEAR ALGEBRA AND ANALYSIS</b>                                                  | <b>619</b> |

| <b>B</b> | <b>GRAPH THEORY</b>                                                                 | <b>653</b> |

| <b>C</b> | <b>DUALITY THEORY</b>                                                               | <b>659</b> |

| <b>D</b> | <b>PROBABILITY THEORY AND MARKOV CHAINS</b>                                         | <b>670</b> |

|                   |            |

|-------------------|------------|

| Contents          | xiii       |

| <b>REFERENCES</b> | <b>680</b> |

| <b>INDEX</b>      | <b>707</b> |

# *Preface*

Parallel and distributed computing systems offer the promise of a quantum leap in the computing power that can be brought to bear on many important problems. Whether and to what extent this promise can be fulfilled is still a matter of speculation, but several years of practical experience with both parallel computers and distributed data communication networks have brought about an understanding of the potential and limitations of parallel and distributed computation. The purpose of this book is to promote this understanding by focusing on algorithms that are naturally suited for large scale parallelization and that represent the best hope for solving problems which are much larger than those that can be solved at present.

Work on parallel and distributed computation spans several broad areas, such as the design of parallel machines, parallel programming languages, parallel algorithm development and analysis, and applications related issues. The focus of this book is on algorithms, and, even within this area, we restrict our attention primarily to numerical algorithms for solving systems of equations or optimization problems. Our choice of material is motivated by large problems for which it is essential to harness the power of massive parallelism, while keeping the communication overhead and delays within tolerable limits. Accordingly, we emphasize algorithms that admit a high degree of parallelization such as relaxation methods of the Jacobi and Gauss-Seidel type, and we

address extensively issues of communication and synchronization. In particular, we discuss algorithms for interprocessor communication and we provide a comprehensive convergence analysis of asynchronous iterative methods.

The design of parallel algorithms can be pursued at several levels, and this explains to some extent the diversity of the literature on the subject. For example:

- (a) One approach is to parallelize an existing serial algorithm, perhaps after modifications, or to develop a new and easier to parallelize algorithm, without being too specific about the implementation in particular types of machines. Here one might be concerned with the algorithm's convergence and rate of convergence (in either a synchronous or an asynchronous computing environment), and with the algorithm's potential for substantial speedup over its serial counterpart.

- (b) A second approach is to focus on the details of implementation on a particular type of machine. The issues here are algorithmic correctness, as well as time and communication complexity of the implementation.

- (c) In still another approach, the choice of the algorithm and the parallel machine are interdependent to the point where the design of one has a strong influence on the design of the other. A typical example is when a VLSI chip is designed to execute efficiently a special type of parallel algorithm.

We have mostly followed the first approach, concentrating on algorithmic analysis at a rather high level of abstraction. Our choice of algorithms, however, is such that in most cases, the methods of parallel implementation are either evident and straightforward, or else are covered by our broad discussion of parallel computation given in Chapter 1. We have not dealt with implementations in specific machines because types of machines are rapidly changing. Nonetheless, at several points, we have made reference to computations in regular architectures, such as mesh and hypercube, which are widely used. We carry out the analysis of various algorithms in considerable depth, guided by the belief that a thorough understanding of an algorithm is typically essential for its application to a challenging problem.

The book was developed through a course that we taught to graduate students at MIT. It is intended for use in graduate courses in engineering, computer science, operations research, and applied mathematics. We have assumed the equivalent of a first course in linear algebra and a grasp of advanced calculus and real analysis that most students are exposed to by the end of their undergraduate studies. Probabilistic notions beyond the theory of finite-state Markov chains are not needed with the exception of Section 7.8, which deals with stochastic gradient methods. We have not required any background in numerical analysis, graph algorithms, optimization, convexity, and duality, and we have consequently developed this material as needed in the main body of the text or the appendices. We note, however, that the mathematically mature reader who has some background in some of these fields is likely to benefit more from the book, and to gain deeper appreciation of the material.

The book can be used for several types of courses. One possibility is a course targeted on parallel algorithms, and intended for students who already have some knowl-

edge of a subset of the fields of numerical analysis, graph theory, and optimization algorithms. Furthermore, such a course could have either a computer science flavor, by focusing on Chapters 1 and 8, and parts of Chapters 2, and 4 through 6, or alternatively a numerical computation flavor by focusing on Chapters 2, 3, and parts of Chapters 1 and 4 through 7. Another possibility is a general course on numerical methods with a strong bias towards parallelizable algorithms. The book lends itself for such a course because it develops economically a broad variety of self-contained basic material in considerable depth.

Chapter 1 contains an exposition of some generic issues that arise in a broad variety of parallel algorithms and are best addressed without specific reference to any particular algorithm. In particular, we discuss the scheduling of a set of processors for the parallel execution of a prescribed algorithm, some basic issues relating to interprocessor communication, and the effects of the communication penalty on the amount by which an algorithm can be speeded up. Special attention is paid to a few interesting architectures such as mesh and hypercube. We then consider issues of synchronization, and we contrast synchronous and asynchronous algorithms. In this chapter, we also introduce relaxation methods of the Gauss-Seidel and Jacobi type and some associated issues of parallelization, communication, and synchronization that are recurring themes throughout the book.

Chapter 2 deals with parallel algorithms for systems of linear equations and matrix inversion. It covers direct methods for general systems as well as systems with special structure, iterative methods, including their convergence analysis, and the conjugate gradient method.

Chapter 3 is devoted to iterative methods for nonlinear problems, such as finding fixed points of contraction mappings, unconstrained and constrained optimization, and variational inequalities. The convergence theory for such methods is developed in an economical way and emphasizes the case of Cartesian product constraint sets (in a primal and a dual setting), which lends itself naturally to parallelization and decomposition.

Chapter 4 deals with the shortest path problem and other, more general, dynamic programming problems. The dynamic programming algorithm can be viewed as a relaxation method and lends itself well for parallelization. We establish (and strengthen somewhat) the classical results for discounted and undiscounted Markovian decision problems, and we also discuss the associated parallel computation issues.

Chapter 5 is devoted to network flow problems. In the first four sections, we deal with the important class of linear problems, and we present some easily parallelizable algorithms, that are conceptually related to the Gauss-Seidel and Jacobi relaxation methods. We then discuss related algorithms for network problems with nonlinear convex cost. The methods of the first five sections can be viewed as relaxation methods applied in a space of dual (price) variables. In the last section we consider relaxation-like methods applied to nonlinear multicommodity flow problems in the primal space of flow variables.

The last three chapters deal with asynchronous algorithms in which each processor computes at its own pace, using intermediate results of other processors that are possibly outdated due to unpredictable communication delays. Among other topics, we develop

asynchronous versions of all the major types of synchronous parallel algorithms that were discussed in previous chapters.

In Chapter 6, we introduce a general class of asynchronous iterative methods (called “totally asynchronous”), and we develop a general theorem for proving their convergence. This theorem is used repeatedly to establish the validity of a broad variety of asynchronous algorithms involving iteration mappings that are either monotone or contracting with respect to a weighted maximum norm. In particular, we show convergence of linear and nonlinear iterations involving weighted maximum norm contractions arising in the solution of systems of algebraic or differential equations, discounted dynamic programming, unconstrained and constrained optimization, and variational inequalities. We also discuss iterations involving monotone mappings arising in shortest path problems, undiscounted dynamic programming, and linear and nonlinear network flow problems.

In Chapter 7, we consider “partially asynchronous” algorithms in which some mild restrictions are placed on the amount of asynchronism present. We prove convergence of a variety of algorithms for fixed points of nonexpansive mappings, deterministic and stochastic optimization, Markov chains, load balancing in a computer network, and optimal routing in data networks.

Chapter 8 is similar in philosophy to Chapter 1 in that it deals with generic issues of parallel and distributed computation. It discusses the organization of an inherently asynchronous network of processors for the purpose of executing a general type of parallel algorithm. It addresses issues like termination detection, processor scheduling, methods for taking a “snapshot” of the global state of a computing system, synchronization via “rollback,” and methods for maintaining communication with a center in the face of topological changes.

Many of our subjects can be covered independently of each other, thereby allowing the reader or an instructor to use material selectively to suit his/her needs. For example, the following groups of sections can be omitted without loss of continuity:

- (a) Sections 2.1 to 2.3, that deal with direct methods for linear systems of equations.

- (b) Sections 2.8, 4.2, 4.3, 7.3, 7.4, 7.7, and 7.8 that develop or use the theory of Markov chains.

- (c) The material on decomposition methods based on duality in Section 3.4 and Sub-section 3.5.7.

- (d) The dynamic programming material of Sections 4.2 and 4.3.

- (e) The material on linear network flow problems in Sections 5.1 to 5.4, and 6.5.

- (f) Sections 5.6 and 7.6, dealing with nonlinear multicommodity network flow problems.

- (g) The material on nonlinear network flow problems in Sections 5.5, 6.6, and Sub-section 7.2.3.

Each major section contains several exercises that, for the most part, illustrate and supplement the theoretical developments of the text. They include algorithmic variations, convergence and complexity analysis, examples, and counterexamples. Some of the

exercises are quite challenging, occasionally representing recent research. The serious reader will benefit a great deal from these exercises, which constitute one of the principal components of the text. Solutions of all the exercises are provided in a manual that will be available to instructors.

A substantial portion of our material has not been covered in other textbooks. This includes most of the last two sections of Chapter 1, much of the last two sections of Chapter 3, Sections 5.2 through 5.5, the entire Chapters 6 and 7, and most of Chapter 8. Some of the material presented was developed as the textbook was being written and has not yet been published elsewhere.

The literature on our subject is enormous, and our references are not comprehensive. We thus apologize in advance to the many authors whose work has not been cited. We have restricted ourselves to listing the sources that we have used, together with a selection of sources that contain material supplementing the text.

We are thankful to a number of individuals and institutions for their help. The inquisitive spirit of our students motivated us to think harder about many issues. We learned a great deal about distributed computation through our long association and collaboration with Bob Gallager and Pierre Humblet. We have appreciated our research collaboration with Michael Athans, David Castanon, Jon Eckstein, Eli Gafni, and Christos Papadimitriou, that produced some of the material included in the book. Tom Luo and Cuneyt Ozveren contributed research material that was incorporated in exercises. We are thankful for the helpful comments of a number of people, including Chee-Seng Chow, George Cybenko, Stratis Galopoulos, George Hart, and Tom Richardson. Our greatest debt of gratitude to a single individual goes to Paul Tseng who worked closely with us on several of the topics presented, particularly the communication algorithms of Section 1.3, the network flow algorithms of Chapter 5, and the partially asynchronous algorithms of Section 7.2. In addition, Paul reviewed the entire manuscript, sharpened several proofs and results, and contributed much research in the form of exercises. We were fortunate to work at the Laboratory for Information and Decision Systems of M.I.T., which provided us with a stimulating research environment. Funding for our research was provided by the Army Research Office through the Center for Intelligent Control Systems, Bellcore Inc., the National Science Foundation, and the Office of Naval Research.

# 1

## *Introduction*

As we embark on the study of parallel and distributed numerical methods it is useful to reflect on their differences from their serial counterparts. There are several issues related to parallelization that do not arise in a serial context. A first issue is *task allocation*, that is, the breakdown of the total workload in smaller tasks assigned to different processors, and the proper sequencing of the tasks when some of them are interdependent and cannot be executed simultaneously. A second issue is the *communication* of interim computation results between the processors; our objective here is to carry out the communication efficiently, and to estimate its impact on performance. A third issue is the *synchronization* of the computations of different processors. In some methods, called *synchronous*, processors must wait at predetermined points for the completion of certain computations or for the arrival of certain data, and the mechanism used to enforce such synchronization may have an important effect on performance. In other methods, called *asynchronous*, there is no requirement for waiting at predetermined points, and the corresponding implications for the methods' validity must be assessed. Other issues relate to the development of appropriate performance measures for parallel methods, and the effects of the system's architecture on these performance measures.

Issues such as the above are important in a variety of contexts and are, therefore, most economically studied without reference to a specific numerical method. We address some of them in this introductory chapter, and we develop some results and methodological approaches that will be used throughout the book. Our analysis is not always fully

rigorous because we do not always adhere to formal models of distributed computation. This helps us develop the main ideas in a more accessible and intuitive manner than it would be possible otherwise. At the same time our analysis is sufficiently detailed to provide the basis for more rigorous proofs where needed, and to convince most readers of the essential correctness of our results.

Section 1.1 contains a brief overview of some application domains and of the presently existing parallel computing systems. In Section 1.2, we consider a simple model of synchronous parallel computation, in which communication issues are ignored, and discuss the concepts of time complexity, speedup, and efficiency. We also discuss issues arising in the parallelization of iterative methods. In Section 1.3, we consider communication issues in parallel and distributed systems. Following a brief discussion of data link control and routing, we formulate some basic communication problems that arise frequently in the algorithms of subsequent chapters, and we provide optimal or nearly optimal algorithms for these problems. At the same time, we discuss the properties of some of the more popular processor interconnection networks. In Section 1.4, we consider methods for algorithm synchronization. We also introduce asynchronous algorithms, compare them informally with their synchronous counterparts, and provide a glimpse of some of their interesting convergence properties that will be the focal point of Chapters 6 and 7.

## 1.1 PARALLEL AND DISTRIBUTED ARCHITECTURES

Parallel and distributed computation is currently an area of intense research activity, motivated by a variety of factors. There has always been a need for the solution of very large computational problems, but it is only recently that technological advances have raised the possibility of massively parallel computation and have made the solution of such problems possible. Furthermore, the availability of powerful parallel computers is generating interest in new types of problems that were not addressed in the past. Accordingly, the development of parallel and distributed algorithms is guided by this interplay between old and new computational needs on the one hand, and technological progress on the other. To appreciate this effect, we briefly discuss some application areas and the types of computing systems that new technologies have made possible.

### 1.1.1 The Need for Parallel and Distributed Computation

We restrict attention to numerical computation, since this is the major application considered in this book. Symbolic computation and artificial intelligence applications have also played an important role in the development of the subject, but are outside our scope.

The original needs for fast computation have been in a number of contexts involving partial differential equations (PDEs), such as computational fluid dynamics and weather prediction, as well as in image processing, etc. In these applications, there is a large number of numerical computations to be performed. The desire to solve more and more

complex problems has always been running ahead of the capabilities of the time, and has provided a driving force for the development of faster, and possibly parallel, computing machines. The above mentioned types of problems can be easily decomposed along a spatial dimension, and have therefore been prime candidates for parallelization, with a different computational unit (processor) assigned the task of manipulating the variables associated with a small region in space. Furthermore, in such problems, interactions between variables are local in nature, thus leading to the design of parallel computers consisting of a number of processors with nearest neighbor connections.

More recently, there has been increased interest in other types of large scale computation. Some examples are the analysis, simulation, and optimization of large scale interconnected systems, queueing systems being a noteworthy representative. Other examples relate to the solution of general systems of equations, mathematical programming, and optimization problems. A common property of such problems, as they arise in practice, is that they can be decomposed, but the subtasks obtained from such a decomposition tend to be fewer and more complex than those obtained in the context of partial differential equations. In particular, the regular and repetitive structure of PDEs is lost. Accordingly, one is led to use fewer and more powerful processors, coordinated through a more complex control mechanism.

In both of the above classes of applications, the main concerns are cost and speed: the hardware should not be prohibitively expensive, and the computation should terminate within an amount of time that is acceptable for the particular application.

A third area of application of parallel, or rather distributed, computation is in information acquisition, information extraction, and control, within geographically distributed systems. An example is a sensor network in which a set of geographically distributed sensors obtain information on the state of the environment and process it cooperatively. Another example is provided by data communication networks in which certain functions of the network (such as correct and timely routing of the messages traveling in the network) have to be controlled in a distributed manner, through the cooperation of the computers residing at the nodes of the network. In this context of distributed computation, the predominant issues are somewhat different from those discussed earlier. Besides cost and speed, there is a more fundamental concern: the distributed system should be able to operate correctly in the presence of limited, sometimes unreliable, communication capabilities, and often in the absence of a central control mechanism.

### 1.1.2 Parallel Computing Systems and their Classification

We discuss here how technology has responded to the computational needs just mentioned, and we provide a classification of existing systems. An important distinction is between *parallel* and *distributed* computing systems. Roughly speaking, parallel computing systems consist of several processors that are located within a small distance of each other. Their main purpose is to execute jointly a computational task and they have been designed with such a purpose in mind; communication between processors is reliable and predictable. Distributed computing systems are different in a number of

ways. Processors may be far apart, and interprocessor communication is more problematic. Communication delays may be unpredictable, and the communication links themselves may be unreliable. Furthermore, the topology of a distributed system may undergo changes while the system is operating, due to failures or repairs of communication links, as well as due to addition or removal of processors. Distributed computing systems are usually loosely coupled; there is very little, if any, central coordination and control. Each processor may be engaged in its own private activities while at the same time cooperating with other processors in the context of some computational task. Often, the cooperative computation in a distributed computing system is not the *raison d'être* of the system; for example, a data network exists in order to service some data communication needs, and the distributed computation taking place in the network is only a side activity supporting the main activity. For this reason, while the architecture of a parallel system is typically under the control of a system's designer, the structure of some distributed systems is dictated by exogenous considerations. Our subsequent discussion in this section is geared toward parallel computing systems. A number of issues more relevant to distributed systems will be touched upon in Sections 1.3 and 1.4. Still, there is no clear dividing line between parallel and distributed systems: several algorithmic issues are similar and we will often use the two terms interchangeably.

Traditional serial computers are characterized by the presence of a single locus of control that determines the next instruction to be executed. The data to be operated upon, during the execution of each instruction, are fetched from a global memory, one at a time. Thus, only one instruction is executed at a time, while the speed of memory access and the speed of input-output devices can slow down the computation. Several methods have been developed for alleviating these bottlenecks, cache memories and pipelining, for example. The first supercomputers were developed on the basis of such advanced computer architecture designs. By means of intelligent memory organization and use of pipelining, supercomputers have been able to execute vector operations (e.g., addition of two vectors) in time comparable to the time required for scalar operations (e.g., addition of two numbers). Thus, as far as the user is concerned, supercomputers behave as if the components of a vector are operated upon simultaneously. Nevertheless, there seem to be some fundamental limitations to the speed of fast serial computers, notwithstanding the fact that they are very costly.

Parallel computers have deviated from the above described model in a variety of ways. The first such computers consisted of a one- or two-dimensional array of processors, with nearest neighbor interconnections. Such an interconnection pattern is very natural for spatially decomposable problems like PDEs and image processing. Furthermore, there was a host computer overseeing and controlling the progress of the computation by passing to the processors the instruction to be executed next.

Processor arrays are well suited for the applications for which they are designed, but not necessarily for general purpose computation. Thus, more coarse-grained parallel computers have been introduced, in which each processor has considerably more control of its own computations, together with more computational power. Accordingly, the processors in such parallel computers are less tightly coupled. Such systems are sometimes called *multiprocessors*, and they are designed so that they can flexibly support general purpose computation.

Another line of development, resting on recent advances in very large scale integration (VLSI) technology, has led to closely coupled parallel computing systems (all computational elements are often placed on a single chip), designed for a special purpose, such as solving systems of linear equations with special structure, or performing fast Fourier transforms. Here the movement of data is very regular and the traditional notion of a stored program is not quite applicable; in effect, much of the program is encoded in the system hardware. *Systolic arrays* provide a prime example of such computing systems.

Still, the above discussion is too simple to accurately describe the wealth of parallel computers available today. For example, there are systems consisting of a large number of processors connected in some regular fashion, reminiscent of processor arrays, which are also capable of general purpose computation.

There are several parameters that can be used to describe or classify a parallel computer and we refer to these briefly.

(a) *Type and number of processors.* There are parallel computing systems with thousands of processors. Such systems are called *massively parallel*, and hold the greatest promise for significantly extending the range of practically solvable computational problems. A diametrically opposite option is *coarse-grained parallelism*, in which there is a small number of processors, say of the order of 10. In this case, each processor is usually fairly powerful, and the processors are loosely coupled, so that each processor may be performing a different type of task at any given time.

(b) *Presence or absence of a global control mechanism.* Parallel computers almost always have some central locus of control, but the question is one of degree: At what level of detail is the operation of the processors controlled? At one extreme, the global control mechanism is only used to load a program and the data to the processors, and each processor is allowed to work on its own thereafter. At the other extreme, the control mechanism is used to instruct each processor what to do at each step, as in the processor arrays mentioned earlier. Intermediate situations are also conceivable. A related popular classification along these lines distinguishes between SIMD (*Single Instruction Multiple Data*) and MIMD (*Multiple Instruction Multiple Data*) parallel computers, referring to the ability of different processors to execute different instructions at any given point in time.

(c) *Synchronous vs. asynchronous operation.* The distinction here refers to the presence or absence of a common global clock used to synchronize the operation of the different processors. Such synchronization is present in SIMD machines, by definition. Synchronous operation has some desirable properties: the behavior of the processors is much easier to control and algorithm design is considerably simplified. On the other hand, it may require some undesirable overhead and, in some contexts, synchronization may be just impossible. For example, it is quite hard to synchronize a data communication network and, even if this were feasible, it is questionable whether the associated overhead can be justified. Some related issues are discussed in Section 1.4. Finally, it should be noted that a parallel computing system operating asynchronously can simulate a synchronous system (see Section 1.4).

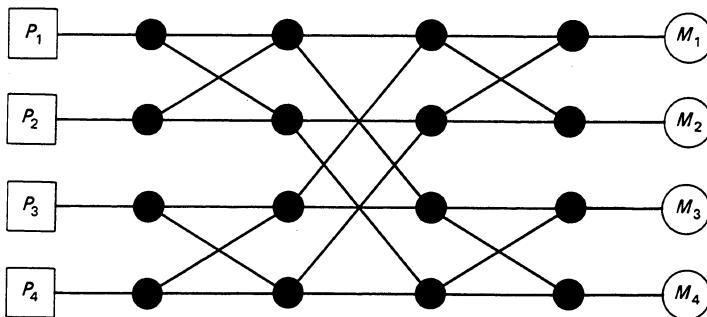

(d) *Processor interconnections.* A significant aspect of parallel computers is the mechanism by which processors exchange information. Generally speaking, there are two extreme alternatives known as *shared memory* and *message-passing* architectures, and a variety of hybrid designs lying in between. The first alternative uses a global shared memory that can be accessed by all processors. A processor can communicate to another by writing into the global memory, and then having the second processor read that same location in the memory. This solves the interprocessor communication problem, but introduces the problem of simultaneous accessing of different locations of the memory by several processors. A common approach for handling memory accesses is based on *switching systems*, such as the one depicted in Fig. 1.1.1. Naturally, the complexity of such switching systems has to increase with the number of processors; this is reflected in longer memory access times. On the other hand, under such an architecture, algorithm design is simplified, because, on a high level, the system behaves as if all processors were directly connected to each other.

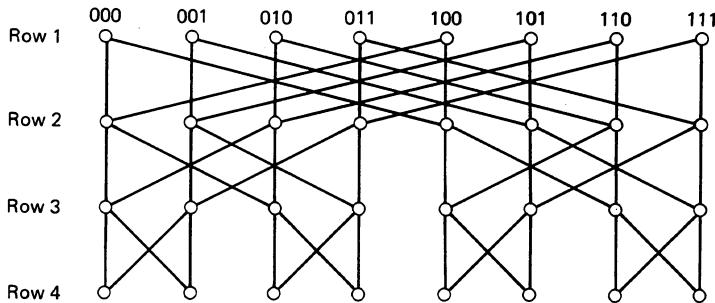

**Figure 1.1.1** A switching system connecting processors  $P_i$  to memory elements  $M_i$ . Here the intermediate nodes correspond to switches. When a message reaches a switch, it can continue on either of the two outgoing links, depending on the destination and the routing algorithm being used. Notice that in this example, there are two alternative paths from each processor to each memory element, used to reduce the probability that two processors simultaneously attempt to utilize the same link. Such redundancy improves reliability, and provides some flexibility which reduces congestion.

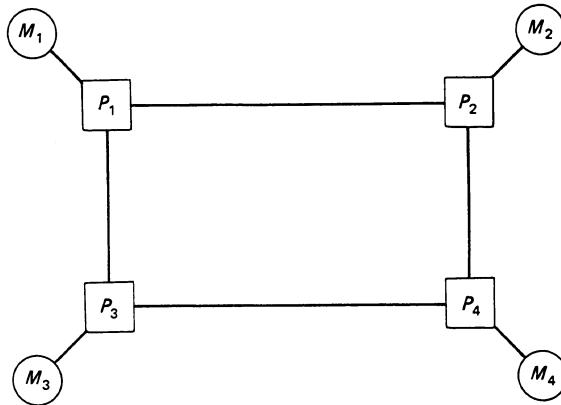

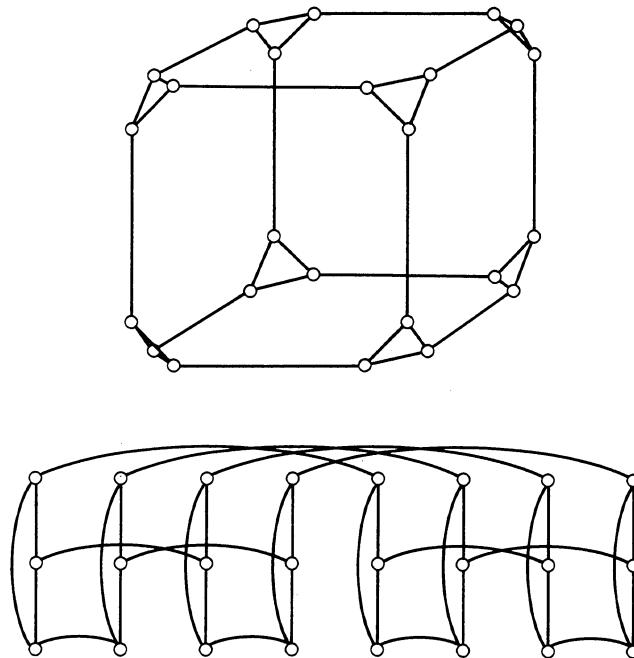

In the second major approach, there is no shared memory, but rather each processor has its own *local memory*. (Of course, each processor may have its own local memory even if there is a shared memory.) Processors communicate through an *interconnection network* consisting of direct communication links joining certain pairs of processors, as shown in Fig. 1.1.2. Which processors are connected together is an important design choice. It would be best if all processors were directly connected to each other, but this is often not feasible: either there is an excessive number of links, which leads to increased cost, or the processors communicate through a shared bus, which leads to excessive delays when the number of processors is very large, due to the necessary bus contention.

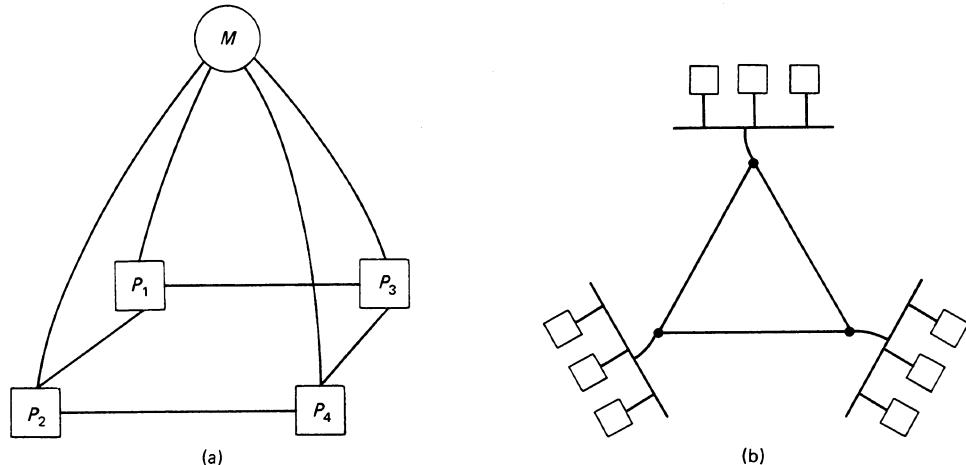

There are also several possibilities for *hybrid* designs that combine certain features from the different approaches just described. Some examples are shown in Fig. 1.1.3, although several more combinations are possible.

Figure 1.1.2 An interconnection network joining a set of processors  $P_i$ , each one endowed with its own local memory  $M_i$ .

Figure 1.1.3 Examples of hybrid designs: (a) coexistence of a shared memory and a point-to-point network; and (b) clusters of processors: a high speed bus serves for intracluster communication, and an interconnection network is used for intercluster communication.

When distant processors communicate through an interconnection network, there is usually a choice of several paths that can be used. Paths should be chosen so as to avoid underutilization of some at the expense of congestion of others. Furthermore, path selection has to be done locally, by processors that have only partial information on the congestion levels at distant parts of the network. How to do this best is the subject of the distributed routing problem. Routing in interconnection networks is briefly discussed in Subsection 1.3.3, and a particular formulation of the routing problem, relevant to data communication networks, is studied in Chapters 5 and 7.

The structure (topology) of interconnection networks is very important in both parallel and distributed computing systems, but there is an important difference. In parallel computers, the interconnection network is under the control of the designer

and for this reason it is usually designed to be very regular, whereas in some distributed systems, like data communication networks, the topology of the network is predetermined and is usually irregular.

## 1.2 MODELS, COMPLEXITY MEASURES, AND SOME SIMPLE ALGORITHMS

### 1.2.1 Models

There is a variety of models of parallel and distributed computation, incorporating different assumptions on the computing power of each individual processor and on the interprocessor information transfer mechanism. For the applications considered in this book, formal models of parallel computation are not essential and we refer the reader to the literature for more detailed expositions (see the notes and sources at the end of the chapter).

Loosely stated, we shall assume that each processor is capable of executing certain basic instructions (such as the basic arithmetic operations, comparisons, branching instructions of the “if ... then” type, etc.), and that there is a mechanism through which processors may exchange information. Concerning the processors’ computational power, it will be often assumed that each basic instruction requires one time unit. Concerning information exchange, we shall sometimes make the simplifying assumption that information transfers are instantaneous and cost-free. On other occasions, we shall assume that the processors communicate through a shared memory or by exchanging messages through an interconnection network. In the latter case, more specific assumptions on the delay incurred by messages as they travel through the network will be introduced as needed.

We postpone the discussion of communication issues for Section 1.3. We now describe in some detail a simple model that will be used to illustrate certain key aspects of parallel computation. This model is actually adequate for most of the synchronous algorithms considered in this book, as long as communication issues are ignored.

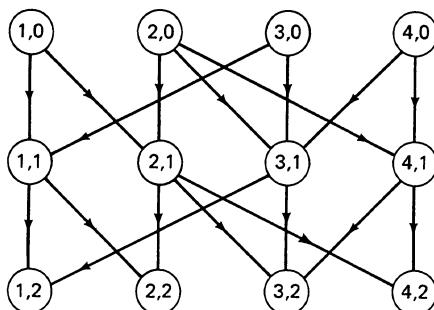

#### Representation of Parallel Algorithms by Directed Acyclic Graphs

A *directed acyclic graph* (DAG) is a directed graph that has no positive cycles, that is, no cycles consisting exclusively of forward arcs (see Appendix B). A DAG can be used to represent a parallel algorithm, as we proceed to show.

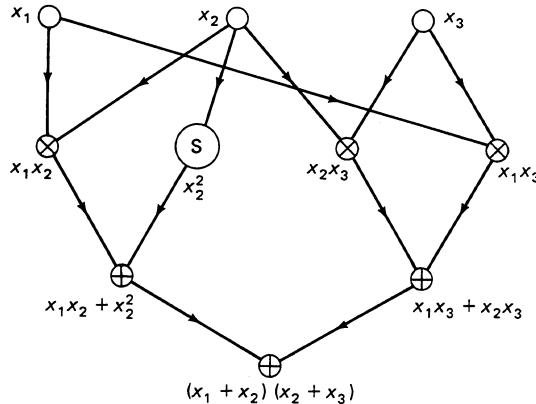

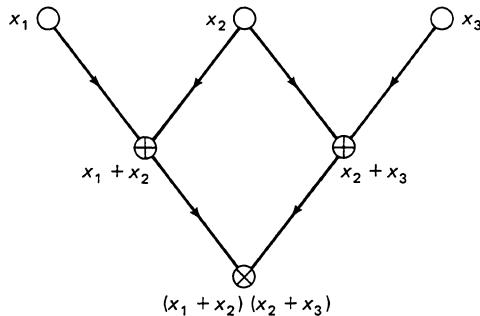

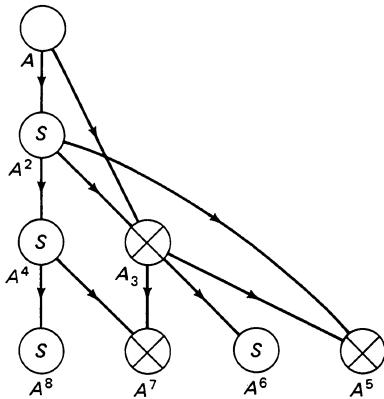

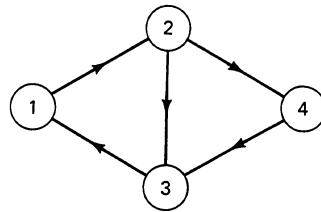

Let  $G = (N, A)$  be a DAG, where  $N = \{1, \dots, |N|\}$  is the set of nodes, and  $A$  is the set of directed arcs. Each node represents an operation performed by an algorithm, and the arcs are used to represent data dependencies. In particular, an arc  $(i, j) \in A$  indicates that the operation corresponding to node  $j$  uses the results of the operation corresponding to node  $i$ . An operation could be elementary (e.g., an arithmetic or a binary Boolean operation, as shown in Fig. 1.2.1), or it could be a high-level operation like the execution of a subroutine.

**Figure 1.2.1** Representation of an algorithm for evaluating the arithmetic expression  $(x_1 + x_2)(x_2 + x_3)$  by means of a DAG. The label at each node indicates the operation corresponding to that node. In particular, the label  $S$  stands for squaring.

We introduce some graph-theoretic terminology. We say that node  $i \in N$  is a *predecessor* of node  $j \in N$  if  $(i, j) \in A$ . The *in-degree* of node  $i \in N$  is the number of predecessors of that node. The *out-degree* of node  $i \in N$  is the number of nodes for which  $i$  is a predecessor. Nodes with in-degree zero are called *input* nodes and nodes with out-degree zero are called *output* nodes. We use  $N_0$  to denote the set of nodes that are not input nodes. A *positive path* is a sequence  $i_0, \dots, i_K$  of nodes such that  $(i_k, i_{k+1}) \in A$  for  $k = 0, \dots, K-1$ . The number  $K$  is called the *length* of the path. The *depth* of a DAG is defined as the largest length of the positive paths, and is denoted by  $D$ . It is seen that  $D$  is finite, as a consequence of acyclicity, and that a longest positive path must start at an input node and end at an output node. We assume throughout that  $G$  has at least one arc and therefore  $D \geq 1$ .

Let us denote by  $x_i$  the result of the operation corresponding to the  $i$ th node in the DAG. Then, the DAG can be viewed as a representation of functional dependencies of the form

$$x_i = f_i(\{x_j \mid j \text{ is a predecessor of } i\}).$$

Here  $f_i$  is a function describing the operation corresponding to the  $i$ th node. If  $i$  is an input node, then  $x_i$  does not depend on other variables and is viewed as an external input variable. Thus, the operation corresponding to an input node  $i$  essentially amounts to reading the value of the input variable  $x_i$ , and we will assume that this takes negligible time. For any node  $i$  that is not an input node (i.e.,  $i \in N_0$ ), we shall assume that the corresponding operation (that is, the evaluation of the function  $f_i$ ) takes one time unit. This assumption is reasonable if each node represents an arithmetic operation. However, in more complicated numerical algorithms, the execution times corresponding to different nodes could be widely different. In that case, the assumption of unit time per operation may be considerably violated, with an attendant complication of the scheduling issues discussed below.

A DAG is only a partial representation of an algorithm. It specifies what operations are to be performed, on what operands, and imposes certain precedence constraints on

the order that these operations are to be performed. To determine completely a parallel algorithm we have to specify which processor performs what operation and at what time. Let us assume that we have available a pool of  $p$  processors and that each processor is capable of performing any one of the desired operations. For any node  $i$  that is not an input node (i.e.,  $i \in N_0$ ), let  $P_i$  be the processor assigned the responsibility of performing the corresponding operation. Also, for  $i \in N_0$ , we let  $t_i$  be a positive integer variable specifying the time that the operation corresponding to node  $i$  is completed. No processors are assigned to input nodes, and we use the convention  $t_i = 0$  for every input node  $i$ . There are two constraints that have to be imposed:

- (a) A processor can perform at most one operation at a time. Thus, if  $i \in N_0$ ,  $j \in N_0$ ,  $i \neq j$ , and  $t_i = t_j$ , then  $P_i \neq P_j$ .

- (b) If  $(i, j) \in A$ , then  $t_j \geq t_i + 1$ . This requirement reflects the fact that the operation corresponding to node  $j$  can only start after the operation corresponding to node  $i$  has been completed.

Once  $P_i$  and  $t_i$  have been fixed, subject to the above constraints, we say that the DAG has been *scheduled* for parallel execution, and we call the set  $\{(i, P_i, t_i) \mid i \in N_0\}$  a *schedule*.

The above described setup could correspond to a variety of actual implementations. For example, processor  $P_i$  could store the result  $x_i$  of its operation in a shared memory from where it can be retrieved by other processors. Alternatively, in a message-passing implementation, processor  $P_i$  sends a message with the value of  $x_i$  to any processor  $P_j$  that needs this value [that is,  $(i, j) \in A$ ]. In practice, a memory access or the transmission of a message may require some time and this has been neglected in our earlier discussion. For example, if a transmission of a message requires exactly  $\tau$  time units, and if  $(i, j) \in A$ , then the constraint  $t_j \geq t_i + 1$  should be modified to

$$t_j \geq t_i + 1, \quad \text{if } P_i = P_j,$$

and

$$t_j \geq t_i + \tau + 1, \quad \text{if } P_i \neq P_j.$$

In fact, even this requirement is rather crude, because the message delay  $\tau$  may depend on the location of processors  $P_i$  and  $P_j$  in an interconnection network. In any case, memory access times and message delays are assumed to be negligible in this section and will be addressed in detail in Section 1.3.

### 1.2.2 Complexity Measures

We first define some notation that is used throughout the text. Let  $A$  be some subset of  $\mathfrak{R}$  and let  $f : A \mapsto \mathfrak{R}$  and  $g : A \mapsto \mathfrak{R}$  be some functions. The notation  $f(x) = O(g(x))$  [respectively,  $f(x) = \Omega(g(x))$ ] means that there exists some positive constant

$c$  and some  $x_0$  such that for every  $x \in A$  satisfying  $x \geq x_0$ , we have  $|f(x)| \leq cg(x)$  [respectively,  $f(x) \geq cg(x)$ ]. The notation  $f(x) = \Theta(g(x))$  means that both  $f(x) = O(g(x))$  and  $f(x) = \Omega(g(x))$  are true. We also use  $\log x$  to denote the logarithm of  $x$  with base 2. Thus,  $x = 2^{\log x}$  for every nonnegative real number  $x$ .

Complexity measures are intended to quantify the amount of computational resources utilized by a parallel algorithm. Some interesting complexity measures are the following:

- (a) The number of processors

- (b) The time until the algorithm terminates (time complexity)

- (c) The number of messages transmitted in the course of the algorithm (communication complexity)

Complexity measures are often expressed as functions of the *size* of the problem being solved, informally defined as the number of inputs to the computation. (For example, in the problem of adding  $n$  integers,  $n$  is a natural measure of problem size.) If the problem size is held constant, it is still possible that the resources used depend on the actual values of the input variables. The usual approach in this case is to count the amount of resources required in the worst case over all possible choices of data corresponding to a given problem size.

There is a further subtlety in the definition of time complexity. It is conceivable that an algorithm has terminated, meaning that the desired outputs of the computation are available at some processors, but no individual processor is aware of this fact. In such a case, it is natural to count the additional time required for the processors to become aware of termination.

### Time Complexity of Algorithms Specified by a DAG

In the case of parallel algorithms specified by a DAG, time complexity is easy to define precisely, as we proceed to show. Let  $G = (N, A)$  be a DAG representing some parallel algorithm. Let  $\{(i, P_i, t_i) \mid i \in N_0\}$  be a schedule for this DAG that uses  $p$  processors. The time spent by such a schedule is equal to  $\max_{i \in N} t_i$ . We define  $T_p$  as the minimum of  $\max_{i \in N} t_i$ , where the minimum is taken over all possible schedules that use  $p$  processors. We view  $T_p$  as the time complexity of the algorithm described by  $G$ . Note that  $T_p$  is a function of the number  $p$  of available processors.

We define

$$T_\infty = \min_{p \geq 1} T_p.$$

It is seen that  $T_p$  is a nonincreasing function of  $p$ , and is bounded below by 0. Since  $T_p$  is integer valued, there exists a minimal integer  $p^*$  such that  $T_p = T_\infty$  for all  $p \geq p^*$ . We view  $T_\infty$  as the time complexity of the algorithm specified by  $G$  when a sufficiently large number of processors (at least  $p^*$ ) is available.

We continue with a few observations. The quantity  $T_1$  is the time needed for a serial execution of the algorithm under consideration. Evidently,  $T_1$  is equal to the

number of nodes in the DAG that are not input nodes. Another important fact is that  $T_\infty$  is equal to the depth of the DAG, which we proceed to prove.

Let  $i_0, \dots, i_K$  be a longest positive path in  $G$ . Then, node  $i_0$  is an input node and  $K$  is equal to the depth  $D$ , by the definition of  $D$ . For any schedule, we have  $t_{i_0} = 0$  and  $t_{i_{k+1}} \geq t_{i_k} + 1$  (for  $k = 0, \dots, K-1$ ), and it follows that  $t_{i_K} \geq K = D$ . We conclude that  $T_\infty \geq D$ . For the reverse inequality, we assign a different processor  $P_i$  to each node  $i$  and we let  $t_i$  be the number of arcs in a longest positive path from an input node to node  $i$ . (We set  $t_i = 0$  if  $i$  is itself an input node.) If  $(i, j) \in A$  then  $t_j \geq t_i + 1$ . This is because we can take a longest positive path from an input node to node  $i$  and append arc  $(i, j)$  to obtain a path to node  $j$ . It follows that we have a valid schedule and the corresponding time is  $\max_i t_i = D$ . Therefore,  $T_\infty \leq D$ , which proves that  $T_\infty = D$ .

For an arbitrary value of  $p$ , we have  $T_1 \geq T_p \geq T_\infty$ . The exact value of  $T_p$  is not easy to determine, in general. In fact the problem of computing  $T_p$ , given a particular DAG and a value of  $p$ , is a difficult combinatorial problem. This is not necessarily a concern because, as will be seen, there are some simple useful bounds for  $T_p$ .

### Properties of $T_p$

Let us fix a DAG  $G$ . Our first result provides a fundamental limitation on the speed of a parallel algorithm.

**Proposition 2.1.** Suppose that for some output node  $i$ , there exists a positive path from every input node to  $i$ . Furthermore, suppose that the in-degree of each node is at most 2. Then,

$$T_\infty \geq \log n,$$

where  $n$  is the number of input nodes.

**Proof.** We say that a node  $j$  in the DAG depends on  $k$  inputs if there exist  $k$  input nodes and a positive path from each one of them to node  $j$ . (For completeness, we also say that an input node  $j$  depends on one input.) We prove, by induction on  $k$ , that  $t_j \geq \log k$  for every node  $j$  depending on  $k$  inputs and for every schedule. The claim is clearly true if  $k = 1$ . Assume that the claim is true for every  $k \leq k_0$  and consider a node  $j$  that depends on  $k_0 + 1$  inputs. Since  $j$  can have at most two predecessors, it has a predecessor  $\ell$  that depends on at least  $\lceil (k_0 + 1)/2 \rceil$  inputs. Then, using the induction hypothesis,

$$t_j \geq t_\ell + 1 \geq \log \left\lceil \frac{k_0 + 1}{2} \right\rceil + 1 \geq \log(k_0 + 1),$$

and the induction is complete. **Q.E.D.**

The next result expresses the fact that if the number of processors is reduced by a certain factor, then the execution time is increased by at most that factor.

**Proposition 2.2.** If  $c$  is a positive integer and  $q = cp$  then  $T_p \leq cT_q$ .

**Proof.** Consider a schedule which takes time  $T_q$  using  $q$  processors. At each stage, at most  $q$  operations are performed, and can be carried out in at most  $q/p = c$  time units using  $p$  processors. We have thus obtained a schedule with  $p$  processors which takes at most  $cT_q$  time units. **Q.E.D.**

Another useful result is the following:

**Proposition 2.3.** For every  $p$ , we have

$$T_p < T_\infty + \frac{T_1}{p}.$$

**Proof.** Consider a schedule  $S$  for which the execution time is equal to  $T_\infty$  and, for every positive integer  $\tau$ , let  $n_\tau$  be the number of nodes  $i$  for which  $t_i = \tau$ . We define a new schedule  $S'$  that uses only  $p$  processors. The schedule  $S'$  proceeds in phases. At the  $\tau$ th phase, we perform the operations that were scheduled for time  $\tau$  under the original schedule  $S$ . Given that there are  $p$  processors available, the  $\tau$ th phase can be completed in  $\lceil n_\tau/p \rceil$  time units. Since  $T_p$  cannot be larger than the time required by schedule  $S'$ , we obtain

$$T_p \leq \sum_{\tau=1}^{T_\infty} \left\lceil \frac{n_\tau}{p} \right\rceil < \sum_{\tau=1}^{T_\infty} \left( \frac{n_\tau}{p} + 1 \right) = \frac{T_1}{p} + T_\infty,$$

where we have used the fact that  $\sum_{\tau=1}^{T_\infty} n_\tau$  is equal to  $T_1$ , the total number of nodes in the DAG that are not input nodes. **Q.E.D.**

The following result is a corollary of Prop. 2.3.

**Proposition 2.4.** (a) If  $p \geq T_1/T_\infty$ , then  $T_p < 2T_\infty$ . More generally, if  $p = \Omega(T_1/T_\infty)$ , then  $T_p = O(T_\infty)$ .

(b) If  $p \leq T_1/T_\infty$ , then

$$\frac{T_1}{p} \leq T_p < 2\frac{T_1}{p}.$$

More generally, if  $p = O(T_1/T_\infty)$ , then  $T_p = \Theta(T_1/p)$ .

**Proof.** (a) If  $p \geq T_1/T_\infty$  [respectively,  $p = \Omega(T_1/T_\infty)$ ], then  $T_1/p \leq T_\infty$  [respectively,  $T_1/p = O(T_\infty)$ ], and the result follows from Prop. 2.3.

(b) If  $p \leq T_1/T_\infty$  [respectively,  $p = O(T_1/T_\infty)$ ], then  $T_\infty \leq T_1/p$  [respectively,  $T_\infty = O(T_1/p)$ ], and Prop. 2.3 yields  $T_p < 2T_1/p$  [respectively,  $T_p = O(T_1/p)$ ]. Furthermore, Prop. 2.2 yields  $T_1 \leq pT_p$ , from which we obtain  $T_p \geq T_1/p = \Omega(T_1/p)$ . **Q.E.D.**

The last two results are of fundamental importance. They establish that although  $T_\infty$  is defined under the assumption of an unlimited number of processors,  $\Omega(T_1/T_\infty)$  processors are actually sufficient to come within a constant factor of  $T_\infty$  [Prop. 2.4(a)]. Furthermore, a corresponding schedule is obtained by simply modifying an optimal schedule for the case of an unlimited number of processors (see the proof of Prop. 2.3), as opposed to solving a generally difficult scheduling problem. This suggests a methodology whereby we first develop a parallel algorithm as if an unlimited number of processors were available, and then adapt the algorithm to the available number of processors. The significance of Prop. 2.4(b) is that as long as  $p = O(T_1/T_\infty)$ , the availability of  $p$  processors allows us to speed up the computation by a factor proportional to  $p$ , which is the best possible. We thus see that for a number of processors nearly equal to  $T_1/T_\infty$ , we obtain both optimal execution time and optimal speeding up of the computation (within constant factors).

### Finding an Optimal DAG

It is seen that there can be several DAGs corresponding to different algorithms for the same computational problem (see Fig. 1.2.2). It may then be of interest to find a DAG for which  $T_p$  is minimized, where  $p$  is the number of available processors. Let us denote by  $T_p^*$  the value of  $T_p$  corresponding to such an optimal DAG and view it as the optimal parallel time, using  $p$  processors, for the computational problem under consideration. The value of  $T_p^*$  is a measure of the complexity of the problem, as opposed to  $T_p$  which is the complexity of a particular algorithm.

**Figure 1.2.2** Another DAG representing an algorithm for evaluating the arithmetic expression  $(x_1 + x_2)(x_2 + x_3)$ . We have  $T_1 = 3$  and  $T_\infty = D = 2$ . This should be contrasted with the DAG of Fig. 1.2.1 which solves the same computational problem and for which  $T_1 = 7$  and  $D = 3$ . We conclude that the DAG given here represents a better parallel algorithm.

An explicit evaluation of  $T_p^*$  is usually very difficult. However, for several interesting classes of problems, there exist methods for constructing DAGs that come within a constant factor of the optimal. We do not pursue this issue any further and refer the reader to the notes and sources at the end of this chapter.

### Speedup and Efficiency

We now assume that a particular model of parallel computation has been chosen. This could be the DAG model considered earlier, or any other model. Let us consider a computational problem parametrized by a variable  $n$  representing problem size. (In the DAG model, different problem sizes correspond to different numbers of input variables.

Thus, properly speaking, an algorithm is not specified by a single DAG, but rather by a family of DAGs, one for each problem size.) Time complexity is generally dependent on  $n$ , and we incorporate this dependence in our notation.

We describe a few concepts that are sometimes useful in comparing serial and parallel algorithms. Suppose that we have a parallel algorithm that uses  $p$  processors ( $p$  may depend on  $n$ ), and that terminates in time  $T_p(n)$ . Let  $T^*(n)$  be the optimal serial time to solve the same problem, that is, the time required by the best possible serial (uniprocessor) algorithm for this problem. The ratio

$$S_p(n) = \frac{T^*(n)}{T_p(n)}$$

is called the *speedup* of the algorithm, and describes the speed advantage of the parallel algorithm, compared to the best possible serial algorithm. The ratio

$$E_p(n) = \frac{S_p(n)}{p} = \frac{T^*(n)}{pT_p(n)}$$

is called the *efficiency* of the algorithm, and essentially measures the fraction of time that a typical processor is usefully employed. Ideally,  $S_p(n) = p$  and  $E_p(n) = 1$ , in which case, the availability of  $p$  processors allows us to speed up the computation by a factor of  $p$ . For this to occur, the parallel algorithm should be such that no processor ever remains idle or does any unnecessary work. This ideal situation is practically unattainable. A more realistic objective is to aim at an efficiency that stays bounded away from zero, as  $n$  and  $p$  increase.

There is a difficulty with the above definitions because the optimal serial time  $T^*(n)$  is unknown, even for seemingly simple computational problems like matrix multiplication. For this reason,  $T^*(n)$  is sometimes defined differently. Some alternatives are the following:

- (a) Let  $T^*(n)$  be the time required by the best existing serial algorithm.

- (b) Let  $T^*(n)$  be the time required by a benchmark serial algorithm. For example, for multiplication of two dense  $n \times n$  matrices,  $\Theta(n^3)$  is a reasonable benchmark, even though there exist algorithms with substantially smaller time requirements [AHU74].

- (c) Finally, we may let  $T^*(n)$  be the time required by a single processor to execute the particular parallel algorithm being analyzed. (That is, we let a single processor simulate the operation of the  $p$  parallel processors.) With this choice of  $T^*(n)$ , efficiency relates to how well a particular algorithm has been parallelized, but provides no information on the absolute merits of the algorithm [in contrast with our earlier definitions of  $T^*(n)$ ].

Notice that if  $T^*(n)$  is defined as in (c), and if algorithms are specified by means of the DAG model, then  $T^*(n)$  coincides with  $T_1(n)$ . In particular, if  $p \leq O(T_1(n)/T_\infty(n))$ , then  $T_p(n) = \Theta(T_1(n)/p)$  [Prop. 2.4(b)] and

$$E_p(n) = \frac{T_1(n)}{pT_p(n)} = \Theta(1).$$

This shows that if the number of processors is suitably small, then efficient parallel implementations are possible. Furthermore, if  $p = \Theta(T_1(n)/T_\infty(n))$ , we also have  $T_p(n) = \Theta(T_\infty(n))$  [Prop. 2.4(a)] and we have a parallel implementation that is both efficient and has a time complexity within a constant factor from the optimum.

The above discussion suggests that efficiency of parallel implementation is not a concern, at least when an algorithm is specified by a DAG, and as long as communication issues are ignored. A more fundamental issue is whether the maximum attainable speedup  $T_1(n)/T_\infty(n)$  can be made arbitrarily large, as  $n$  is increased. In certain applications, the required computations are quite unstructured, and there has been considerable debate on the range of achievable speedups in real world situations. The main difficulty is that some programs have some sections that are easily parallelizable, but also have some sections that are inherently sequential. When a large number of processors is available, the parallelizable sections are quickly executed, but the sequential sections lead to bottlenecks. This observation is known as *Amdahl's law* and can be quantified as follows: if a program consists of two sections, one that is inherently sequential and one that is fully parallelizable, and if the inherently sequential section consumes a fraction  $f$  of the total computation, then the speedup is limited by

$$S_p(n) \leq \frac{1}{f + (1 - f)/p} \leq \frac{1}{f}, \quad \forall p.$$

On the other hand, there are numerous computational problems for which  $f$  decreases to zero as the size of the problem increases, and Amdahl's law is not a concern.

### 1.2.3 Examples: Vector and Matrix Computations

In this subsection, we consider some elementary but very common numerical computational tasks, present some simple parallel algorithms, and discuss their complexity and efficiency. All of the algorithms to be considered can be represented by DAGs and such representations will be occasionally employed. It is assumed that each addition or multiplication takes unit time and that processors are able to instantly exchange intermediate results. In practice, processors may be communicating through an interconnection network or through a shared memory and our analysis ignores the associated communication and memory access delays. Nevertheless, the algorithms considered here are simple enough so that they can be implemented in some architectures with negligible communication overhead. The communication aspects of such implementations will be discussed in Subsections 1.3.4 to 1.3.6.

#### Scalar Addition

The simplest computational task is the addition of  $n$  scalars. It is clear that the best serial algorithm requires  $n - 1$  operations. Thus,  $T^*(n) = n - 1$ . We now present a parallel

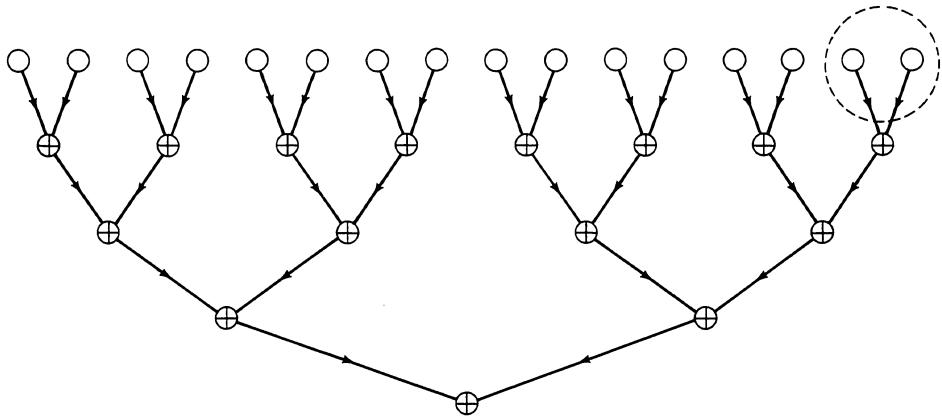

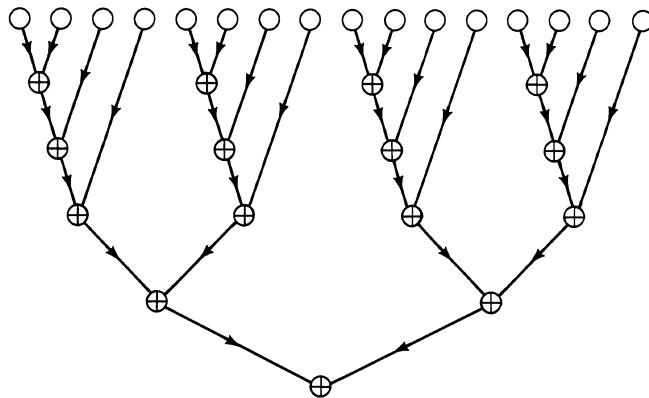

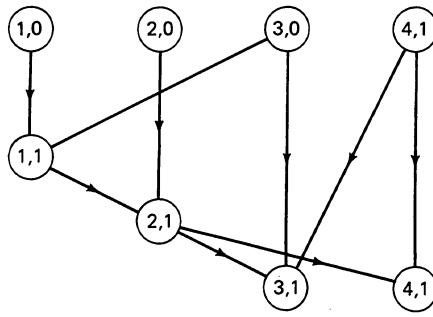

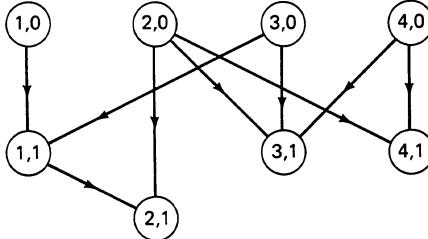

algorithm under the simplifying assumption that  $n$  is a power of 2. We partition the  $n$  scalars into  $n/2$  disjoint pairs and we use  $n/2$  different processors to add the two scalars in each pair. Thus, after one time unit, we are left with the task of adding only  $n/2$  scalars. Continuing similarly, after  $\log n$  stages, we are left with a single number and the computation terminates (see Fig. 1.2.3). This algorithm generalizes easily to the case where  $n$  is not a power of 2: the execution time becomes  $\lceil \log n \rceil$  using  $\lfloor n/2 \rfloor$  processors (see Fig. 1.2.3).

**Figure 1.2.3** Parallel computation of the sum of 16 scalars. Eight processors are needed for the parallel additions at the first stage and a total of  $4 = \log 16$  stages are needed. If the portion of the diagram enclosed in the dashed circle is removed, we obtain an algorithm for the parallel addition of 15 scalars. Notice that now only  $7 = \lfloor 15/2 \rfloor$  processors are needed.

The efficiency of the above algorithm is

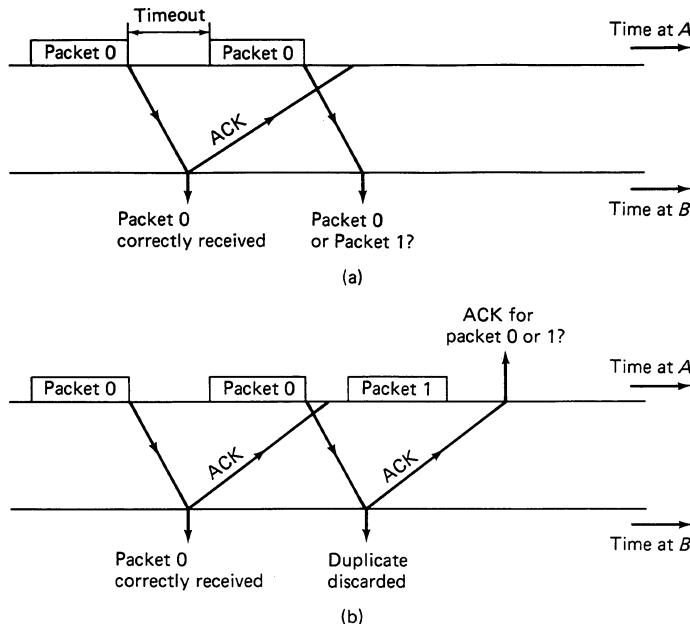

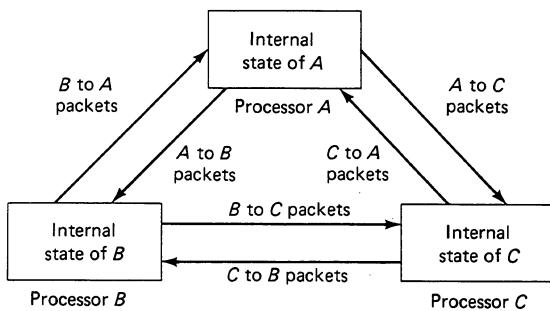

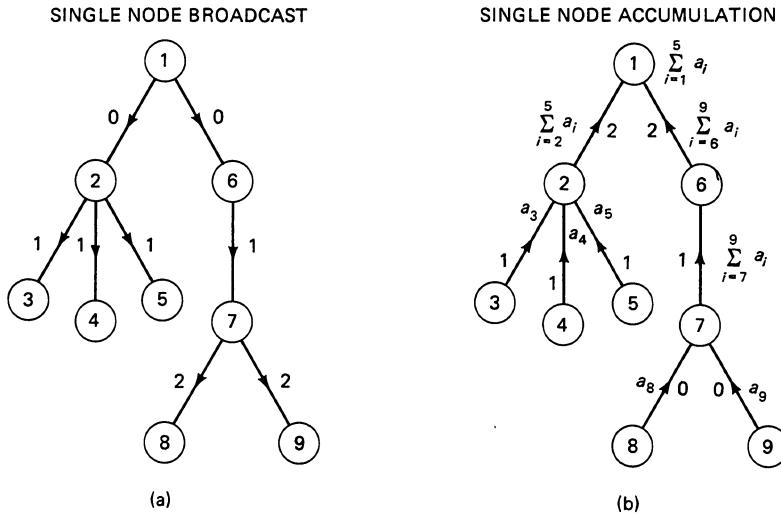

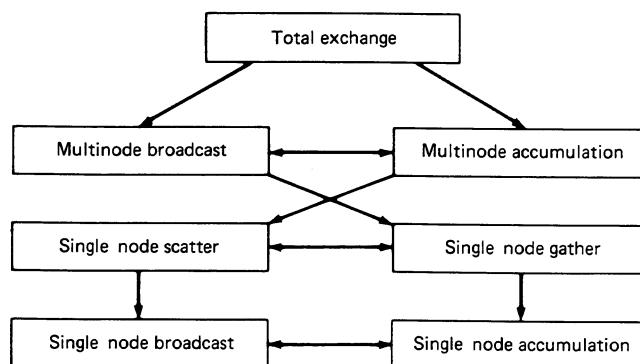

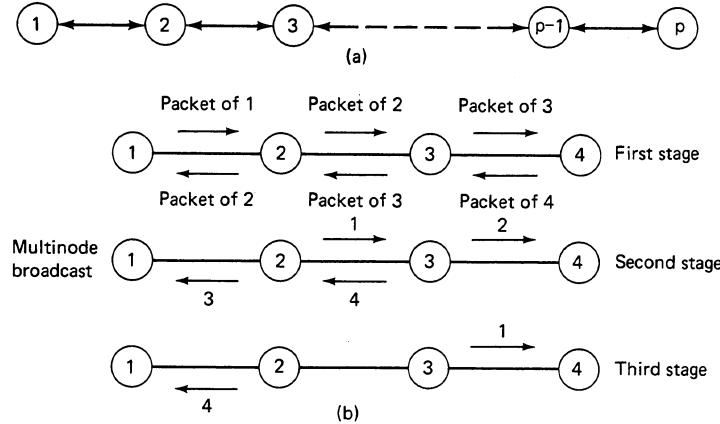

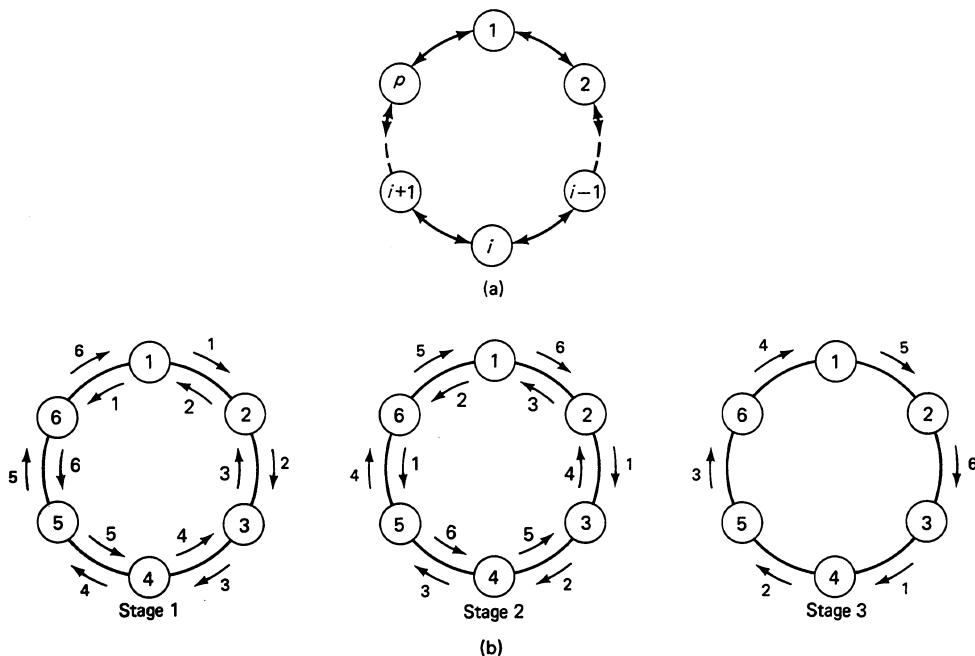

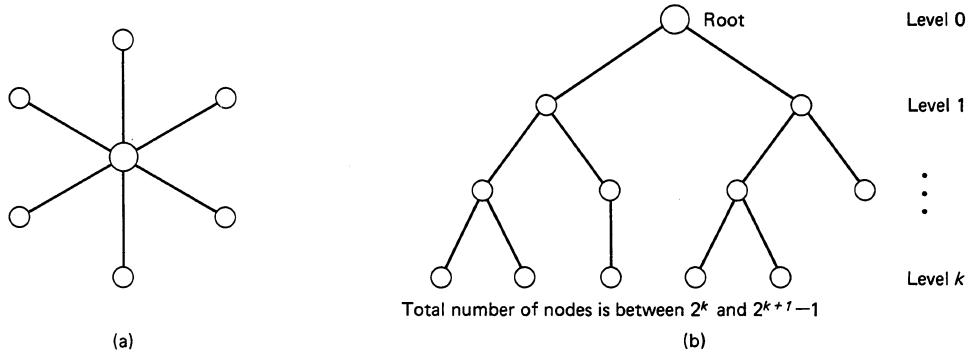

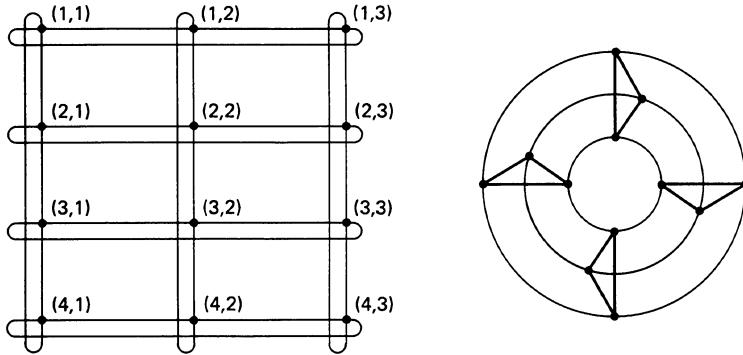

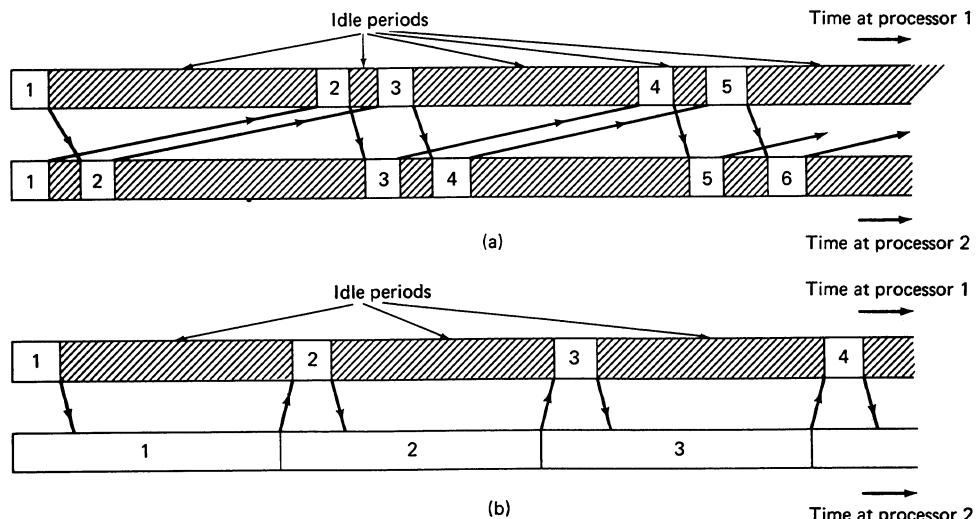

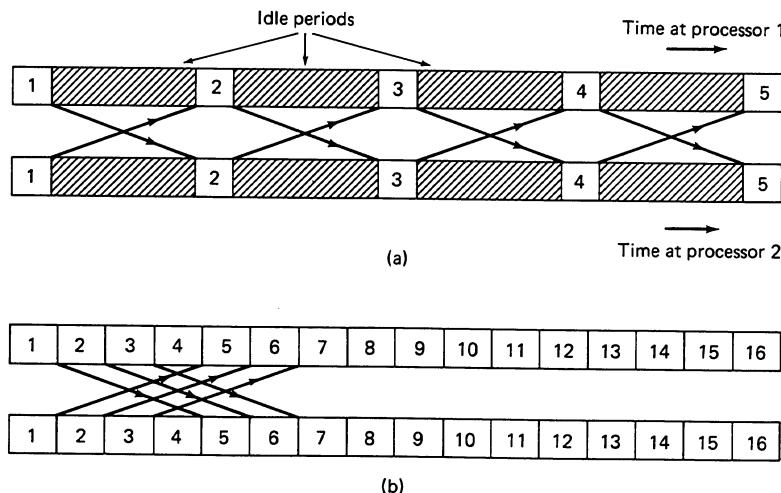

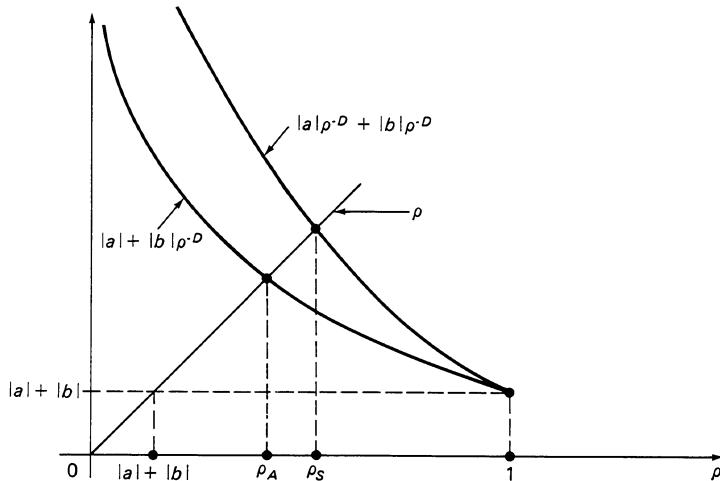

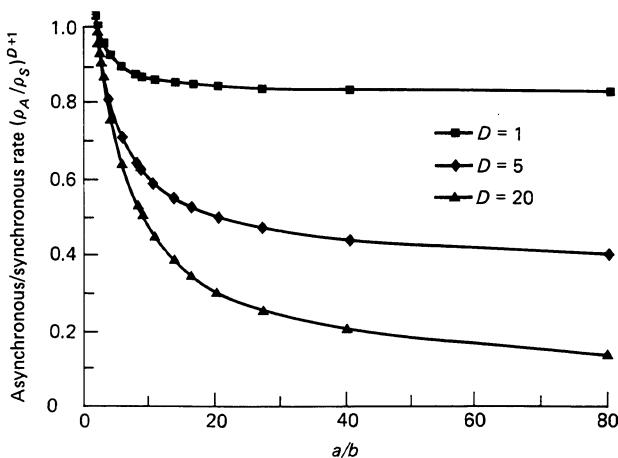

$$\frac{n-1}{\lfloor n/2 \rfloor \lceil \log n \rceil},$$