# Although We've Come to the End of the Road(map): The Future of CMOS

Nicole DiLello 6.Insight April 3, 2007

Although we've come To the end of the road Still I can't let go It's unnatural You belong to me I belong to you

- Introduction

- Current technology

- Next generation

- o 20 years from now

- Conclusion

#### Introduction

- o Current technology

- o Next generation

- o 20 years from now

- o Conclusion

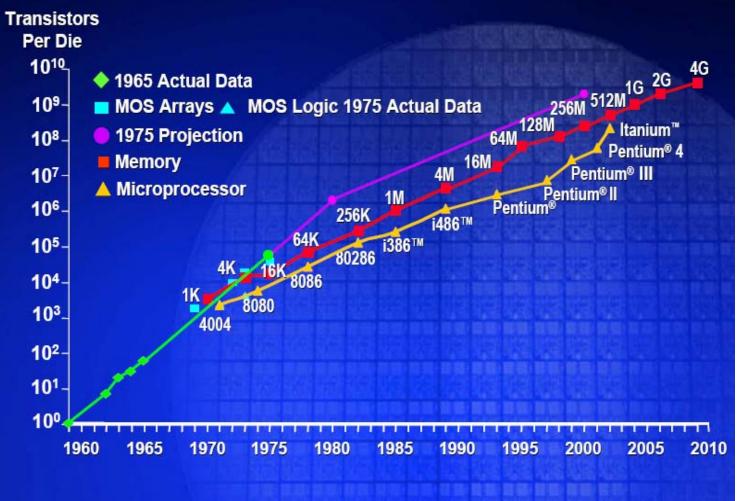

#### Moore's Law

#### **Integrated Circuit Complexity**

#### • • Before continuing...

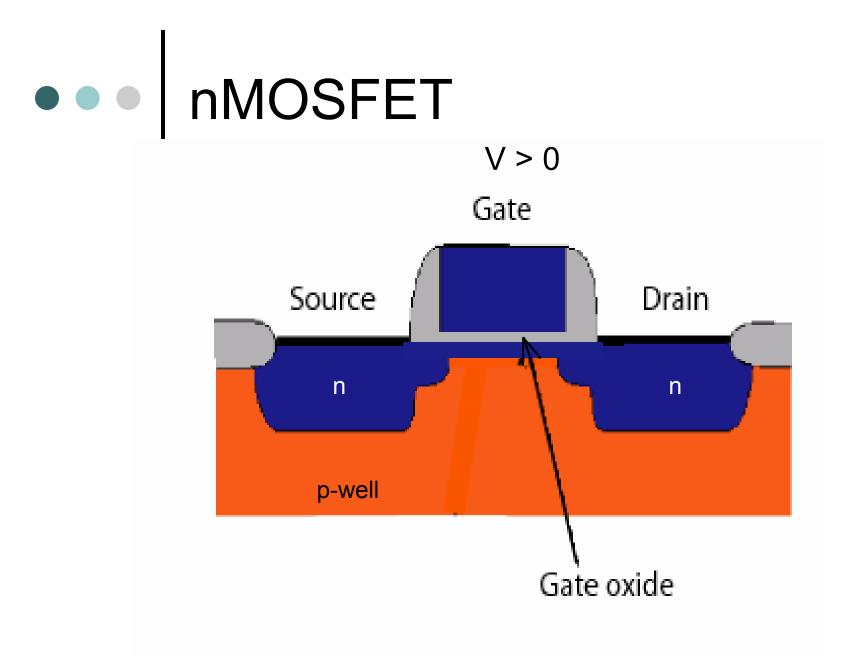

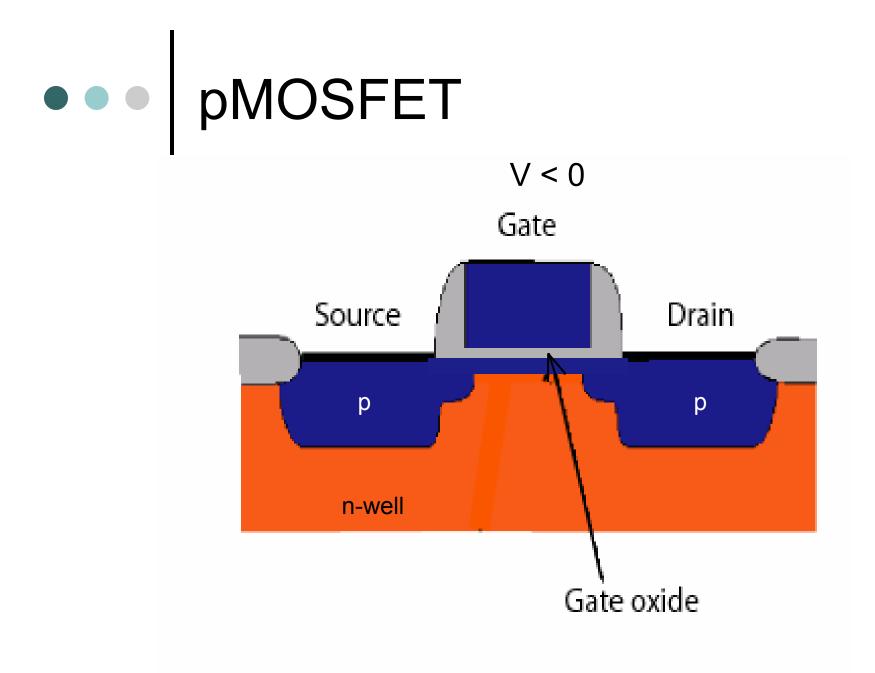

o nMOS + pMOS = CMOS

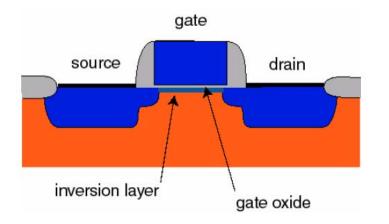

Standard MOSFET

- Made entirely from Si

- Crystalline

- n/p regions are doped

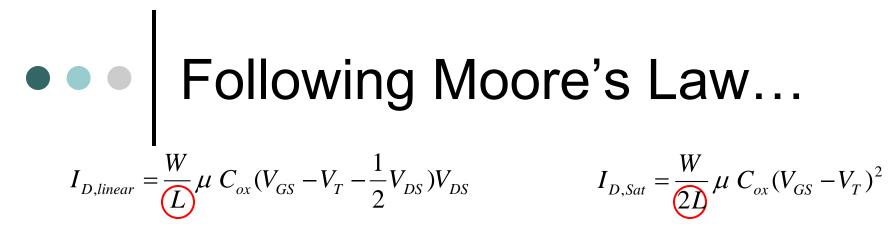

- Make transistors smaller

- International Technology Roadmap for Semiconductors (ITRS)

- U.S., Europe, Japan, Taiwan, Korea

- Chip manufacturers, academia

• • • ITRS (2005)

| Year of Production                                          | 2005               | 2006     | 2007     | 2008     | 2009     | 2010     | 2011     | 2012     | 2013    |

|-------------------------------------------------------------|--------------------|----------|----------|----------|----------|----------|----------|----------|---------|

| DRAM ½ Pitch (nm) (contacted)                               | 80                 | 70       | 65       | 57       | 50       | 45       | 40       | 36       | 32      |

| MPU/ASIC Metal 1 (M1) ½ Pitch<br>(nm)(contacted)            | 90                 | 78       | 68       | 59       | 52       | 45       | 40       | 36       | 32      |

| MPU Physical Gate Length (nm)                               | 32                 | 28       | 25       | 22       | 20       | 18       | 16       | 14       | 13      |

| Lg: Physical Lgate for High Performance logic<br>(mm) [1]   | 32                 | 28       | 25       | 22       | 20       | 18       | 16       | 14       | 13      |

| EOT: Equivalent Oxide Thickness [2]                         |                    |          |          |          |          |          |          |          |         |

| Extended planar bulk (Å)                                    | 12                 | 11       | 11       | 9        | 7.5      | 6.5      | 5        | 5        |         |

| UTB FD (Å)                                                  |                    |          |          | 9        | 8        | 7        | 6        | 5        | 5       |

| DG (Å)                                                      |                    |          |          |          |          |          | 8        | 7        | 6       |

| Gate Poly Depletion and Inversion-Layer Thick               | ness [3]           |          |          |          |          |          |          |          |         |

| Extended Planar Bulk (Å)                                    | 7.3                | 7.4      | 7.4      | 2.9      | 2.8      | 2.7      | 2.5      | 2.5      |         |

| UTB FD (Å)                                                  |                    |          |          | 4        | 4        | 4        | 4        | 4        | 4       |

| DG (Å)                                                      |                    |          |          |          |          | _        | 4        | 4        | 4       |

| EOT <sub>elec</sub> : Electrical Equivalent Oxide Thicknes  | ,<br>s in inversio | n [4]    |          |          |          |          |          |          |         |

| Extended Planar Bulk (Å)                                    | 19.3               | 18.4     | 18.4     | 11.9     | 10.3     | 9.2      | 7.5      | 7.5      |         |

| UTB FD (Å)                                                  |                    |          |          | 13       | 12       | 11       | 10       | 9        | 9       |

| DG (Å)                                                      |                    |          |          |          |          |          | 12       | 11       | 10      |

| J <sub>g.limit</sub> : Maximum gate leakage current density | [5]                |          |          |          |          |          |          |          |         |

| Extended Planar Bulk (A/cm <sup>2</sup> )                   | 1.88E+02           | 5.36E+02 | 8.00E+02 | 9.09E+02 | 1.10E+03 | 1.56E+03 | 2.00E+03 | 2.43E+03 | 2       |

| FDSOI (A/cm <sup>2</sup> )                                  | 1                  |          |          | 7.73E+02 | 9.50E+02 | 1.22E+03 | 1.38E+03 | 2.07E+03 | 2.23E+0 |

| DG (A/cm <sup>2</sup> )                                     |                    |          |          |          |          |          |          | 7.86E+02 |         |

|                                                             |                    |          |          |          |          |          |          |          |         |

| V <sub>dd</sub> : Power Supply Voltage (V) [6]              | 1.1                | 1.1      | 1.1      | 1        | 1        | 1        | 1        | 0.9      | 0.9     |

| V <sub>t.sat</sub> : Saturation Threshold Voltage [7]       |                    |          |          |          |          |          |          |          |         |

| Extended Planar Bulk (mV)                                   | 195                | 168      | 165      | 160      | 159      | 151      | 146      | 148      |         |

| UTB FD (mV)                                                 |                    |          |          | 169      | 168      | 167      | 170      | 166      | 167     |

| DG (mV)                                                     |                    |          |          |          |          |          | 181      | 184      | 185     |

| Isd leak: Source/Drain Subthreshold Off-State Le            | akase Curr         | ent [8]  |          |          |          |          |          |          |         |

| Extended Planar Bulk (µA/µm)                                | 0.06               | 0.15     | 0.2      | 0.2      | 0.22     | 0.28     | 0.32     | 0.34     |         |

| UTB FD (µA/µm)                                              | 0.00               | 0.10     | V.2      | 0.17     | 0.19     | 0.22     | 0.22     | 0.29     | 0.29    |

|                                                             | 2                  |          |          | V.11     | 0010     | Villa B  | 0.22     | 0.120    | 0.20    |

# ••• ITRS (2005)

| Year of Production                                                           | 2014     | 2015     | 2016                                      | 2017     | 2018                                                                                                            | 2019               | 2020   |

|------------------------------------------------------------------------------|----------|----------|-------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------|--------------------|--------|

| DRAM ½ Pitch (nm) (contacted)                                                | 28       | 25       | 22                                        | 20       | 18                                                                                                              | 16                 | 14     |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)(contacted)                                | 28       | 25       | 22                                        | 20       | 18                                                                                                              | 16                 | 14     |

| MPU Physical Gate Length (nm)                                                | 11       | 10       | 9                                         | 8        | 7                                                                                                               | 6                  | 6      |

| Lg: Physical Lgate for High Performance logic (nm) [1]                       | 11       | 10       | 9                                         | 8        | 7                                                                                                               | 6                  | 5      |

| EOT: Equivalent Oxide Thickness [2]                                          |          |          |                                           |          |                                                                                                                 |                    |        |

| Extended planar bulk (Å)                                                     |          |          |                                           |          |                                                                                                                 |                    |        |

| UTB FD (Å)                                                                   | 5        | 5        |                                           |          |                                                                                                                 |                    |        |

| DG (Å)                                                                       | 6        | 6        | 5                                         | 5        | 5                                                                                                               | 5                  | 5      |

| Gate Poly Depletion & Inversion-Layer Thickness [3]                          |          |          | da ang ang ang ang ang ang ang ang ang an |          | 2023 - 1925 - 1925 - 1925 - 1925 - 1925 - 1925 - 1925 - 1925 - 1925 - 1925 - 1925 - 1925 - 1925 - 1925 - 1925 - | Now of the second  |        |

| Extended planar bulk (Å)                                                     |          |          |                                           |          |                                                                                                                 |                    |        |

| UTB FD (Å)                                                                   | 4        | 4        |                                           |          |                                                                                                                 |                    |        |

| DG (Å)                                                                       | 4        | 4        | 4                                         | 4        | 4                                                                                                               | 4                  | 4      |

| EOT <sub>elec</sub> : Electrical Equivalent Oxide Thickness in inversion [4] | 1        |          | 20 V. V. V.                               |          |                                                                                                                 | ka seren a seren a |        |

| Extended Planar Bulk (Å)                                                     |          |          |                                           |          |                                                                                                                 | C. 22              |        |

| UTB FD (Å)                                                                   | 9        | 9        |                                           | 1        |                                                                                                                 |                    |        |

| DG (Å)                                                                       | 10       | 10       | 9                                         | 9        | 9                                                                                                               | 9                  | 9      |

| I <sub>g.limit</sub> : Maximum gate leakage current density [5]              |          |          |                                           |          |                                                                                                                 |                    |        |

| Extended Planar Bulk (A/cm <sup>2</sup> )                                    |          |          |                                           |          |                                                                                                                 |                    |        |

| FDSOI (A/cm <sup>2</sup> )                                                   | 3.27E+03 | 3.70E+03 |                                           |          |                                                                                                                 |                    |        |

| DG (A/cm <sup>2</sup> )                                                      | 1.00E+03 | 1.10E+03 | 1.22E+03                                  | 1.38E+03 | 1.57E+03                                                                                                        | 1.83E+03           | 2.20E+ |

| $V_{dd}$ : Power Supply Voltage (V) [6]                                      | 0.9      | 0.8      | 0.8                                       | 0.7      | 0.7                                                                                                             | 0.7                | 0.7    |

| V <sub>t,sat</sub> : Saturation Threshold Voltage [7]                        |          | a        |                                           |          | 2                                                                                                               | y                  |        |

| Extended Planar Bulk (mV)                                                    |          |          |                                           |          |                                                                                                                 |                    |        |

| UTB FD (mV)                                                                  | 164      | 166      | 1                                         |          |                                                                                                                 |                    |        |

| DG (mV)                                                                      | 190      | 192      | 195                                       | 200      | 201                                                                                                             | 205                | 208    |

| Isd, leak: Source/Drain Subthreshold Off-State Leakage Current [8            | 1        |          |                                           |          |                                                                                                                 |                    |        |

| Extended Planar Bulk (µA/µm)                                                 |          |          |                                           |          |                                                                                                                 |                    |        |

| UTB FD (µA/µm)                                                               | 0.36     | 0.37     |                                           |          |                                                                                                                 |                    |        |

| CONTRACTOR AND A DESCRIPTION                                                 | 0.30     | 0.37     |                                           |          |                                                                                                                 |                    |        |

#### Red brick wall

o Introduction

o Current technology

o Next generation

o 20 years from now

o Conclusion

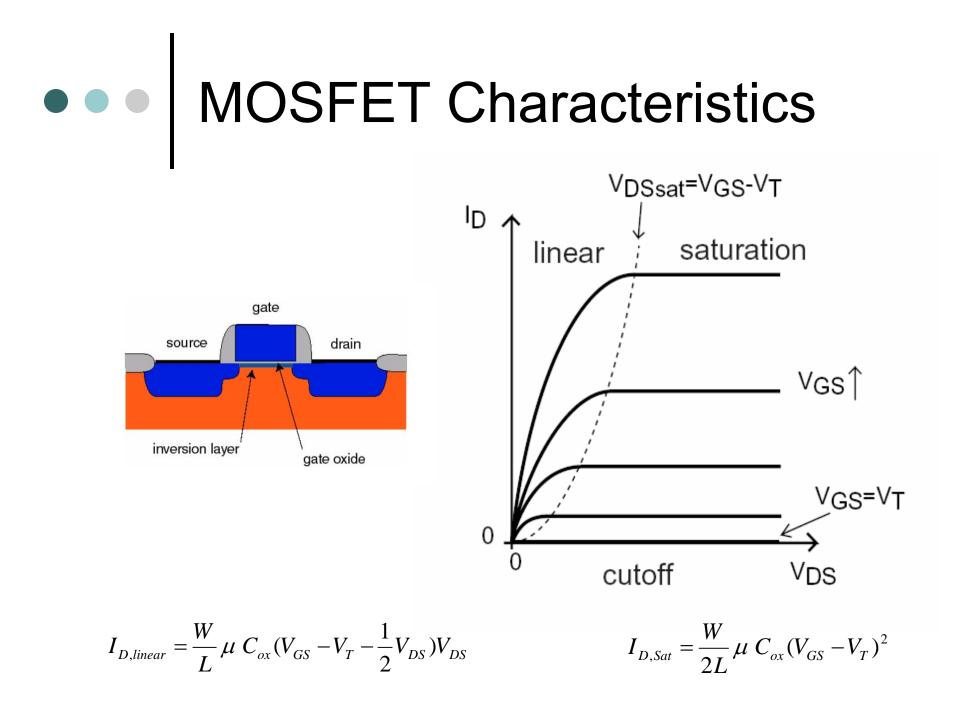

$$I_{D,linear} = \frac{W}{L} \mathcal{L} \mathcal{O}_{ox} (V_{GS} - V_T - \frac{1}{2} V_{DS}) V_{DS}$$

$$I_{D,Sat} = \frac{W}{2L} (\mu C_{ox} (V_{GS} - V_T)^2)$$

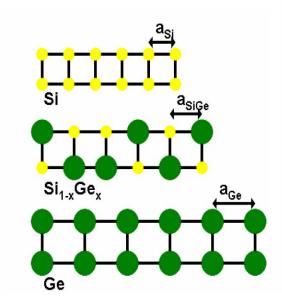

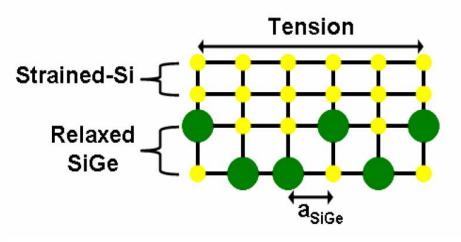

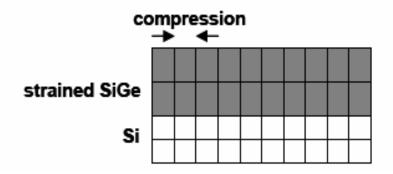

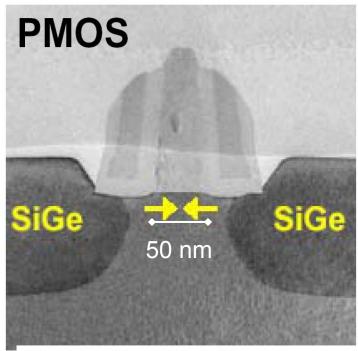

$\mu_e$  increases for tensile strain  $\mu_h \text{ increases for compressive strain}$

Nitride film causes tensile stress in channel  $\rightarrow$  increase  $\mu_e$

SiGe causes compressive stress in channel  $\rightarrow$  increase  $\mu_h$

Can induce stress for both nMOS and pMOS on the same wafer!

Introduction

Current technology

Next generation

20 years from now

Conclusion

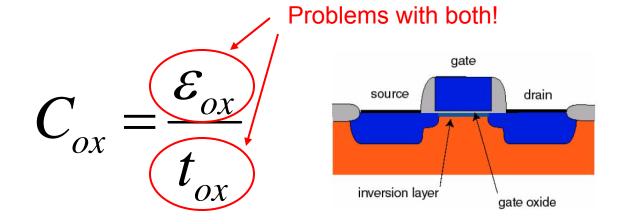

$$I_{D} = \frac{W}{L} \mu (C_{ox}) (V_{GS} - V_{T} - \frac{1}{2} V_{DS}) V_{DS}$$

$$I_D = \frac{W}{2L} \mu (C_{os} - V_T)^2$$

#### • SiO<sub>2</sub>: How do I love thee? Let me count the ways...

- Native oxide for Si  $\rightarrow$  easy to grow

- Good quality: resistant to water, other atmospheric elements

- Matches Si lattice well → no dangling bonds

- High breakdown voltage

•

$$\varepsilon_{SiO2} = 3.9^* \varepsilon_0$$

## High-к (k, if you're lazy)

- Measured in terms of "equivalent oxide thickness" (EOT)

- Can make thicker layers

If  $\kappa = 16$ , can have a thickness of 4 nm that gives roughly the same  $C_{ox}$  as 1 nm of SiO<sub>2</sub>.

# • • • SiO<sub>x</sub>N<sub>y</sub>

- Relatively easy to integrate (just add some N<sub>2</sub>)

- o Increases κ a bit ( $\kappa_{Si3N4} \sim 7$ )

- Intel introduced at 90 nm node (2004)

- Probably limited to a thickness of ~1.3 nm

- Need a better fix

#### Some Other Options

Dielectric  $\Delta E_C$  (eV) Crystal Band gap  $E_G$  (eV) to Si Material constant ( $\kappa$ ) structure(s)  $SiO_2$ 3.9 8.9 3.2 Amorphous Si<sub>3</sub>N<sub>4</sub> 5.1 Amorphous 7 2 Amorphous 9 8.7  $Al_2O_3$ 2.8<sup>a</sup>  $Y_2O_3$ 15 5.6 2.3<sup>a</sup> Cubic Pick  $La_2O_3$ 4.3 2.3<sup>a</sup> Hexagonal, cubic 30 me!  $Ta_2O_5$ 26 4.5 1 - 1.5Orthorhombic TiO<sub>2</sub> 3.5 Tetrag.<sup>c</sup> (rutile, anatase) 80 1.2 Mono.<sup>b</sup>, tetrag.<sup>c</sup>, cubic HfO<sub>2</sub> 25 5.7  $1.5^{a}$ Mono.<sup>b</sup>, tetrag.<sup>c</sup>, cubic ZrO<sub>2</sub> 25 7.8  $1.4^{a}$

TABLE I. Comparison of relevant properties for high- $\kappa$  candidates.

<sup>a</sup>Calculated by Robertson (See Ref. 153).

<sup>b</sup>Mono.=monoclinic.

<sup>c</sup>Tetrag.=tetragonal.

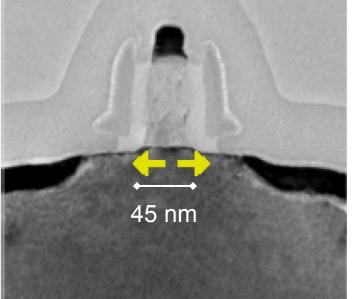

### Intel's Announcement

- Jan. 27, 2007, New York Times: 45 nm process (in production later this year) will use Hf-based dielectric (HfO<sub>2</sub>? Si-based alloy? Shhhh...) and metal gate

- Leakage current is down, drive current is up, power consumption is down

- IBM: Hey, we did it too!

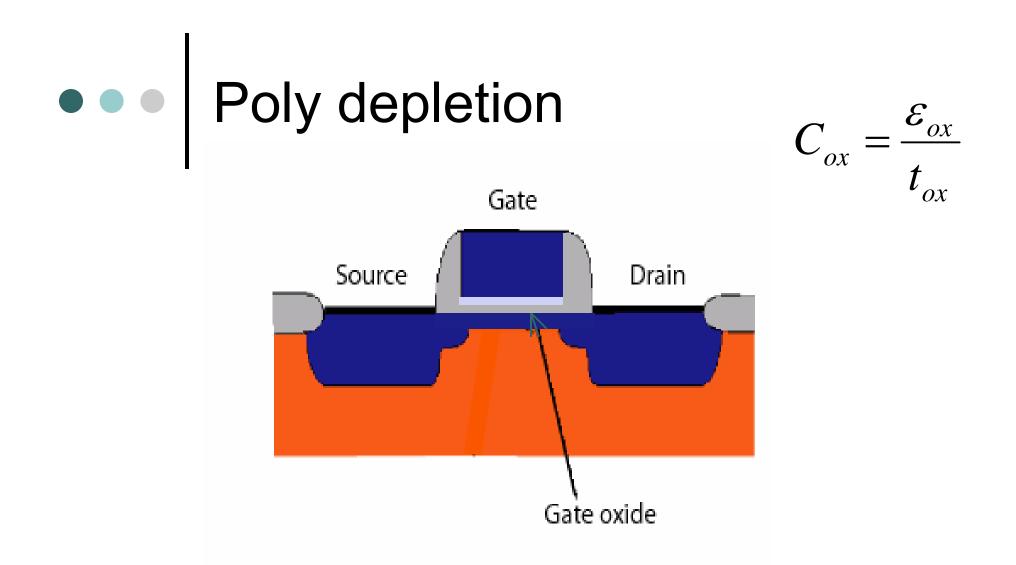

- Currently: gates made from poly-Si

- Doped at >10<sup>20</sup> cm<sup>-3</sup>

- Pro: same material for nMOS and pMOS

- Cons: Can only dope so high, poly depletion effects

Deplete 3 – 4 Å in the gate  $\rightarrow$  adds 3 – 4 Å to dielectric (significant when dielectric is 12 Å)  $\rightarrow$  reduces C<sub>ox</sub>

No poly depletion

Lower series resistance

Different for nMOS and pMOS

Incorporating SiGe, Hf-based dielectric, and metal gates show that the industry is willing to (slowly) incorporate new materials

- o Introduction

- o Current technology

- o Next generation

- o 20 years from now

- o Conclusion

# Look at bigger picture

• What if we change the mode of transportation entirely?

- Tunneling FET (TFET)?

- Carbon nanotubes?

- Computation bubbles?

- PHOTONICS!

- Before we go crazy-nuts, should probably look into a hybrid system

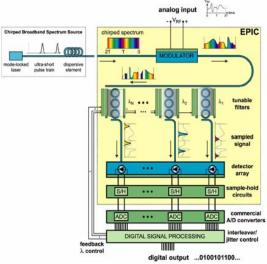

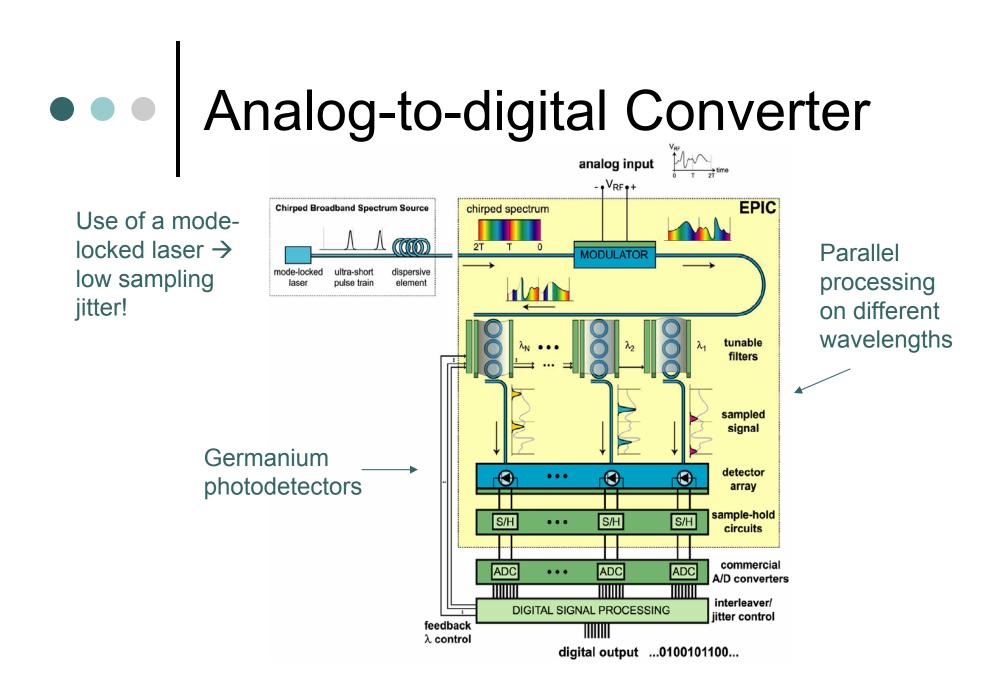

#### Integrated electronic/photonic system

Photonics are good for transmitting data, high frequency applications

$\bullet \bullet \bullet$

- Electronics are good for processing data, especially in a small area

- Let's use both!

## But still Si-based

- Everything on-chip  $\rightarrow$  faster!

- Integrate laser

- Si modulator

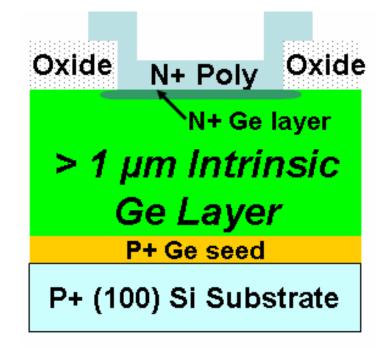

- Ge photodetectors

- SiGe already in CMOS process

- SiO<sub>2</sub> and SiN<sub>x</sub> waveguides

- Already in CMOS process

- Key: Optical sampling drastically reduces the timing jitter

## • • Germanium photodiode

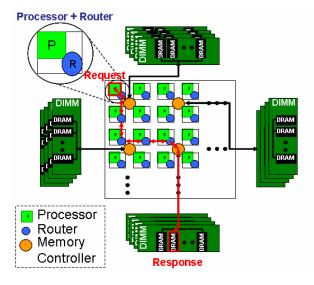

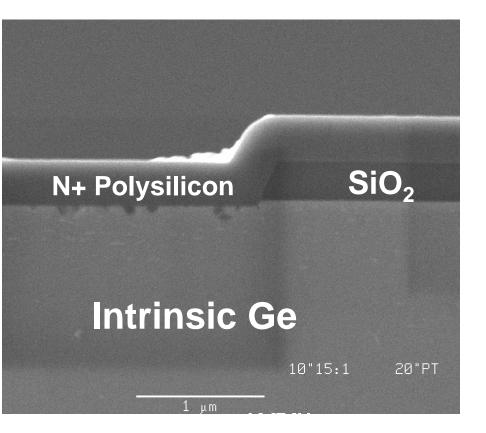

# Another system: Multi-core Processor

- Working within an existing CMOS process

- Materials constraints

- Process constraints

- Pros: 1,000 cores, much more energy efficient, faster

- Devices: 6.012, 6.720J, 6.728, 6.730, 6.731

- Processing: 6.152J, 6.774, 6.781

- o Optics/Photonics: 6.013, 6.630, 6.631

- o Circuits: 6.002, 6.301

- Computer Architecture: 6.823

## • • Groups at MIT

- Strain engineering Hoyt, Fitzgerald

- o High-κ materials Antoniadis

- Electronic Photonic Integrated Circuits (EPIC) – Kaertner, Hoyt, Ram, H.I.

Smith, Ippen

- Multi-core processor Stojanovic, Asanovic, Hoyt, Ram, Kaertner, H.I. Smith, Schmidt

# • • Conclusions

- "No exponential is forever, but we can delay 'forever."

- New materials: whoo!

- Electronic photonic architectures: whoo!