## FA 14.3: A Low-Power Differential CMOS Bandgap Reference

Todd L. Brooks \*, Alan L. Westwick

Telecom Operations, Motorola, Austin, TX

\*Now with Analog Devices, Wilmington, MA

The performance of many mixed analog/digital systems is limited by inaccuracies and power supply noise coupling errors in integrated voltage references [1, 2]. Reference circuitry also typically contributes a large fraction of the analog power consumption. The CMOS bandgap circuit described here provides a 2.0V differential voltage reference for a 10.24MHz oversampled data converter, and maintains high PSR and accuracy while consuming 2.2mW.

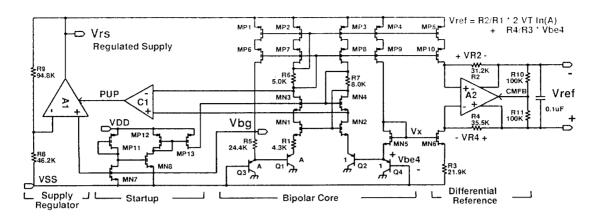

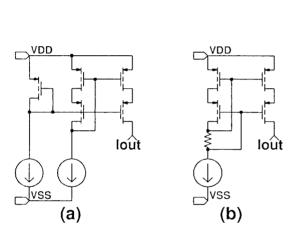

The bandgap reference is shown in Figure 1. A single bipolar core circuit establishes a PTAT reference current, a single-ended bandgap voltage,  $V_{\rm bg}$ , with respect to ground, and an additional voltage,  $V_{\rm x}$ , used in the differential reference. Both p-channel and n-channel devices,  $M_{\rm Pl}-M_{\rm P4}$  and  $M_{\rm N1}-M_{\rm N2}$ , are cascoded to improve the PSR. A conventional high-swing cascode current mirror, shown in Figure 2a, requires power-consuming cascode bias circuitry. A self-biasing high-swing cascode technique, illustrated in Figure 2b, uses a resistor to develop a bias voltage. The voltage drop across the resistor is maintained slightly larger than  $V_{\rm DSAT}$  of the cascode devices. This ensures that the mirror devices operate near the edge of the saturation region, providing low-voltage operation with high output impedance. Resistors  $R_{\rm 6}$  and  $R_{\rm 7}$ , implemented in the bipolar core circuit of Figure 1, provide bias voltages for cascode devices  $M_{\rm P6}-M_{\rm P10}$  and  $M_{\rm N3}-M_{\rm N4}$ , respectively.

The differential reference voltage is generated by sourcing a current with positive temperature coefficient from  $M_{ps}$  and M<sub>P10</sub> into resistor R<sub>2</sub> and sinking a current with negative temperature coefficient into  $M_{N6}$  from resistor  $R_4$ . The current in M<sub>P5</sub> and M<sub>P10</sub> is mirrored from the PTAT current flowing in bandgap core transistors  $M_{P2}$  and  $M_{P7}$ . Resistor  $R_2$  develops a voltage drop,  $V_{R2}$ , proportional to the thermal voltage of the bipolar transistors. The current in  $M_{N6}$  is proportional to the base-emitter voltage,  $V_{be4}$ , of transistor  $Q_4$  by using large matched devices for  $M_{NS}$  and  $M_{N6}$  to establish a voltage drop equal to  $V_{be4}$  across resistor  $R_3$ . Resistor  $R_4$  develops a voltage drop,  $V_{R4}$ , proportional to  $V_{bet}$ . Amplifier  $A_2$  maintains equal voltages at the drains of  $M_{p_{10}}$  and  $M_{N6}$  and establishes a temperature-independent voltage,  $V_{rep}$  at its output equal to the sum of  $V_{R2}$  and  $V_{R4}$ . Common-mode feedback in  $A_2$  maintains a constant common-mode level in the output. Although the input common-mode level varies with temperature, the impact on  $V_{ref}$  is less than 2ppm/°C with an amplifier CMRR of only 60dB. Direct scaling of V<sub>ref</sub> is by adjusting the values of R<sub>2</sub> and R<sub>4</sub> relative to R<sub>1</sub> and R<sub>3</sub>, respectively. The ratio of R<sub>1</sub> to R<sub>3</sub> is adjusted to null the reference temperature coefficient, allowing R<sub>2</sub> and R<sub>4</sub> to have similar values for differential matching.

The PSR advantages of differential circuit implementation are obtained with little additional circuit complexity and power consumption. The simplicity of the amplifier feedback circuitry makes amplifier settling time independent of the high-frequency characteristics of the parasitic pnp transistors in the CMOS process. In contrast, many continuous-time reference circuits use parasitic pnp devices and current mirror circuitry in the feedback network around an operational amplifier. The settling time of switched-capacitor bandgap circuits is also typically limited by the parasitic pnp characteristics.

Supply regulation is added to improve the low-frequency PSR

of the differential reference within the 40kHz signal bandwidth of the oversampled data converter. A 4V regulated supply is generated by amplifying the bandgap voltage,  $V_{\rm bg}$ , using amplifier  $A_1$ . This feature is implemented at the minimal expense of a 500mV drop in the minimum 4.5V supply voltage and of 500µW of additional power consumption in amplifier  $A_1$ . Startup circuitry is added to ensure that  $V_{\rm bg}$  and the regulated supply do not remain at ground when power is applied. Comparator  $C_1$  provides a power-up signal to amplifier  $A_1$ , forcing the amplifier output equal to  $V_{\rm DD}$  during startup conditions.

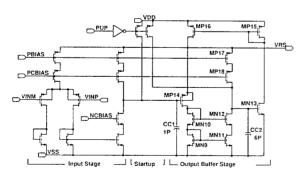

Supply regulation amplifier  $A_1$  in Figure 3 uses a low-power output stage optimized for high PSR. Current in the drain of source follower device  $M_{\rm P14}$  is amplified using devices  $M_{\rm N9}$ - $M_{\rm N13}$  and mirrored back into the source of  $M_{\rm P14}$  to close the negative feedback loop. The resulting low-impedance Class AB buffer stage sources and sinks large output currents. The negative feedback maintains constant current in source-follower device  $M_{\rm P14}$ , boosting its transconductance and decreasing its output impedance by a factor of 1+A, where A, is the current gain of the feedback circuit. Capacitors  $C_{\rm C1}$  and  $C_{\rm C2}$  give frequency compensation without the high-frequency PSR degradation of conventional Miller-compensated two-stage amplifiers [3].

Differential reference amplifier  $A_2$  uses complementary output buffer structures similar to those in  $A_1$ , with source follower buffer devices at amplifier outputs placed in local feedback for enhanced large-signal current drive, class AB operation, and reduced output impedance. Amplifier  $A_2$  is for use with a  $0.1 \mu F$  regulation capacitor across the amplifier outputs for low output impedance at the 10.24 MHz data converter clock rate.

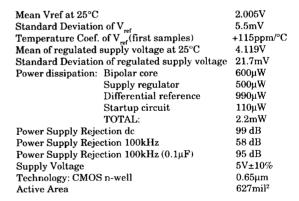

Device matching errors contributing to reference variation are minimized by common-centroid layout. Devices are sized to minimize device variations and the reference sensitivities to these variations, and more layout area is allotted to devices causing greater reference variation. Table 1 summarizes performance of the bandgap reference. Statistics for the reference and regulated supply voltages are from a sample of 30 parts from the first wafer lot of an uncharacterized process.

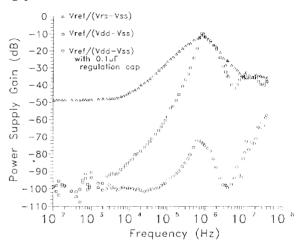

Three sets of supply rejection data for the differential reference are given in Figure 4: reference by itself, reference with supply regulation, and reference with both supply regulation and 0.1  $\mu F$  output capacitor. Supply noise between 40 kHz and 10.20 MHz is removed by a filter following the data converter and does not affect system performance. Rejection is at least 79 dB over frequencies of interest when the circuit is used with regulated supply and  $0.1 \mu F$  capacitor across reference outputs.

## Acknowledgments

The authors thank M. Rybicki and the Telecom design team for guidance and support, J. Guevara for layout design, and C. Mangelsdorf, I. Miller, and B. Martino for advice.

## References

- [1] Ferro, M., et al., "A Floating CMOS Bandgap Voltage Reference for Differential Applications," IEEE J. Solid-State Circuits, vol. 24, pp. 690-697. Jun. 1989.

- [2] Nicollini, G., D. Senderowicz, "A CMOS Bandgap Reference for Differential Signal Processing," IEEE J. Solid-State Circuits, vol. 26, pp. 41-50, Jan. 1991.

- [3] Ahuja, B. K., "An Improved Frequency Compensation Technique for CMOS Operational Amplifiers," IEEE J. Solid-State Circuits, vol. SC-18, pp. 629-633, Dec. 1983.

Figure 1: Bandgap reference.

Figure 2: High-swing cascode current mirror.; (a) conventional, (b) self-biased.

Figure 4: Measured power supply rejection of differential reference.

Figure 5: See page 346.

Figure 3: Supply regulation amplifier A1.

Table 1: Performance summary.