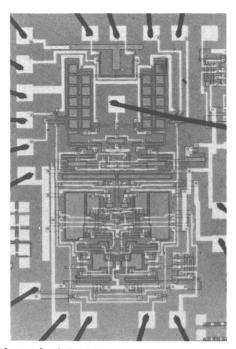

## The Design of High-Performance Analog Circuits on Digital CMOS Chips

ERIC A. VITTOZ, MEMBER, IEEE

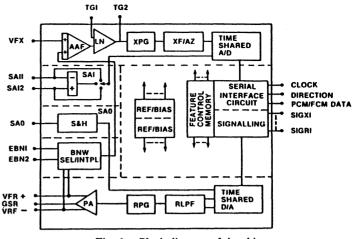

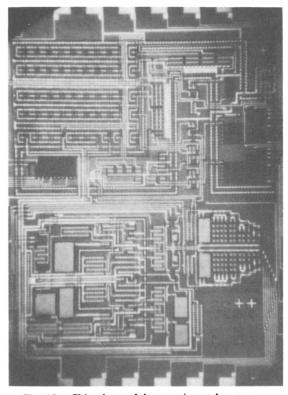

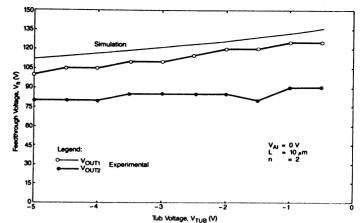

Abstract — Devices available in digital oriented CMOS processes are reviewed, with emphasis on the various modes of operation of a standard transistor and their respective merits, and on additional specifications required to apply devices in analog circuits. Some basic compatible analog circuit techniques and their related tradeoffs are then surveyed by means of typical examples. The noisy environment due to cohabitation on the chip with digital circuits is briefly evoked.

## I. INTRODUCTION

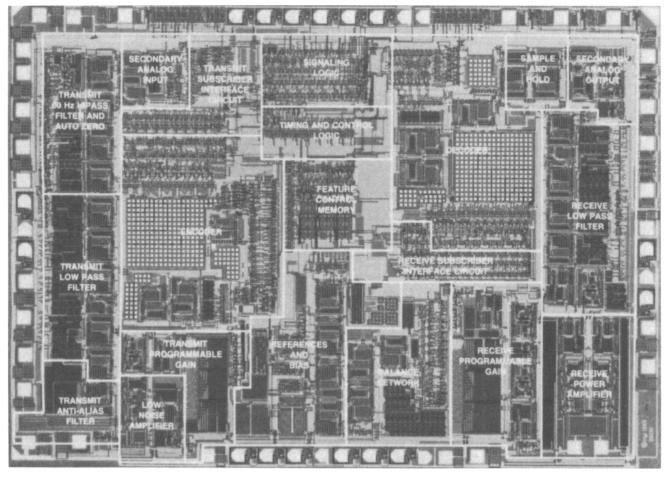

THE EVOLUTION of scaled-down digital processes will shift the boundary between digital and analog parts of systems [1]. However, analog circuits will remain irreplaceable components of systems-on-a-chip. Besides A/D conversion, they will always be needed to perform a variety of critical tasks required to interface digital with the external world, such as amplification, prefiltering, demodulation, signal conditioning for line transmission, for storage, and for display, generation of absolute values (voltages, currents, frequencies), and to implement compatible sensors on chip. In addition, analog will retain for a long while its advantage over digital when very high frequency or very low power is required.

Most of the limitations of analog circuits are due to the fact that they operate with electrical variables and not simply with numbers. Therefore, their accuracy is fundamentally limited by unavoidable mismatches between components, and their dynamic range is limited by noise, offset, and distortions.

For economical reasons, the analog part of a system-ona-chip must be fully compatible with a process basically tailored for digital requirements, and this with a minimum number of additional specifications. Section II will review all active and passive devices available in digital CMOS processes, together with the additional specifications needed to use them for implementing analog circuits. Some basic analog circuit techniques will then be described in Section III by means of typical examples. Finally, the problems related to the noisy environment due to cohabitation on the chip with large digital circuits will be briefly evoked in Section IV.

Manuscript received November 2, 1984; revised December 24, 1984. The author is with Centre Suisse d'Electronique et de Microtechnique, (CSEM, formerly CEH) Maladiere 71, 2000 Neuchàtel 7, Switzerland.

#### II. DEVICES AVAILABLE FOR ANALOG CIRCUITS

#### A. Transistors

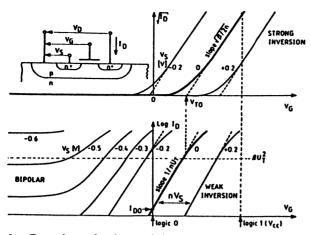

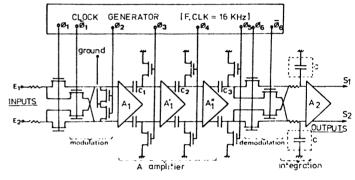

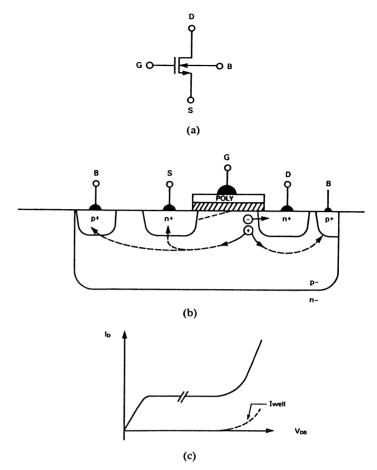

A clear understanding of the various ways of biasing a normal MOS transistor, and of their respective merits, is a key factor in the design of optimum analog subcircuits. Fig. 1 illustrates the complete transfer characteristics  $I_D(V_G)$  of a n-channel MOS transistor in saturation for various possible modes of operation. For the sake of symmetry, all potentials are defined with respect to that of the local substrate, in this case the p-well.

The general behavior of drain current in saturation  $I_D$  in the two basic modes of field effect operation can be described by two separate approximative models [2], [3] which sacrifice accuracy to clarity and simplicity:

Strong inversion  $(I_D \gg \beta U_T^2)$

$$I_{D} = \frac{\beta}{2n} (V_{G} - V_{T0} - nV_{S})^{2},$$

for  $V_{D} > V_{D \text{ sat}} = (V_{G} - V_{T0})/n.$  (1)

Weak inversion  $(I_D \ll \beta U_T^2)$

$$I_{D} = K\beta U_{T}^{2} \exp((V_{G} - V_{T0} - nV_{S})/nU_{T}),$$

for  $V_{D} > V_{D \text{ sat}} = 3 \text{ to } 4U_{T}.$  (2)

These models only include the three most important device parameters required for circuit design

$\beta = \mu C_{ox} W/L \quad \text{transfer parameter for strong inversion} \\ V_{T0} \qquad \text{gate threshold voltage for } V_S = 0$

*n* slope factor in weak inversion, which also describes approximately the effect of fixed charges in the channel in strong inversion. Its value depends slightly on  $V_s$  [3] and ranges usually from 1.3 to 2.

K is a factor somewhat larger than 1, which connects weak and strong inversion. Its exact value has no importance in circuit design, since transistors in weak inversion must be biased at fixed drain current  $I_D$  to avoid the very high sensitivity to  $U_T = kT/q$  and  $V_{T0}$  for fixed gate voltage  $V_G$ .

In CMOS logic circuits, transistors usually operate with  $V_s = 0$  as shown in heavy lines in Fig. 1. Their role is to

Reprinted from IEEE J. Solid-State Circuits, vol. SC-20, no. 3, pp. 657-665, June 1985.

Fig. 1. General transfer characteristics  $I_D(V_G)$  of a MOS transistor in saturation. Different modes of operation can be identified, namely strong inversion, weak inversion, and bipolar.

provide maximum drain current in the "on" state for  $V_G = V_{cc}$ , and minimum residual current  $I_{D0}$  in the "off" state for  $V_G = 0$ . The only requirements for digital circuits are thus a maximum possible value of transfer parameter  $\beta$ , and a value of threshold voltage  $V_{T0}$  as low as possible while ensuring acceptable value of residual current for  $V_G = 0$

$$I_{D0} = K\beta U_T^2 \exp(-V_{T0}/nU_T).$$

(3)

This is only possible if slope factor n of weak inversion is not too large. These requirements are also favorable to analog circuits, since they allow a maximum value of transconductance  $g_m$  which can be easily derived from (1) and (2) as

. ....

$$g_m = ((2\beta I_D)/n)^{1/2} = 2I_D/(V_G - V_{T0} - nV_S)$$

(strong inversion) (4)

$$g_m = I_D/nU_T$$

(weak inversion). (5)

However, specifications on the maximum range of varia-

tion of  $\beta$ ,  $V_{T0}$ , and *n* are usually necessary.

Transconductance  $g_m$  is proportional to drain current  $I_D$ in weak inversion, but only to the square root of  $I_D$  in strong inversion. If source voltage  $V_S$  is not zero, the gate voltage for constant drain current is shifted by  $nV_S$  for both modes of operation. Thus transconductance  $g_{ms}$  from source to drain is given by

$$g_{ms} = ng_m. \tag{6}$$

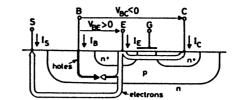

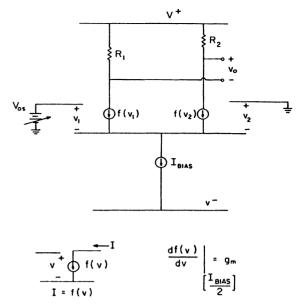

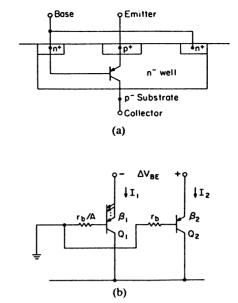

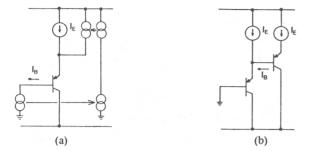

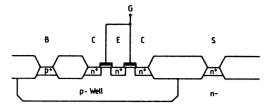

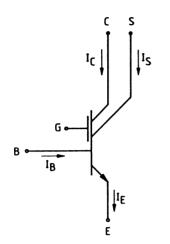

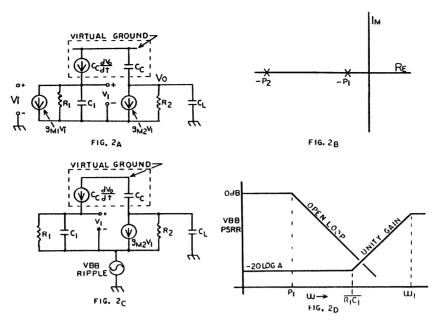

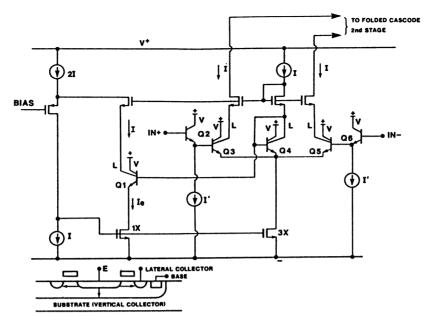

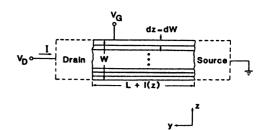

Fig. 1 also shows that when gate voltage  $V_G$  is sufficiently negative, it has not more effect on drain current, which means that gate transconductance  $g_m$  decreases to zero. However,  $I_D$  can still be controlled by negative values of source voltage  $V_S$  which corresponds to a forward-biased source junction. The device then operates as a lateral bipolar, with the flow of carriers pushed away from the surface by the negative gate potential [4]. The various flows of carriers in this mode of operation are shown in Fig. 2. Source, drain, and p-well have been renamed emitter E,

Fig. 2. Flows of carriers in bipolar operation.

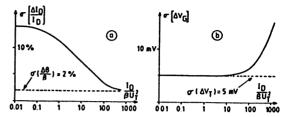

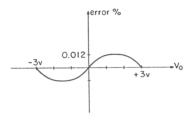

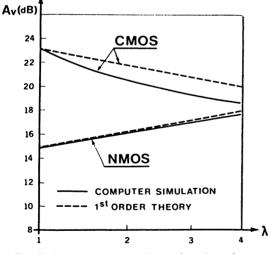

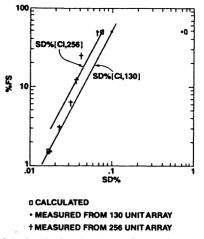

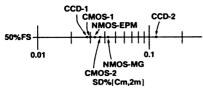

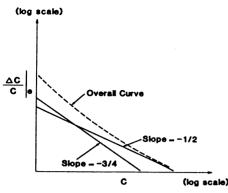

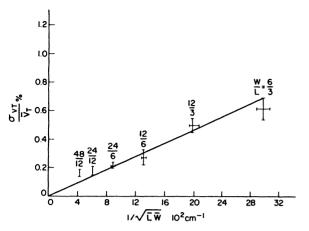

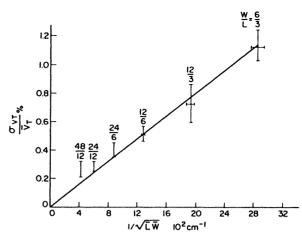

Fig. 3. Matching of a pair of MOS transistors as a function of drain current, for (a) same gate voltage and (b) same drain current. Uncorrelated components with mean standard deviations of 2 percent for  $\Delta\beta/\beta$  and 5 mV for  $\Delta V_T$  are assumed in this example.

collector C, and base B. Since a large fraction of emitter current  $I_E$  flows to substrate, the maximum alpha-gain of this lateral bipolar is only 0.2 to 0.6, depending on the process. However, owing to the low rate of recombination in the well, the  $\beta$ -gain can reach quite acceptable values ranging from 20 to 500. This high value of current gain is only obtained for the transistor implemented in the well, in this case a n-p-n. The n-p-n to substrate can be used without lateral collector, but only in common collector configurations.

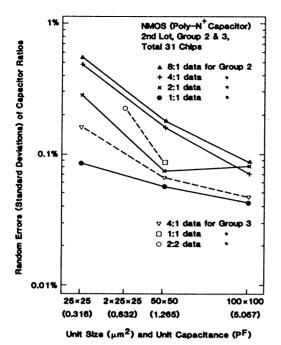

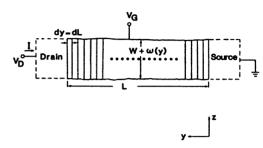

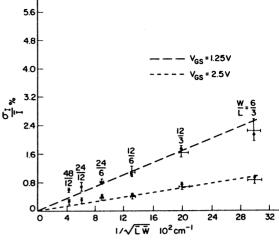

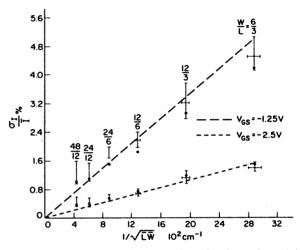

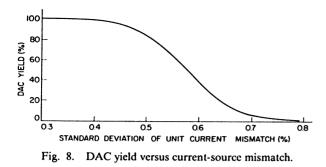

For implementing analog circuits, it is necessary to specify the matching properties of similar adjacent transistors. Matching must be characterized by two independent statistical values: threshold mismatch  $\Delta V_T$ , which may have in practice a mean standard deviation ranging from 1 to 20 mV, and  $\Delta\beta/\beta$  mismatch which is usually in the range of 0.5-5 percent. Fig. 3 shows that when two transistors have the same gate voltage, as in a current mirror, the mismatch of their drain currents

$$\Delta I_D / I_D = \Delta \beta / \beta - (g_m / I_D) \Delta V_T \tag{7}$$

is maximum in weak inversion, for which  $g_m/I_D$  is maximum, and only comes down to  $\Delta\beta/\beta$  when the transistors operate deeply in strong inversion. On the contrary, when they have the same drain current, as in a differential pair, the mismatch of their gate voltages

$$\Delta V_G = \Delta V_T - (I_D / g_m) \cdot \Delta \beta / \beta \tag{8}$$

is just  $\Delta V_T$  in weak inversion, and increases in strong inversion where  $g_m/I_D$  is reduced.

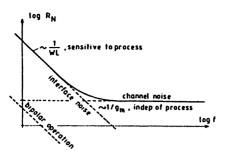

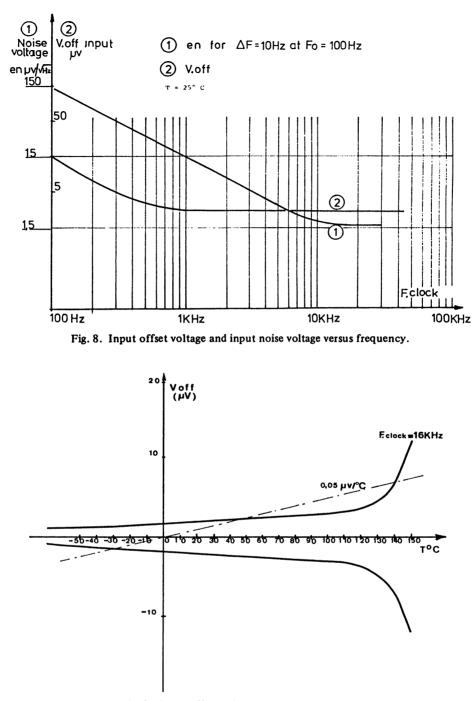

Noise is a very important limitation of most analog circuits. As shown in Fig. 4, the noise of a transistor must also be characterized by at least two independent sources: White channel noise is independent of the process and corresponds to an equivalent input noise resistance  $R_N$  approximately equal to the inverse of transconductance  $g_m$  [5]. Gate interface 1/f noise dominates at low frequencies

Fig. 4. Contributions to equivalent input noise resistance  $R_N$  of a MOS transistor.

TABLE I Specifications on Transistors for Analog and Digital Applications.

(Analog Requires Specifications on Additional Parameters, and on Maximum and Minimum Values of Some Parameters.)

| Parameter       | Digital | Analog  |

|-----------------|---------|---------|

| β               | min.    | minmax. |

| ۷ <sub>T</sub>  | max.    | minmax. |

| n               | max.    | minmax. |

| 1 <sub>D0</sub> | max.    | max.    |

| β-bipolar       |         | min.    |

| mismatch        |         | max.    |

| 1/f noise       |         | (max.)  |

| output resist.  |         | min.    |

| 1               |         |         |

and is approximately independent of drain current. It is inversely proportional to gate area, and very sensitive to process quality. It should therefore be eliminated by circuit techniques such as chopping or autozeroing [6]-[8].

Both flicker noise and threshold mismatch are drastically reduced when the transistor operates in the lateral bipolar mode [4]. This is because the device is then shielded from all surface effects.

The respective qualitative specifications on transistors for digital and analog applications are summarized in Table I. An additional requirement for analog is a high value of output resistance which is approximately proportional to channel length. Designs should be made independent of the exact value of this parameter.

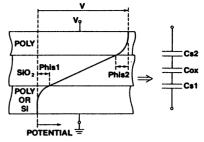

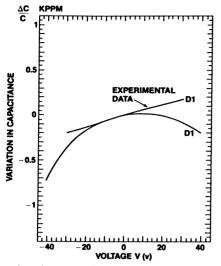

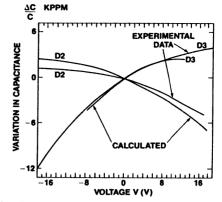

#### **B.** Passive Components

In digital CMOS circuits, passive components, namely capacitors and resistors, are only present as parasitics and should therefore by minimized. On the contrary, functional passive components of reasonable values and acceptable quality are required in most analog subcircuits.

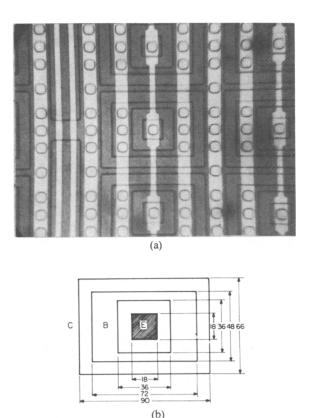

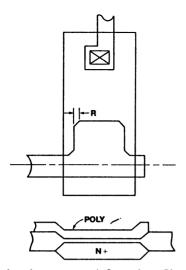

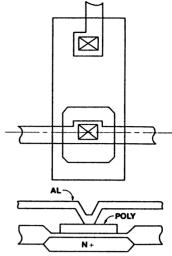

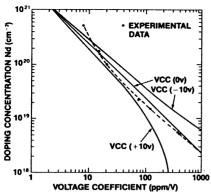

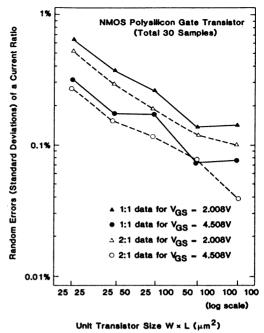

Excellent precision capacitors can be implemented in a compatible way by using the silicon dioxide dielectric, provided both electrodes have a sufficiently low resistivity. Thin oxide gate capacitors are available in metal gate technologies, but they cannot be implemented in Si-gate processes without additional steps. For processes with a single polysilicon layer, the only reasonable choice is the

capacitor between aluminum and polysilicon layers [9], which usually achieves rather low specific values. Many modern technologies provide two layers of polysilicon that can be used as electrodes for the capacitors [10].

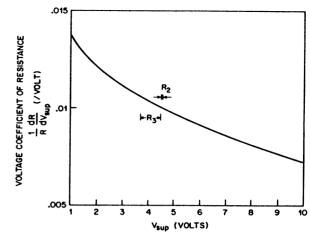

Good resistors of less than 100  $\Omega$ /sq. can be obtained in the polysilicon layer. Higher values of few kiloohms per square are possible by using the well diffusion, but these resistors are slightly voltage dependent, and they are always associated with a large parasitic capacitance. Lightly doped polysilicon resistors such as those used to implement quasi-static RAM's [11] achieve very high values but they have a very poor accuracy.

Most of the modern design techniques for analog circuits are based on ratios of capacitances or resistances, and therefore only require specifications on matching and linearity of passive devices. If absolute values are needed as well, data on spread, temperature behavior, and aging must be available, and must be ensured by periodic statistical measurements.

No floating diode is usually available, except the baseemitter junction of the bipolar transistor to substrate. Some special micropower processes offer a lateral diode in the polysilicon layer [12].

#### III. BASIC ANALOG CIRCUIT TECHNIQUES

#### A. Optimum Matching

Most analog circuit techniques are based on the matching properties of similar components. For a given process, matching of critical devices may be improved by enforcing the set of rules that are summarized in Table II. These rules are not specific to CMOS and are applicable to all kinds of IC technologies. The relevancy and the quantitative importance of each of these rules depend on the particular process and on the particular device under consideration.

1) Devices to be matched should have the same structure. For instance, a junction capacitor cannot be matched with an oxide capacitor. This also means that the error due to parasitic junction capacitors cannot be compensated by adjusting the value of functional oxide capacitors.

2) They should have same temperature, which is no problem if power dissipated on chip is very low. Otherwise, devices to be matched should be located on the same isotherm, which can be obtained by a symmetrical implementation with respect to the dissipative devices.

3) They should have same shape and same size. For example, matched capacitors should have same aspect ratios, and matched transistors or resistors should have same width and same length, and not simply same aspect ratios.

4) Minimum distance between matched devices is necessary to take advantage of spatial correlation of fluctuating physical parameters.

5) Common-centroid geometries should be used to cancel constant gradients of parameters. Good practical examples

TABLE II Rules for Optimum Matching

1. Same structure

- 2. Same temperature

- 3. Same shape, same size

- 5. Common-centroid geometries

- 6. Same orientation

- 7. Same surrounding

- 8. Non minimum size

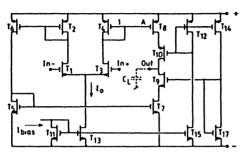

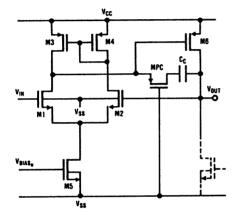

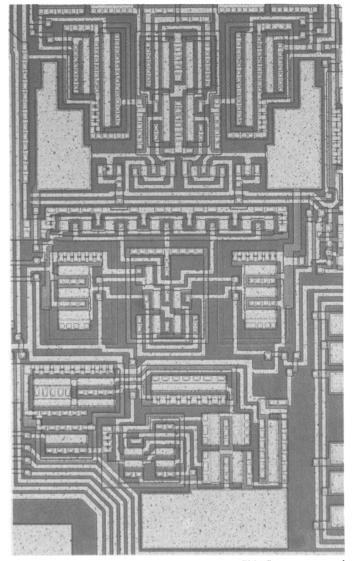

Fig. 5. Single-stage cascode operational transconductance amplifier (OTA) [13].

are the quad configuration used to implement a pair of transistors, and common-centroid sets of capacitors.

6) The same orientation on chip is necessary to eliminate dissymmetries due to unisotropic steps in the process, or to the unisotropy of the silicon substrate itself. In particular, the source to drain flows of current in matched transistors should be strictly parallel.

7) Devices to be matched should have the same surroundings in the layout. This to avoid for instance the end effect in a series of current sources implemented as a line of transistors, or the street effect in a matrix of capacitors.

8) Using nonminimum size is an obvious way of reducing the effect of edge fluctuations, and to improve spatial averaging of fluctuating parameters.

Matching can be extended to the realization of non-unity n/m ratios by separately grouping m and n matched devices. A slight alteration of one or many devices is necessary when intermediate ratios are required.

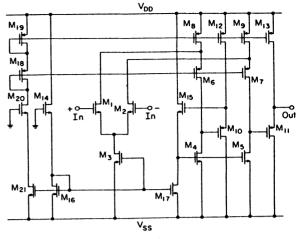

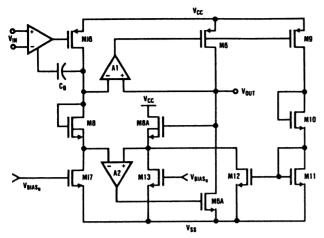

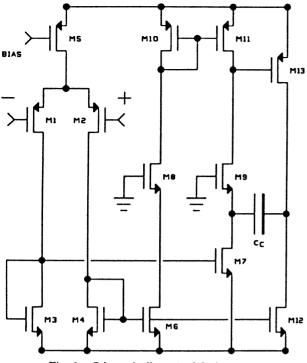

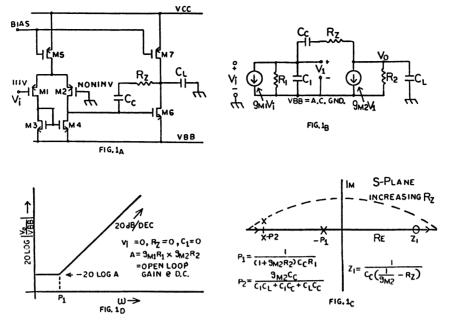

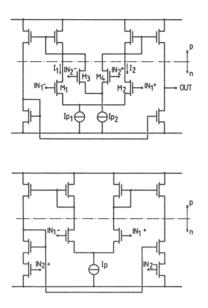

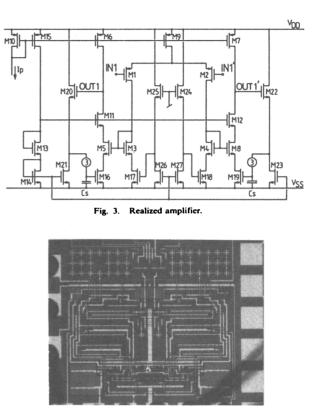

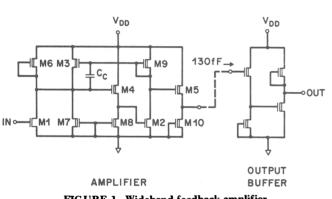

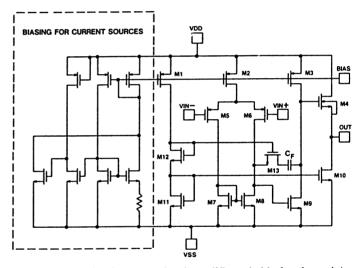

## **B.** Amplifiers

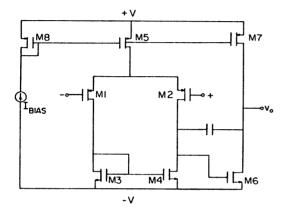

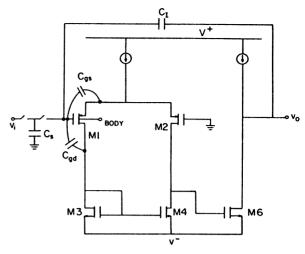

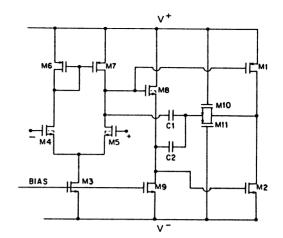

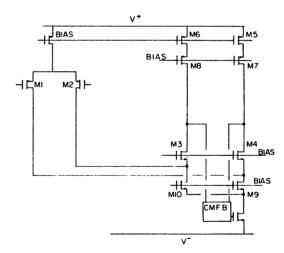

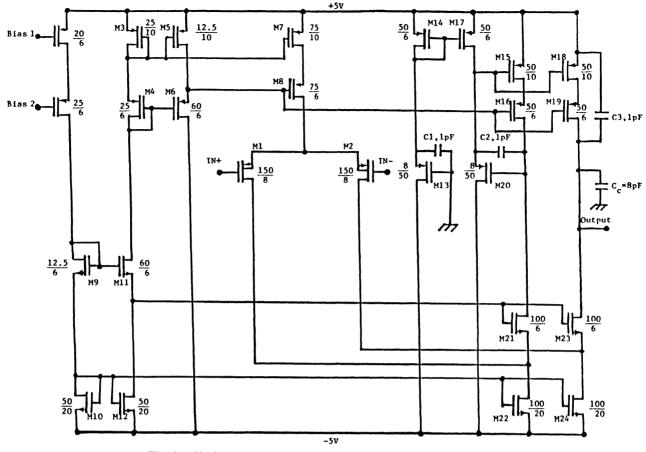

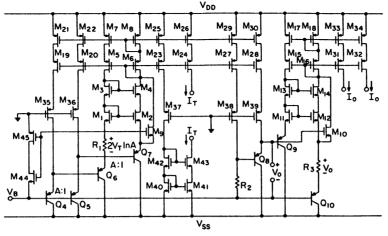

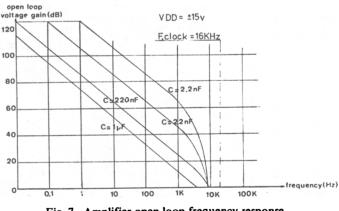

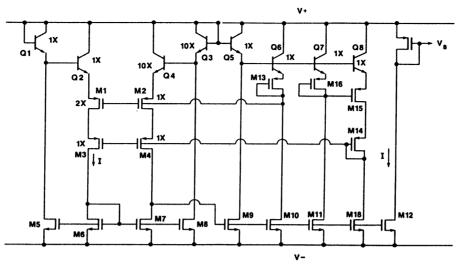

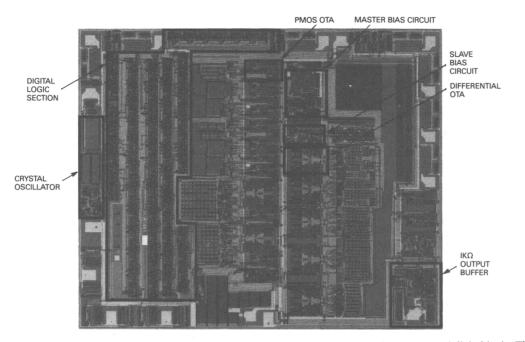

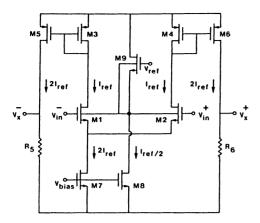

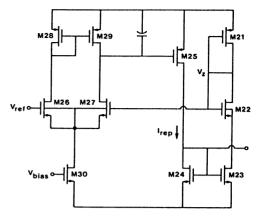

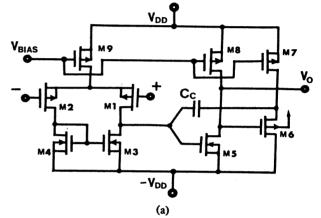

The basic configurations and tradeoffs related to the realization of amplifiers can be discussed with the example of a single-stage cascode OTA represented in Fig. 5 [13].

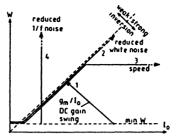

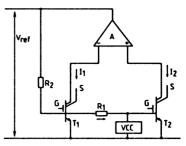

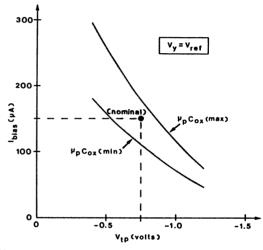

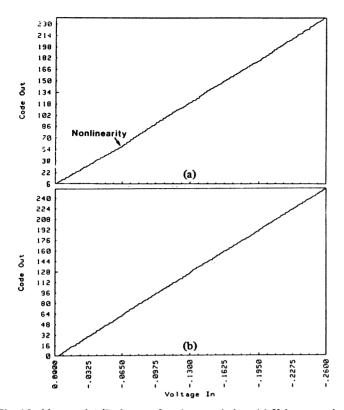

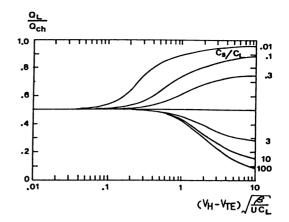

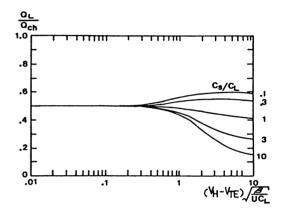

Differential pair  $T_1 - T_3$  converts the differential input voltage into a difference of currents which is integrated in load capacitance  $C_L$ . These transistors can have minimum channel length since they are loaded by the high input conductance of current mirrors. Remaining design parameters are then channel width W and value of tail current  $I_0$ . Optimization of this input pair therefore amounts to choosing the best possible point in the  $(W, I_0)$  plane, with respect to conflicting requirements. This plane is represented in Fig. 6, with the limit between weak and strong inversion which corresponds to a given value of  $W/I_0$ .

Fig. 6. Optimization of width W and tail current  $I_0$  of input pair  $T_1 - T_3$ . Arrowed paths 1 to 4 indicate displacements in plane  $(W, I_0)$  for maximum improvement of various features of the amplifier.

Displacements in the plane for maximum improvement of various important features of the whole amplifier are represented in a qualitative way.

Transconductance for a given current, dc gain, and maximum possible swing are all improved by increasing  $W/I_0$  to approach weak inversion, where they reach their maximum values (path 1). This also reduces input offset voltage.

The white noise spectral density is inversely proportional to transconductance  $g_m$ , which increases linearly with current  $I_0$  up to the upper limit of weak inversion. To keep the advantages of weak inversion, a further increase of  $g_m$ requires a parallel increase of width W and current  $I_0$ (path 2), which is only limited by size.

Speed (path 3) is proportional to  $g_m$  as long as parasitic capacitances of the transistors (proportional to W) are constant or negligible. A further increase in speed requires a progressive incursion into strong inversion, which results in progressive degradations of dc gain and of maximum possible swing. Speed in strong inversion only increases with the square root of current.

Low frequency 1/f noise is reduced by increasing channel width (path 4) and by choosing the better type of transistor, which is usually a p-channel.

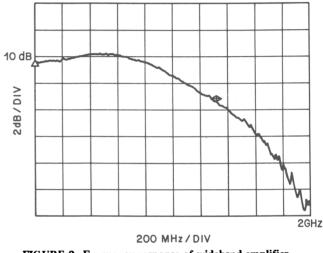

If input current can be tolerated, very low 1/f noise and very high speed can be achieved by using transistors operated as lateral bipolars [4], [14].

The maximum differential current available from the pair is equal to tail current  $I_0$ , which puts a fundamental limit to slew rate. This problem can be circumvented by momentarily increasing current  $I_0$  by a fixed amount each time an input step is anticipated, which yields a dynamic amplifier [15]. It can also be increased by an amount proportional to the difference of drain currents to realize an adaptive bias [16], [17], which provides operation in class *AB*.

Complementary pairs  $T_1 - T_2$  and  $T_3 - T_4$  can be viewed as common emitter amplifiers, each of which amplifies half of the total differential input voltage. Gain  $g_{m1,3}/g_{m2,4}$ must be high enough, of the order of 3 to 10, to have noise and offset voltage limited to the only contribution of the differential input pair. This requires operation of transistors  $T_2$  and  $T_4$  deep enough into strong inversion. Too much gain reduces the stability phase margin.

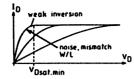

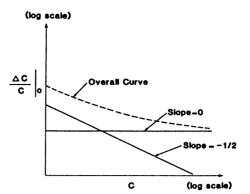

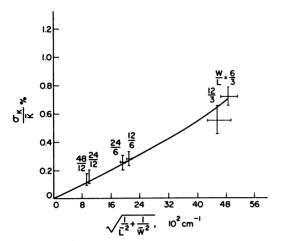

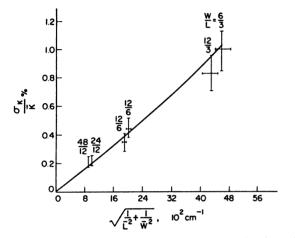

As was illustrated by Fig. 3, the mismatch of current mirrors is maximum in weak inversion. It can be shown

Fig. 7. Optimization of W/L of current mirrors.

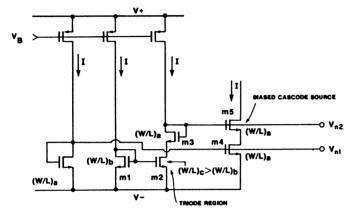

that this is true as well for both white and 1/f noise [18]. However, according to relations (1) and (2), weak inversion provides the minimum possible value of drain saturation voltage of the order of 100 mV. Therefore, the optimization of W/L of current mirrors  $T_{11} - T_{13} - T_{15}$ ,  $T_2 - T_6$ ,  $T_4 - T_8$ ,  $T_5 - T_7$  amounts to an acceptable compromise between small mismatch and low noise ( $V_G - V_{T0}$  large), and small saturation voltage ( $V_G - V_{T0}$  small) to permit large-signal swing (Fig. 7).

The overall transconductance of the amplifier can be multiplied by ratio A of mirror  $T_4 - T_8$ , at the expense of a reduction in phase margin. Some of the mirrors can be avoided by using the folded cascode scheme [20].

Cascode transistors  $T_9$  and  $T_{10}$  decrease the output conductance by a factor equal to  $g_{ms}/g_o$ . This is obtained without any noise penalty, and with only a very small reduction of phase margin. The resulting dc gain is thus higher than that of a two-stage noncascode amplifier which requires internal compensation. Gain may be further boosted by using double or triple cascode [19], until it becomes limited by the direct conductance to ground due to impact ionization in the drain depletion layers.

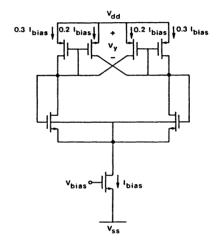

The reduction of maximum output swing due to the cascode transistors can be minimized by careful design of the bias circuitry  $T_{12} - T_{14} - T_{15} - T_{17}$  [13], [20]. Drain voltages of transistors  $T_7$  and  $T_8$  can be made equal to their limit value  $V_{D \text{ sat}}$  for saturation, independently of bias current. Maximum output swing is then only reduced by  $4V_{D \text{ sat}}$  with respect to total supply voltage, which only amounts to about 400 mV in weak inversion.

The circuit can be modified to provide differential output [20]. This doubles the maximum output swing, but requires a common mode feedback scheme.

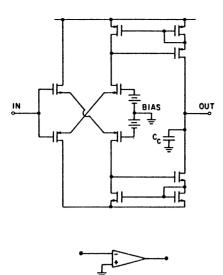

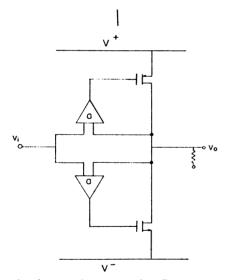

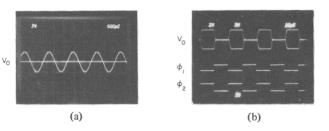

All amplifiers based on a differential input pair suffer noise and speed penalties with respect to a simple CMOS inverter used as an amplifier with an adequate biasing scheme [21]. This kind of amplifier is furthermore free from any slew rate limitation. It represents a very attractive solution for very low power [7] or very high speed [22] applications, in spite of its poor intrinsic PSRR.

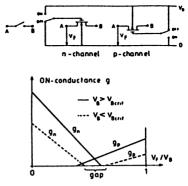

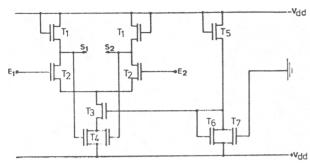

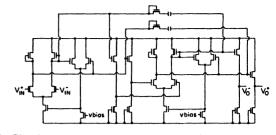

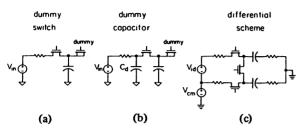

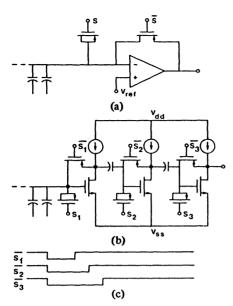

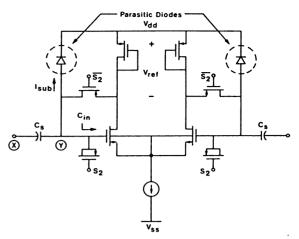

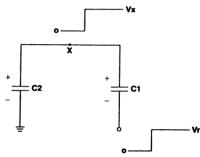

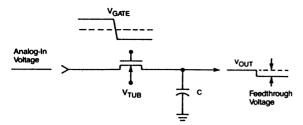

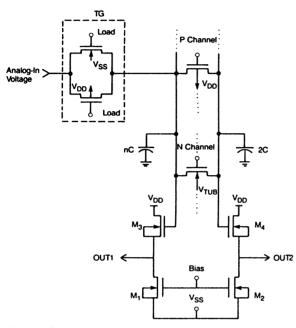

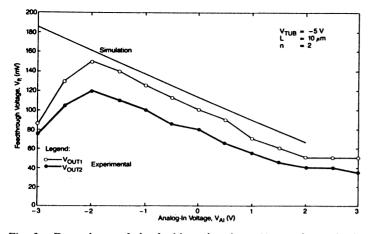

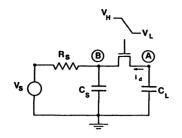

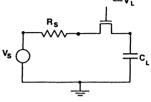

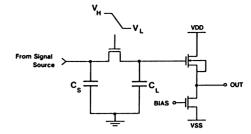

## C. Switch and Sample-and-Hold

The realization of the analog switch, which is a very important component of CMOS analog circuits, is illustrated in Fig. 8. A n-channel transistor is switched on by connecting its gate to the positive power line  $V_B$ . However, its on-conductance  $g_n$  comes to zero if potential  $V_F$  at which the device floats is too high. The same is true if  $V_F$  is too low for on-conductance  $g_p$  of the p-channel transistor

Fig. 8. Realization of an analog switch. On-conductances  $g_n$  and  $g_p$  of n-channel and p-channel transistors depend on floatation voltage  $V_{F}$ .

with gate connected to zero. If total supply voltage  $V_B$  is larger than a critical value  $V_{Bcrit}$ , the conductance of the switch can be ensured independently of  $V_F$  by connecting both types of transistors in parallel. Below this critical value, a gap of conduction appears at intermediate levels of  $V_F$ . Because of substrate effects, this critical supply voltage may widely exceed the sum  $V_{T0p} + V_{T0n}$  of p and n thresholds for zero source voltages. For example,  $V_{T0p} =$ 0.6 V and  $V_{T0n} = 0.7$  V may correspond to  $V_{Bcrit} = 2.3$  V [18], [23]. This very severe limitation to low-voltage operation of analog circuits may be circumvented by on-chip clock voltage multiplication [8], [24].

Leakage in the off state is due to residual channel current and to reverse currents of junctions. Care must be taken not to bootstrap the switch potential beyond that of the power supply lines, which would forward bias these junctions [25].

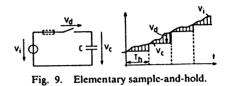

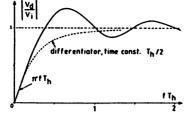

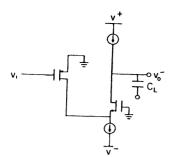

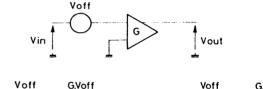

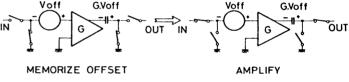

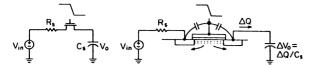

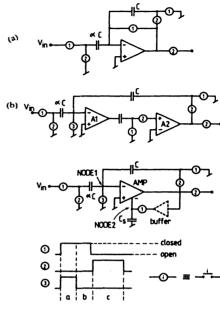

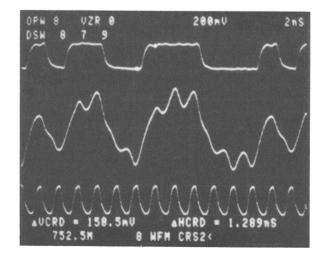

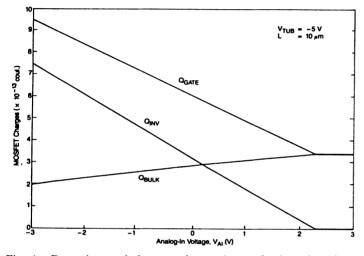

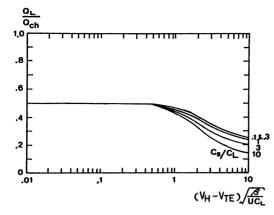

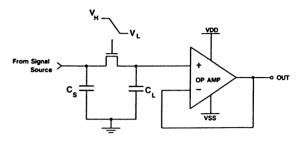

The combination of a switch and a capacitor provides a basic sample-and-hold shown in Fig. 9. Voltage  $V_{C}$  across capacitor C keeps a constant value equal to that of input voltage  $V_i$  at the last sampling instant. The value the of noise voltage at the sampling instant is also frozen in capacitor C; therefore, the total noise power is concentrated below the clock frequency. Voltage  $V_d$  across the switch is readjusted to zero each time the switch is closed, which corresponds to the transfer function for the fundamental signal (component of output signal  $V_{d}$  at the frequency of input signal  $V_i$ ) shown in Fig. 10 [26]. At low frequency, this autozeroing by means of a sample-and-hold amounts to a differentiation, with a time constant equal to half the value of hold duration  $T_{h}$ . It may be used to cancel offset and to reduce low-frequency noise components generated in a circuit [6], [27].

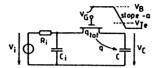

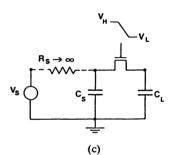

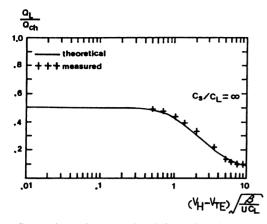

Another source of sampling error is caused by the charge which is released from the channel into holding capacitor Cwhen the transistor of the switch is blocked [28]. This problem has been analyzed in the general case shown in

Fig. 10. Differentiating property of autozeroing obtained by sampleand-hold.

Fig. 11. Equivalent circuit of a practical sample-and-hold. Finite fall time of gate voltage  $V_G$  allows redistribution of charge through the transistor.

Fig. 12. Calculated fraction q of total charge  $q_{1ot}$  left in holding capacitor C after switch-off [23].

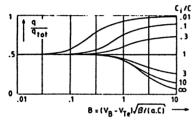

Fig. 11 where the source of the signal is assumed to have an internal capacitance  $C_i$  [23], [26]. Finite fall time of  $V_G$ (slope -a) from initial value  $V_B$  to effective threshold voltage  $V_{Te}$  allows a redistribution through the transistor of total charge  $q_{tot} = C_{gate} (V_B - V_{Te})$  between C and  $C_i$ . The result obtained by numerical integration of a normalized nonlinear equation describing this process, for time constant  $R_iC_i$  much larger than the switching time, is represented in Fig. 12. This figure shows the fraction q of total channel charge  $q_{tot}$  which goes into holding capacitor C for various values of ratio  $C_i/C$ . This fraction is a function of an intermediate parameter B which combines clock amplitude, clock slope,  $\beta$  of transistor, and value of holding capacitor C. These curves suggest various strategies for minimizing parasitic charge q.

A first possibility is to choose  $C_i$  very large and B much larger than 1. All charges released into C flow back into  $C_i$ during the decay of gate voltage, and q tends to zero (some easily calculable additional charge is due to the coupling through overlap capacitors after switching off). The drawback is the long period of time needed for switching off.

A second solution is to equilibrate the values of both capacitors [29]. By symmetry, half of the channel charge flows in each capacitor, and can be compensated by halfsized dummy switches that are switched on when the main switch is blocked [28].

The need for equal values of capacitors may be eliminated by choosing a value of B much smaller than 1 which also

Fig. 13. Stray insensitive SC integrators.

ensures equipartition of the total charge. Charge q is then compensated by a single dummy switch.

When complementary transistors are used to implement the switch, they partially compensate each other, although matching is very poor. The effect of charge injection can be drastically reduced by appropriate circuit techniques such as differential implementation [25], and active compensation by a low sensitivity auxiliary input [26], [30].

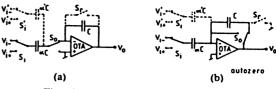

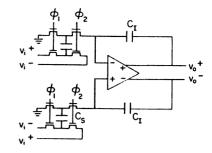

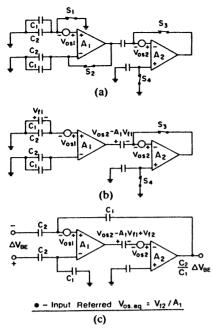

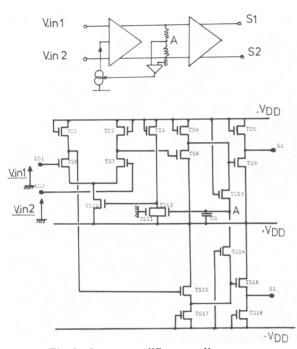

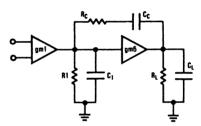

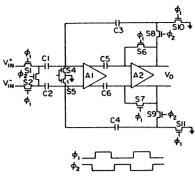

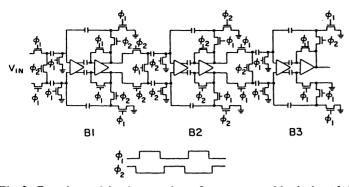

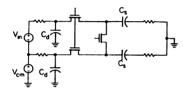

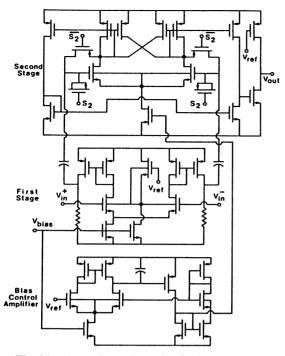

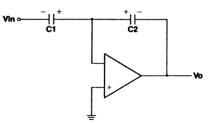

#### D. Switched Capacitor Integrators

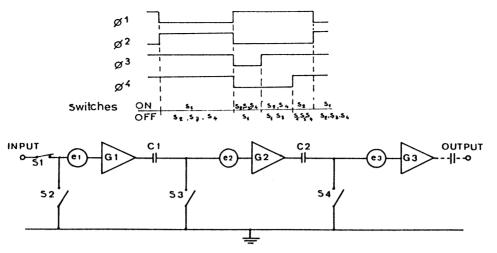

Switched capacitor integrators are the building blocks of all kinds of circuits, in particular SC filters. Two different implementations that are insensitive to parasitic capacitances to ground are shown in Fig. 13. Both provide a differential input and a time constant  $1/\alpha f_c$ , which only depends on clock frequency  $f_c$  and ratio of capacitors  $\alpha$ . Version b includes autozeroing, which reduces lowfrequency noise and compensates offset. It can therefore be realized with a nondifferential amplifier such as a CMOS inverter [7].

Output resetting can be obtained by additional switch  $S_r$ , and many differential signals can be separately weighted and summed by repeating the input circuitry, as shown in dotted lines. These integrators may be damped at will by connecting one of these additional inputs to output.

They can be transformed into amplifiers with controlled gain, either by resetting the output at every clock cycle, or by deleting integrating capacitor C in a damped configuration.

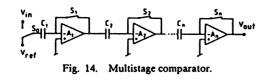

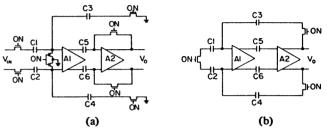

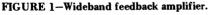

## E. Comparators

Comparators must usually achieve a very low value of input offset voltage. An excellent solution is obtained by removing integrating capacitor C in the basic integrator of Fig. 13b [31]. Any difference  $V_{i+} - V_{i-}$  will cause an output current to charge (or discharge) the parasitic output capacitance. The comparator thus behaves as an integrator of input error voltage, and sensitivity is proportional to the time alotted for comparison. It is ultimately limited by the finite dc gain of the amplifier. The speed-sensitivity ratio may be increased by achieving *n*th order integration along a cascade of *n* stages [26], as shown in Fig. 14.

The effects of charge injection and switching noise may be virtually cancelled by sequentially opening switches  $S_1$ to  $S_n$  before toggling switch  $S_0$ : When  $S_1$  is opened first, charge injection and sampled noise cause an error voltage across  $C_1$ . Since switch  $S_2$  is still closed, a compensation voltage appears across  $C_2$  after equilibration. The same is true when  $S_2$  to  $S_{n-1}$  are then opened sequentially. The

Fig. 16. Extraction of  $U_T = kT/q$  with MOS transistors  $T_1 - T_2$  operated in weak inversion.

only residual error at the input is thus that due to switch  $S_n$  divided by the gain of the n-1 first stages [32], [33]. Accuracy is further improved by using a fully differential implementation for which values of offset as low as 5  $\mu$ V have been reported [34].

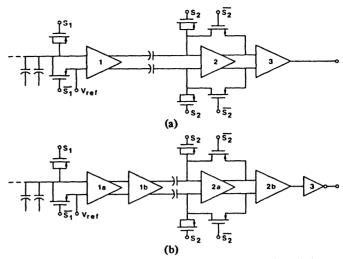

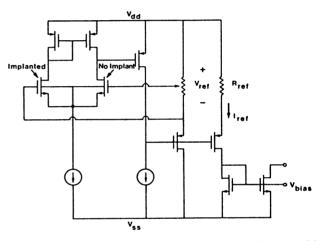

## F. Voltage and Current References

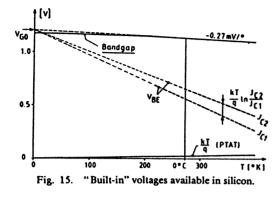

The realization of absolute references must be based on intrinsic physical values, in order to reduce their sensitivity to process variations.

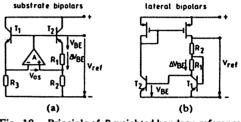

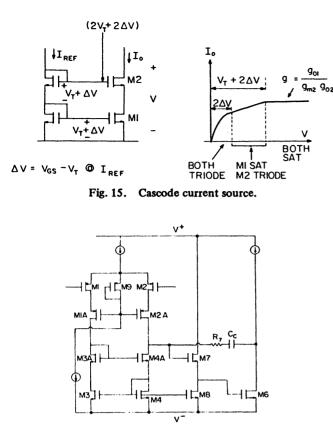

The various "built-in" voltages provided by silicon are represented in Fig. 15. They can be extracted by adequate circuits to implement voltage references.

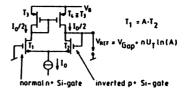

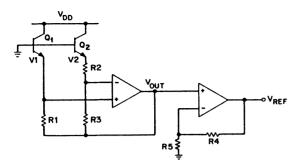

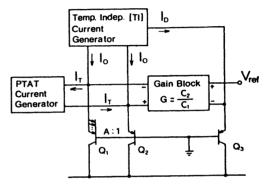

Thermal voltage  $U_T = kT/q$ , proportional to absolute temperature (PTAT), can be extracted by two MOS transistors operated in weak inversion with different current densities, as shown in Fig. 16 [3], [35]. If  $T_3 = T_4$ , application of weak inversion model (2) to transistors  $T_1$  and  $T_2 = AT_1$  yields

$$V_{\rm ref} = U_T \ln(A) \tag{9}$$

which in turn imposes current  $I_2$  in the circuit.

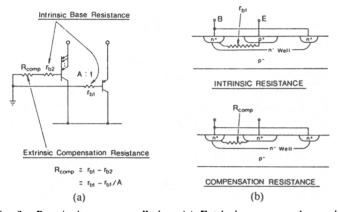

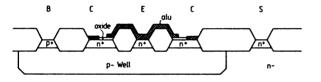

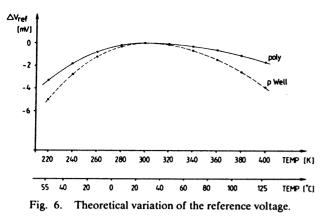

Bandgap voltage  $V_{gap}$  decreases approximately linearly with temperature from extrapolated value  $V_{G0}$ , with a slight curvature. A possible technique for direct extraction of  $V_{gap}$  is shown in Fig. 17 [36]. Transistor  $T_1$  is n-channel with a normal n<sup>+</sup>-doped silicon gate. Transistor  $T_2$  is also

Fig. 17. Extraction of bandgap voltage  $V_{gap}$  by MOS transistors [36].

Fig. 18. Principle of SC-weighted bandgap reference.

Fig. 19. Principle of R-weighted bandgap reference.

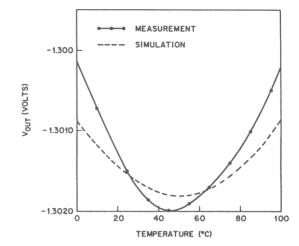

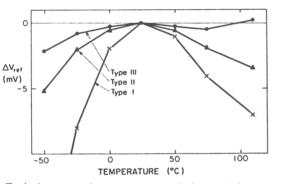

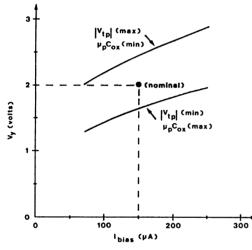

n-channel but with a p<sup>+</sup>-doped gate, as is possible in some technologies. Their threshold voltages therefore differ by approximately  $V_{gap}$  which appears at the output of this simple amplifier connected in unity gain configuration. After compensation by a small PTAT voltage obtained by operating  $T_1$  and  $T_2$  in weak inversion at different current densities, a temperature coefficient lower than 30 ppm °C can be obtained. All references based on MOS operation have their accuracy degraded by large uncontrolled offset components due to surface effects.

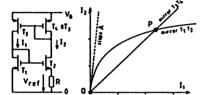

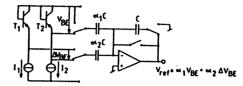

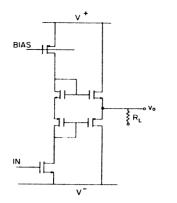

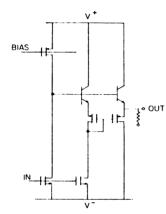

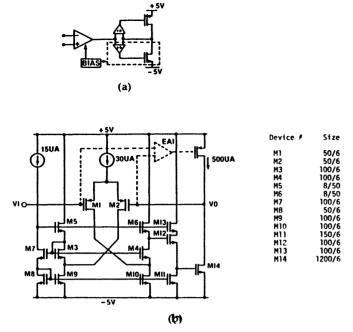

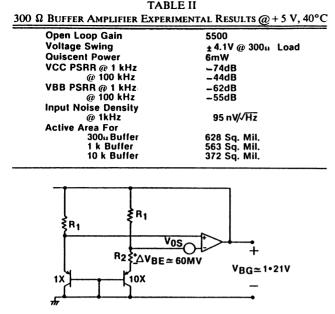

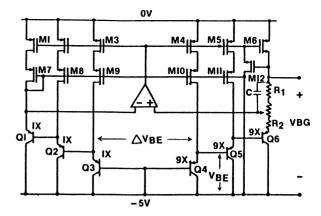

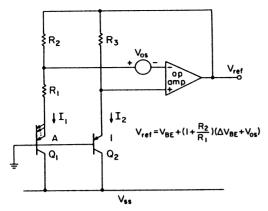

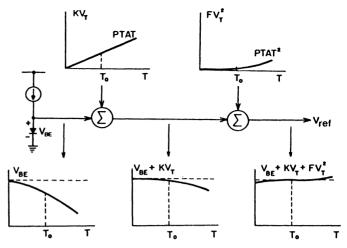

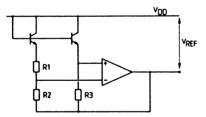

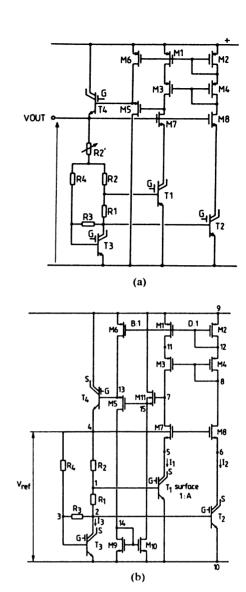

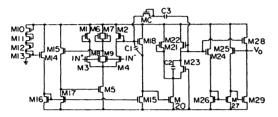

Base-emitter voltage  $V_{BE}$  of bipolar transistors is not really a physical parameter, but it only depends very slightly on the process. The difference  $\Delta V_{BE}$  of two bipolars operated at different current densities is strictly proportional to kT/q. After multiplication by an adequate factor, it can be added to  $V_{BE}$  to obtain a voltage of value  $V_{G0}$  independent of temperature. This principle of bandgap reference is well known in bipolar technology, and can be applied to the bipolars available in CMOS technology.

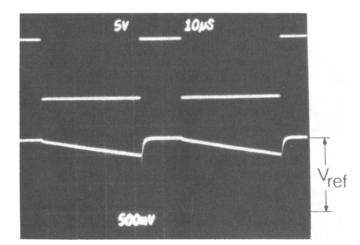

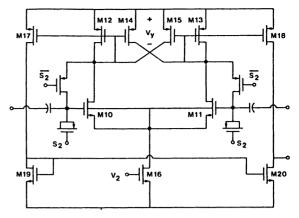

Weighting and summing  $V_{BE}$  and  $\Delta V_{BE}$  can be achieved by the SC circuit shown in Fig. 18, which is derived from the integrator of Fig. 13(b) [23], [37], [38]. Transistors  $T_1$ and  $T_2$  are bipolars to substrate. Accuracy is mainly limited by charge injection from the feedback switch.

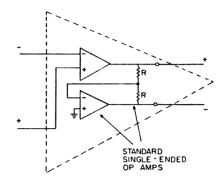

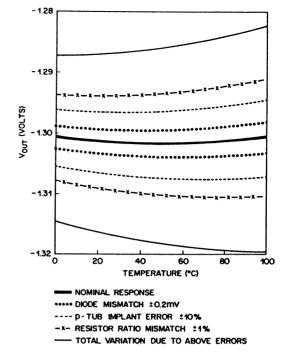

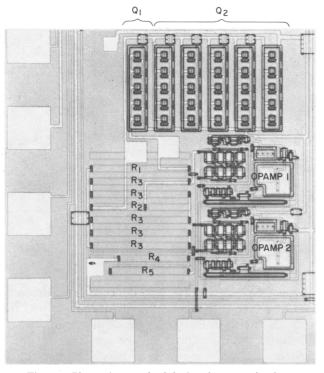

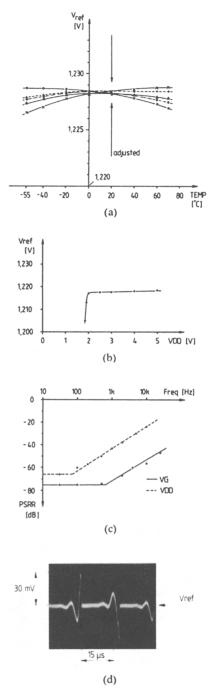

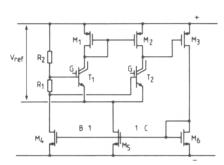

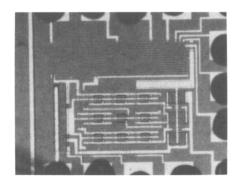

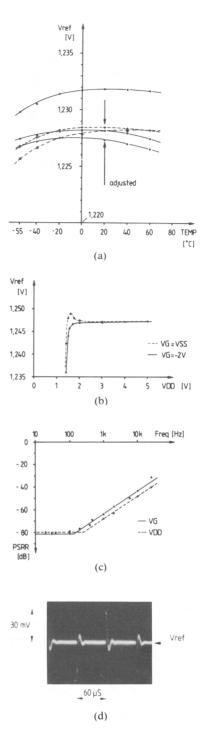

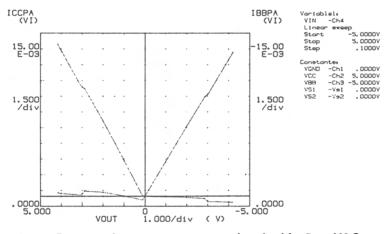

Another solution consists in using a resistive divider, as depicted in Fig. 19. Version *a* uses substrate bipolars and a CMOS amplifier [39]. The offset of this amplifier, which is multiplied by  $R_2/R_1$  of the order of 10, causes independent errors of the value of  $V_{ref}$  and of its temperature coefficient. Adjustment at two different temperatures would thus be required to achieve an accuracy of a few millivolts. Version *b* uses compatible lateral bipolars and avoids any MOS amplifier [4]. The error due to the p-channel mirror is

Fig. 20. SC voltage-to-current converter [40].

lowered by operating deeply in strong inversion. The offset of bipolars is small and only causes an error PTAT, which can be corrected at a single temperature.

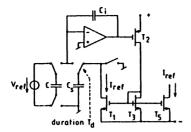

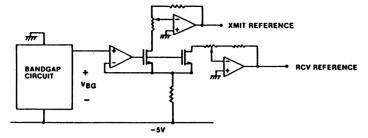

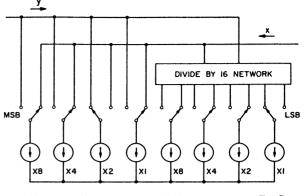

Semiconductor physics do not provide any "built-in" current. Current references must thus be derived from voltage references by applying Ohm's law in voltage to current converters. Poor absolute precision and temperature coefficient of available resistors result in errors of many tens of percent. A good solution based on a SC scheme that takes advantage of the better accuracy of available capacitors is shown in Fig. 20 [40]. It is a closed loop system which forces equilibrium, for every clock cycle, between charge  $CV_{ref}$  poured into storage capacitor  $C_s$  and charge  $I_{ref}T_d$  withdrawn from the same capacitor. Thus

$$I_{\rm ref} = CV_{\rm ref}/T_d.$$

(10)

Generation of an independent frequency on chip is not possible with a precision better than a few tens of percent. It is normally not required since an accurate clock frequency is usually provided by the system, from which synchronous signals of any frequency can be derived in a digital way. Totally asynchronous signals of accurate frequency can be produced by quasi-sinusoidal SC oscillators [41]-[43].

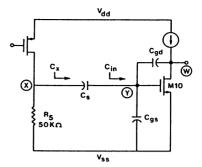

## IV. ANALOG CIRCUITS IN A DIGITAL ENVIRONMENT

If no precaution is taken, the dynamic range of analog circuits will be limited by the noise generated by digital circuits operating on the same chip. This problem is specially accute for sampled circuits which fold down highfrequency noise components by undersampling.

Coupling may occur through power lines, current in the common substrate, capacitive links, and possibly by minority carriers that are released when digital transistors are being blocked.

Various provisions can be suggested to improve the situation: Utilization of separate power lines, including pads, bondings, and possibly pins. Implementation of power supply filters or regulators. High value of PSRR, also at high frequencies for sampled circuits; care must be taken not to destroy the PSRR of amplifiers by the additional circuitry. Systematic implementation of fully differential structures. Avoidance of large current spikes in digital circuits, and of any digital transition during critical analog tasks. Provision of maximum distance on chip to digital lines, and of separate clean clocks for analog cir-

cuits. Critical nodes should be shielded from substrate and from digital lines by adequate layers, and analog circuits can be separated by special wells that collect parasitic minority carriers. Processes that provide an epitaxial layer on a highly doped substrate, to improve immunity to latch-up, allow to drain all parasitic currents to substrate.

#### V. CONCLUSION

Thanks to the versatility of the CMOS technology, all kinds of analog circuits can be combined on the same chip with digital circuits, without any process modification. However, additional parameters need to be specified and guaranteed, the number of which depends on the type of function and on design cleverness.

A standard MOS transistor can be operated in various modes which have their respective merits. Weak inversion provides maximum values of gain and signal swing, and minimum offset and noise voltages. Strong inversion is required to achieve high speed, and provides minimum relative values of offset and noise currents. The lateral bipolar mode exhibits excellent matching properties and very low 1/f noise, and can be used to implement a variety of schemes previously developed for normal bipolars transistors.

Mismatch of active and passive devices represents a major limitation to the accuracy of analog circuits. It can be minimized by respecting a set of basic rules. Designs must be based on sound concepts that take maximum advantage of all available components.

Single-stage cascoded OTA's should be preferred to multistage amplifiers. Their optimization amounts to choosing the best possible compromise with respect to various conflicting requirements. The excellent performance of the MOS transistor as a switch and the availability of highquality capacitors are key elements in the implementation of a variety of analog functions. The elementary sampleand-hold that is made possible by the absence of any dc gate control current can be used to reduce low-frequency noise and to compensate offset. Its major limitation is due to charge injection from the switch, which can be evaluated and partially compensated by an adequate strategy.

Accurate absolute references are very critical circuits which must be based on intrinsic physical values to achieve low sensitivity to process. This is possible for voltage references, from which current references can be derived by applying Ohm's law.

Precautions must be taken to avoid degradation of analog performances by the noise generated by the digital part of the chip.

#### References

- R. W. Brodersen and P. R. Gray, "The role of analog circuits in future VLSI technologies," in ESSCIRC '83 Dig. Tech. Papers, Sept. 1983, pp. 105-110. J. D. Chatelain, "Dispositifs à semiconducteurs," Traité d'Electri-cité EPFL, vol. VII (Georgi, St-Saphorin, Switzerland), 1979. [1]

- [2]

- [3] E. Vittoz and J. Fellrath, "CMOS analog integrated circuits based on weak inversion operation," *IEEE J. Solid-State Circuits*, vol. SC-12, pp. 224-231, June 1977.

[4] E. Vittoz, "MOS transistors operated in the lateral bipolar mode and their applications in CMOS technology," *IEEE J. Solid-State Circuits*, vol. 270, June 1977.

- Circuits, vol. SC-18, pp. 273-279, June 83. J. Fellrath and E. Vittoz, "Small signal model of MOS transistors in weak inversion," in *Proc. Journées d'Electronique* 1977 (EPF-Lausanne), pp. 315-324. [5]

- Lausanne), pp. 313-324.

H. W. Klein and W. Engl, "Design techniques for low noise CMOS operational amplifiers," in ESSCIRC '84 Dig. Tech. Papers (Edinburgh), Sept. 1984, pp. 27-30.

F. Krummenacher, "Micropower switched capacitor biquadratic cell," IEEE J. Solid-State Circuits, vol. SC-17, pp. 507-512, June 1992.

- [7] 1982.

- M. Degrauwe and F. Salchli, "A multipurpose micropower SC-filter," *IEEE J. Solid-State Circuits*, vol. SC-19, pp. 343-348, June [8] 1984

- E. Vittoz and F. Krummenacher, "Micropower SC filters in Si-gate technology," in Proc. ECCTD '80 (Warshaw), Sept. 1980, pp. (9) 61-72

- J. L. McCreary, "Matching properties, and voltage and temperature dependence of MOS capacitors," *IEEE J. Solid-State Circuits*, vol. SC-16, pp. 608-616, Dec. 1981. Y. Uchida *et al.*, "A low power resistive load 64 kbit CMOS RAM," *IEEE J. Solid-State Circuits*, vol. SC-17, pp. 804-909, Oct. [10]

- [11] 1982

- RAM," IEEE J. Solid-State Circuits, vol. SC-17, pp. 804-909, Oct. 1982.

[12] M. Dutoit and F. Sollberger, "Lateral polysilicon p-n diodes," J. Electrochem. Soc., vol. 125, pp. 1648-1651, Oct. 1978.

[13] F. Krummenacher, "High voltage gain CMOS OTA for micropower SC filters," Electron. Lett., vol. 17, pp. 160-162, 1981.

[14] S. Gustafsson et al., "Low-noise operational amplifiers using bipolar input transistors in a standard metal gate CMOS process," Electron. Lett., vol. 20, pp. 563-564, 1984.

[15] B. J. Hosticka, "Dynamic CMOS amplifiers," IEEE J. Solid-State Circuits, vol. SC-15, pp. 887-894, Oct. 1980.

[16] M. G. Degrauwe et al., "Adaptive biasing CMOS amplifiers," IEEE J. Solid-State Circuits, vol. SC-17, pp. 522-528, June 1982.

[17] E. Seevinck and R. F. Wassenaar, "Universal adaptive biasing principle for micropower amplifiers," in ESSCIRC '84 Dig. Tech. Papers (Edinburgh), Sept. 1984, pp. 59-62.

[18] E. Vittoz, "Micropower techniques," Advanced Summer Course on Design of MOS-VLSI Circuits for Telecommunications, L'Aquila, Italy, June 1984, to be published by Prentice-Hall, 1985.

[19] P. W. Li et al., "A ratio-independent algorithmic ADC technique," in ISSCC Dig. Tech. Papers, Feb. 1984, pp. 62-63.

[20] T. C. Choi et al., "High-frequency CMOS switched-capacitor filters for communications application," IEEE J. Solid-State Circuits, vol. SC-18, pp. 652-664, Dec. 1983.

[21] F. Krummenacher, E. Vittoz, and M. Degrauwe, "Class AB CMOS amplifiers for micropower SC filters," Electron. Lett., vol. 17, pp. 433-435, June 1981.

[22] S. Masuda et al., "CMOS sampled differential push-pull cascode

- 433-435, June 1981.

- [22] S. Masuda et al., "CMOS sampled differential push-pull cascode operational amplifier," in Proc. ISCAS '84 (Montreal, Ont., Canada), May 1984, p. 1211.

- [23] E. Vittoz, "Microwatt SC circuit design," "Summer course on SC

circuits," KU-Leuven, Belgium, June 1981, republished in Electro-

- [24] F. Krummenacher, H. Pinier, and A. Guillaume, "Higher sampling rates in SC circuits by on-chip clock-voltage multiplication," in ESSCIRC '83 Dig. Tech. Papers (Lausanne), pp. 123–126, Sept. 1983.

- D. J. Alstott, "A precision variable-supply CMOS comparator," IEEE J. Solid-State Circuits, vol. SC-17, pp. 1080-1087, Dec. 1982. E. Vittoz, "Dynamic analog techniques," Advanced Summer Course [25]

- [26] E. Villoz, "Dynamic analog techniques," Advanced Summer Course on Design of MOS-VLSI Circuits for Telecommunications, L'Aquila, Italy, June 1984, to be published by Prentice-Hall, 1985.

C. Enz, "Analysis of the low-frequency noise reduction by autozero technique," Electron. Lett., vol. 20, pp. 959-960, Nov. 1984.

E. Suarez et al., "All-MOS charge redistribution analog-to digital conversion techniques," IEEE J. Solid-State Circuits, vol. SC-10, pp. 379-385, Dec. 1975

- [27]

- [28] pp. 379-385, Dec. 1975.

- L. Bienstman and H. J. De Man, "An eight-channel 8-bit micro-[29]

- [29] L. Bienstman and H. J. De Man, "An eight-channel 8-bit microprocessor compatible NMOS converter with programmable scaling," *IEEE J. Solid-State Circuits*, vol. SC-15, pp. 1051-1059, Dec. 1980.

[30] M. G. Degrauwe, E. Vittoz, and I. Verbauwhede, "A micropower CMOS instrumentation amplifier," in *ESSCIRC '84 Dig. Tech. Papers* (Edinburgh), Sept. 1984, pp. 31-34.

[31] Y. S. Lee et al., "A 1 mV MOS comparator," *IEEE J. Solid-State Circuits*, vol. SC-13, pp. 294-297, June 1978.

[32] R. Poujois et al., "Low-level MOS transistor amplifier using storage techniques," in *ISSCC Dig. Tech. Papers*, 1973, pp. 152-153.

[33] A. R. Hamade, "A single chip all-MOS 8-bit ADC," *IEEE J. Solid-State Circuits*, vol. SC-14, pp. 785-791, Dec. 1978.

[34] R. Poujois and J. Borel, "A low drift fully integrated MOSFET operational amplifier," *IEEE J. Solid-State Circuits*, vol. SC-13, pp. 499-503, Aug. 1978.

- 499-503, Aug. 1978.

[35] E. Vittoz and O. Neyroud, "A low-voltage CMOS bandgap reference," *IEEE J. Solid-State Circuits*, vol. SC-14, pp. 573-577, June 1979

- [36] H. Oguey and B. Gerber, "MOS voltage reference based on polysilicon gate work function difference," *IEEE J. Solid-State Circuits*, vol. SC-15, pp. 264-269, June 1980.

[37] O. Leuthold, "Integrierte Spannungsüberwachungsschaltung," pre-structure of the second secon

- [37] O. Leuthold, "Integrierte Spannungsüberwachungsschaltung," presented at Meet. Swiss Chapter Solid-State Devices Circuits (Bern, Switzerland), Oct. 1981.

[38] B. S. Song and P. R. Gray, "A precision curvature-compensated CMOS bandgap reference," *IEEE J. Solid-State Circuits*, vol. SC-18, pp. 634-643, Dec. 1983.

[39] R. Ye and Y. Tsividis, "Bandgap voltage reference sources in CMOS technology," *Electron. Lett.*, vol. 18, pp. 24-25, 1982.

[40] H. W. Klein and W. L. Engl, "A voltage-current-converter based on a SC-controller," in *ESSCIRC '83 Dig. Tech. Papers*, (Lausanne, Switzerland). Sent. 1983. pp. 119-122.

- [41]

- on a SC-controller," in ESSCIRC '83 Dig. Tech. Papers, (Lausanne, Switzerland), Sept. 1983, pp. 119-122.

E. Vittoz, "Micropower SC oscillator," IEE/E J. Solid-State Circuits, vol. SC-14, pp. 622-624, June 1979.

B. J. Hosticka et al., "Switched-capacitor FSK modulator and demodulator in CMOS technology," in ESSCIRC '83 Dig. Tech. Papers, pp. 231-216 (Lausanne, Switzerland), Sept. 1983.

F. Krummenacher, "A high resolution capacitance-to-frequency converter," in ESSCIRC '84 Dig. Tech. Papers (Edinburgh), Sept. 1984. [42]

- [43] 1984, pp. 95-98.

## MOS Operational Amplifier Design— A Tutorial Overview

PAUL R. GRAY, FELLOW, IEEE, AND ROBERT G. MEYER, FELLOW, IEEE

## (Invited Paper)

Abstract-This paper presents an overview of current design techniques for operational amplifiers implemented in CMOS and NMOS technology at a tutorial level. Primary emphasis is placed on CMOS amplifiers because of their more widespread use. Factors affecting voltage gain, input noise, offsets, common mode and power supply rejection, power dissipation, and transient response are considered for the traditional bipolar-derived two-stage architecture. Alternative circuit approaches for optimization of particular performance aspects are summarized, and examples are given.

## I. INTRODUCTION

THE rapid increase in chip complexity which has occurred over the past few years has created the need to implement complete analog-digital subsystems on the same integrated circuit using the same technology. For this reason, implementation of analog functions in MOS technology has become increasingly important, and great strides have been made in recent years in implementing functions such as high-speed DAC's, sampled data analog filters, voltage references, instrumentation amplifiers, and so forth in CMOS and NMOS technology [1]. These developments have been well documented in the literature. Another key technical development has been a maturing of the state of the art in the implementation of operational amplifiers (op amps) in MOS technology. These amplifiers are key elements of most analog subsystems, particularly in switched capacitor filters, and the performance of many systems is strongly influenced by op amp performance. Many of the developments in MOS operational amplifier design have not been as well documented in the literature, and the intent of this paper is to review the state of the art in this field. This paper is focused on the design of op amps for use within single-chip analog-digital LSI systems, and the particular problems of the design of stand-alone CMOS amplifiers are not addressed.

The authors are with the Department of Electrical Engineering and Computer Sciences and the Electronics Research Laboratory, University of California, Berkeley, CA 94720. In Section II, the important performance requirements and objectives for operational amplifiers within a monolithic analog subsystem are summarized. In Section III, the performance of the basic two-stage CMOS operational amplifier architecture is summarized. In Section IV, alternative circuit approaches for the improvement of particular performance aspects are considered. In Section V, the particular problems associated with NMOS depletion load amplifier design are considered, and in Section VI, the design of output stages is considered. Finally, a summary and discussion of the design of amplifiers in scaled technologies are presented in Section VII.

## II. PERFORMANCE OBJECTIVES FOR MOS OPERATIONAL AMPLIFIERS

The performance objectives for operational amplifiers to be used within a monolithic analog subsystem are often quite different from those of traditional stand-alone bipolar amplifiers. Perhaps the most important difference is the fact that for many of the amplifiers in the system, the load which the output of the amplifier has to drive is well defined, and is often purely capacitive with values of a few picofarads. In contrast, stand-alone general-purpose amplifiers usually must be designed to achieve a certain level of performance independent of loading over capacitive loads up to several hundred picofarads and resistive loads down to 2 k $\Omega$  or less. Within a monolithic analog subsystem, only a few of the amplifiers must drive a signal off chip where the capacitive and resistive loads are significant and variable. In this paper, these amplifiers will be termed output buffers, and the amplifiers whose outputs do not go off chip will be termed internal amplifiers. The particular problems of the design of these output buffers are considered in Section VII.

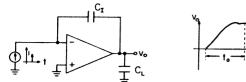

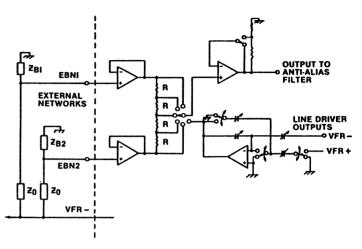

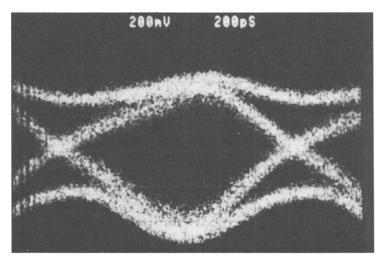

A typical application of an internal operational amplifier, a switched capacitor integrator, is illustrated in Fig. 1. The basic function of the op amp is to produce an updated value of the output in response to a switching event at the input in which the sampling capacitor is charged from the source and discharged into the summing node. The output must assume the new updated value within the required accuracy, typically on the order of 0.1 percent, within one clock period, typically on the order of 1  $\mu$ s for voiceband filters. Important performance

Reprinted from IEEE J. Solid-State Circuits, vol. SC-17, no. 6, pp. 969-982, Dec. 1982.

Manuscript received August 24, 1982; revised September 27, 1982. This work was supported by the Joint Services Electronics Program under Contract F49620-79-c-0178 and the National Science Foundation under Grant ENG79-07055.

Fig. 1. Typical application of an internal MOS operational amplifier, a switched capacitor integrator.

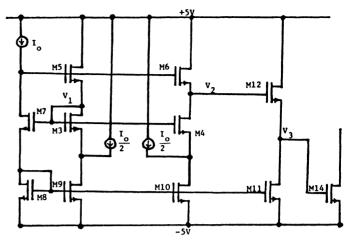

TABLE I TYPICAL PERFORMANCE, CONVENTIONAL TWO-STAGE CMOS INTERNAL OPERATIONAL AMPLIFIER (+/-5 V SUPPLY, 4 µm SI GATE CMOS)

| dc gain (capacitive load only)               | 5000                    |  |  |

|----------------------------------------------|-------------------------|--|--|

| Setting time, 1 V step, $C_l = 5 \text{ pF}$ | 500 ns                  |  |  |

| Equiv. input noise, 1 kHz                    | 100 nV/ <del>//Hz</del> |  |  |

| PSRR, dc                                     | 90 dB                   |  |  |

| PSRR, 1 kHz                                  | 60 dB                   |  |  |

| PSRR, 50 kHz                                 | 40 dB                   |  |  |

| Supply capacitance                           | 1 fF                    |  |  |

| Power dissipation                            | 0.5 mW                  |  |  |

| Unity-gain frequency                         | 4 MHz                   |  |  |

| Die area                                     | 75 mils <sup>2</sup>    |  |  |

| Systematic offset                            | 0.1 mV                  |  |  |

| Random offset std. deviation                 | 2 mV                    |  |  |

| CMRR                                         | 80 dB                   |  |  |

| CM range                                     | within 1 V of supply    |  |  |

parameters are the power dissipation, maximum allowable capacitive load, open-loop voltage gain, output voltage swing, equivalent input flicker noise, equivalent input thermal noise, power supply rejection ratio, supply capacitance (to be defined later), and die area. In this particular application the input offset voltage, common-mode rejection ratio, and commonmode range are less important, but these parameters can be important in other applications. Because of the inherent capacitive sample/hold capability in MOS technology, dc offsets can often be eliminated at the subsystem level, making operational amplifier offsets less important. A typical set of values for the parameters given above for a conventional amplifier design in 4  $\mu$ m CMOS technology are given in Table I. In the following section, the factors affecting the various performance parameters are evaluated for the most widely used amplifier architecture.

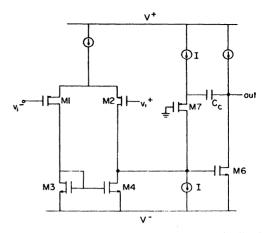

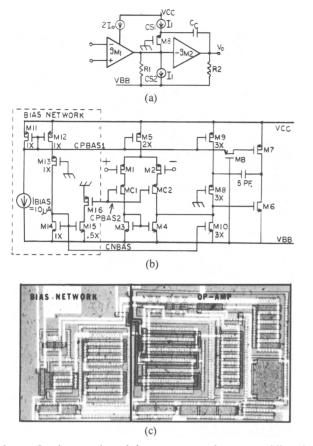

## III. BASIC TWO-STAGE CMOS OPERATIONAL AMPLIFIER

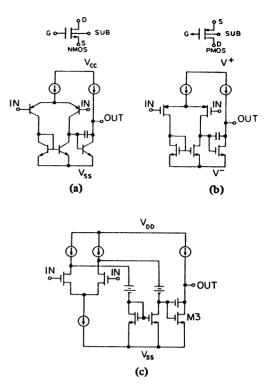

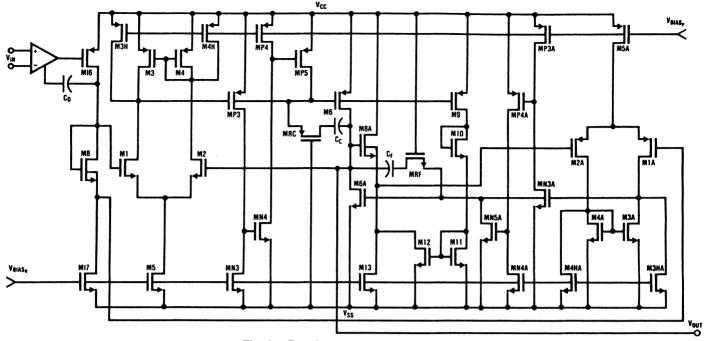

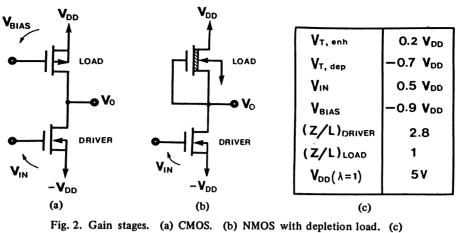

Currently, the most widely used circuit approach for the implementation of MOS operational amplifiers is the two-stage configuration shown in Fig. 2(b). This configuration is also widely used in bipolar technology, and the bipolar counterpart is also illustrated in Fig. 2(a). The behavior of this circuit when implemented in bipolar technology has been reviewed in an overview article published earlier [2]. This circuit configuration provides good common mode range, output swing, voltage gain, and CMRR in a simple circuit that can be compensated with a single pole-splitting capacitor. While the implementation of this architecture in NMOS technology requires additional circuit elements because of the lack of a complementary device, many NMOS amplifiers commercially manufactured at the present time use a conceptually similar

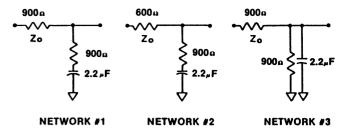

Fig. 2. Two-stage operational amplifier architecture. (a) Bipolar implementation. (b) CMOS implementation. (c) An example of an NMOS implementation with interstage coupling network.

configuration, as illustrated in Fig. 2(c) where a differential interstage level-shifting network composed of voltage and current sources has been inserted between the first and second stages so that both stages can utilize n-channel active devices and depletion mode devices as loads. The implementation of this circuit is discussed further in Section V.

In this section, we will analyze the various performance parameters of the CMOS implementation of this circuit, focusing particularly on the aspects which are different from the bipolar case.

## **Open Circuit Voltage Gain**

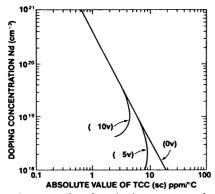

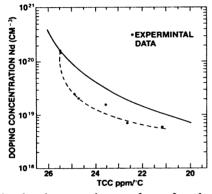

An important difference between MOS and bipolar technology is the fact that the maximum transistor open circuit voltage gain  $g_m/g_o$  is much lower for MOS transistors than for bipolar transistors, typically by a factor on the order of 10-40 for typically used geometries and bias currents [3]. Under certain simplifying assumptions, voltage gain can be shown to be

$$g_m/g_o = \frac{2L}{V_{gs} - V_T} \left(\frac{dx_d}{dV_{ds}}\right)^{-1}$$

(1)

where  $x_d$  is the width of the depletion region between the end of the channel and the drain and L is the effective channel length. The expression illustrates several key aspects of MOS devices used as analog amplifiers. First, for constant drain current decreasing either the channel length or width results in a decrease in the gain, the latter because of the fact that  $V_{gs}$  increases. This fact, along with noise considerations, usually dictates the minimum size of the transistors that must be used in a given high-gain amplifier application. Usually, this is

SCALE DEPENDS ON Z,L

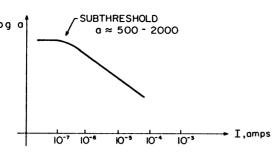

Fig. 3. Typical open circuit gain of an MOS transistor as a function of bias current.

Fig. 4. Schematic of basic two-stage CMOS operational amplifier.

larger than the length and width used for digital circuits in the same technology.

Second, if the device geometry is kept constant, the voltage gain is inversely proportional to the square root of the drain current since  $(V_{gs} - V_T)$  is proportional to the square root of the drain current. A typical variation of open circuit voltage gain as a function of drain current is shown in Fig. 3 [4]. The gain becomes constant at a value comparable to bipolar devices in the subthreshold range of current. This fact makes use of low current levels desirable, and at the same time complicates the design of high-speed amplifiers which must operate at high current.

Third, if device size and bias current are kept constant, the gain is an increasing function of substrate doping since  $dx_d/dV_{ds}$  decreases with increasing doping. Thus, devices which have received a channel implant to increase threshold voltage would display a higher open circuit gain than an unimplanted device whose channel doping was lower. Finally, the expression demonstrates that open circuit gain is not degraded by technology scaling in the constant field sense since all terms in the expression decrease in proportion. However, scaling in the quasi-constant field or constant voltage sense would result in a decrease in gain.

Turning to the operational amplifier, the voltage gain of the first stage of the circuit shown in Fig. 4 can be shown to be simply

$$A_{v1} = \frac{g_{m1}}{g_{o2} + g_{o4}} \tag{2}$$

where  $g_m$  is the device transconductance and  $g_o$  is the small signal output conductance, and assuming that M1 and M2 are

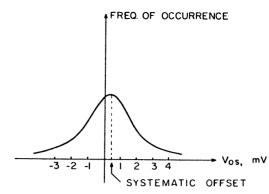

Fig. 5. Typical input offset distribution, MOS operational amplifier.

identical and that M3 and M4 are identical. Similarly, the second stage voltage gain is

$$A_{v2} = \frac{g_{m6}}{g_{06} + g_{07}}.$$

(3)

For switched capacitor filter applications, the overall voltage gain required is on the order of several thousand [5], implying a gain in each stage on the order of 50. In order to achieve this level of gain per stage, transistor bias currents and channel lengths and widths are usually chosen such that the transistor  $(V_{gs} - V_T)$  is several hundred millivolts, and the drain depletion region is on the order of one fifth or less of the effective channel length at the typical drain bias of several volts. Circuit approaches to achieving more voltage gain or, alternatively, achieving the same voltage gain with smaller devices, are discussed in Section IV.

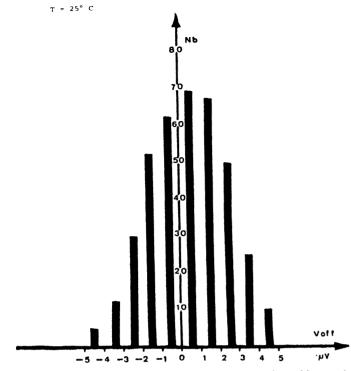

## DC Offsets, DC Biasing, and DC Power Supply Rejection

The input offset voltage of an operational amplifier is composed of two components, the systematic offset and the random offset. The former results from the design of the circuit and is present even when all of the matched devices in the circuit are indeed identical. The latter results from mismatches in supposedly identical pairs of devices. A typical observed distribution of input offset voltages is shown in Fig. 5.

## Systematic Offset Voltage

In bipolar technology, the comparatively high voltage gain per stage (on the order of 500) tends to result in a situation in which the input-referred dc offset voltage of an operational amplifier is primarily dependent on the design of the first stage. In MOS op amps, because of the relatively low gain per stage, the offset voltage of the differential to single-ended converter and second stage can play an important role. In Fig. 6, the operational amplifier of Fig. 4 has been split into two separate stages. Assuming perfectly matched devices, if the inputs of the first stage are grounded, then the quiescent output voltage at the drain of M4 is equal to the voltage at the drain of M3 (M3 and M4 have the same drain current and gate-source voltage, and hence must have the same drain-source voltage). However, the value of the gate voltage of M6 which is required to force the amplifier output voltage to zero may be different from the quiescent output voltage of the first stage. For a first stage gain of 50, for example, each 50 mV difference in these

Fig. 6. Two-stage amplifier illustrating interstage coupling constraints.

voltages results in 1 mV of input-referred systematic offset. Thus, the W/L ratios of M3, M4, and M6 must be chosen so that the current density in these three devices are equal. For the simple circuit of Fig. 6, this constraint would take the form

$$\frac{(W/L)_3}{(W/L)_6} = \frac{(W/L)_4}{(W/L)_6} = \left(\frac{1}{2}\right) \frac{(W/L)_5}{(W/L)_7} \,. \tag{4}$$

In order that this ratio be maintained over process-induced variations in channel length, the channel lengths of M3, M4, and M6 usually must be chosen to be the same, and the ratios provided by properly choosing the channel widths. The use of identical channel lengths for the devices is at odds with the requirements (discussed later) that for low noise, M3 and M4 have low transconductance, and that for best frequency response under capacitive loading, M6 has high transconductance.

Systematic offset voltage is closely correlated with dc power supply rejection ratio. If a systematic offset exists, it is likely to display a dependence on power supply voltage, particularly if the bias reference source is such that the bias currents in the amplifier are not supply independent.

## Random Input Offset Voltage

Source-coupled pairs of MOS transistors inherently display somewhat higher input offset voltage than bipolar pairs for the same level of geometric mismatch or process gradient. The reason for this is perhaps best understood intuitively by means of the conceptual circuit shown in Fig. 7. Here, a differential amplifier is made up of an identical pair of unilateral active devices biased at a current I and displaying a transconductance  $g_m$ . If the load elements, in this case assumed to be resistors, are assumed to mismatch by a percentage  $\Delta$ , then in order for the output voltage of the differential amplifier to be zero, the absolute difference in the currents in the two devices must be equal to  $\Delta I$ . This in turn requires that the dc input difference voltage applied to bring about this difference be

$$V_{gs} = \frac{I}{g_m} \Delta.$$

(5)

Thus, the input offset in this case depends on the  $I/g_m$  ratio of the active devices and the fractional mismatch in the

Fig. 7. Conceptual circuit for calculation of random offset voltage.

matched elements. A similar dependence is found for mismatches in many of the parameters of the active devices themselves, such as area mismatches in bipolar transistors and channel length and width mismatches in MOS transistors.

For bipolar devices, the  $I/g_m$  ratio is equal to kT/q or 0.026 V at room temperature. For MOS transistors, the ratio is  $(V_{gs} - V_T)/2$ , a bias-dependent quantity which is normally in the 100-500 mV range. While the offset voltage can be substantially improved by operating at low values of  $V_{gs}$ , the result is typically a somewhat larger offset voltage than in the bipolar case [2]. As discussed in a later section, the  $I/g_m$  ratio also directly effects the slew rate for class A input stages, so that often transient performance requirements place a lower limit on the allowable value of this parameter.

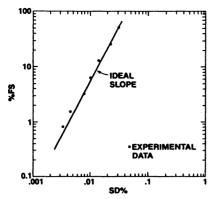

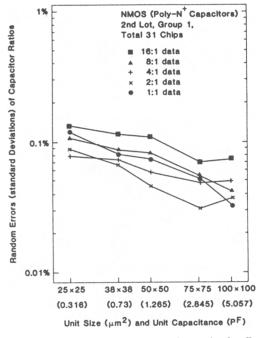

One mismatch component present in MOS devices which is not present in bipolar transistors is the mismatch in the threshold voltage itself. This component does not obey the above relationship, and results in a constant offset component which is bias current independent. Threshold mismatch is a strong function of process cleanliness and uniformity, and can be substantially improved by the use of common centroid geometries. Published data indicate that large-geometry commoncentroid structures are capable of achieving threshold match distributions with standard deviations on the order of 2 mV in a silicon gate MOS process of current vintage [6].

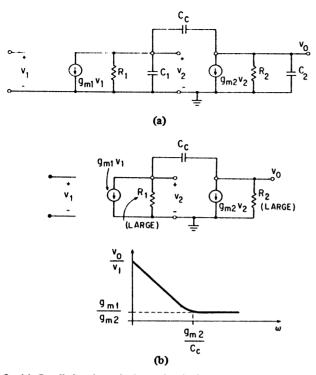

## Frequency Response, Compensation, Slew Rate, and Power Dissipation

The compensation of the two-stage CMOS amplifier can be carried out much as in the case of its bipolar equivalent using a pole-splitting capacitor  $C_c$  as shown in Fig. 2. However, important differences arise because of the much lower transconductance of the MOS transistor relative to bipolar devices [7]. The circuit can be approximately represented by the small-signal equivalent circuit of Fig. 8(a) if the nondominant poles due to the capacitances at the source of M1-2, the capacitance at the gate of M3, and any other nondominant poles which may exist on the circuit are neglected. This circuit has been analyzed by many authors [2], [8] because it occurs so fre-

Fig. 8. (a) Small-signal equivalent circuit for two-stage amplifier. (b) Small-signal equivalent circuit with  $C_1$  and  $C_2$  set to zero, and gain of the circuit versus frequency.

quently in bipolar amplifiers. The circuit displays two poles and a right half-plane zero, which under the assumption that the poles are widely spaced, can be shown to be approximately located at

$$p_1 = \frac{-1}{(1 + g_{m_2}R_2)C_cR_1} \tag{6}$$

$$p_2 = \frac{-g_{m_2}C_c}{C_2C_1 + C_2C_c + C_cC_1} \tag{7}$$

$$z = + \frac{g_{m2}}{C_c} \,. \tag{8}$$

Note that the pole due to the capacitive loading of the first stage by the second,  $p_1$ , has been pushed down to a very low frequency by the Miller effect in the second stage, while the pole due to the capacitance at the output node of the second stage,  $p_2$ , has been pushed to a very high frequency due to the shunt feedback. For this reason, the compensation technique is called pole splitting.

A unique problem arises when attempting to use pole splitting in MOS amplifiers. Analytically, the problem is illustrated by considering the location of the second pole  $p_2$  and the right half-plane zero z relative to the unity-gain frequency  $g_{m_1}/C_c$ . Here we make the simplifying assumption that the internal parasitic  $C_1$  is much smaller than either the compensation capacitor  $C_c$  or the load capacitance  $C_2$ . This gives

$$\left|\frac{p_2}{\omega_1}\right| = \frac{g_{m2}C_c}{g_{m1}C_2} \tag{9}$$

$$\left|\frac{2}{\omega_1}\right| = \frac{g_{m2}}{g_{m1}}.$$

(10)

Note that the location of the right half-plane zero relative to

the unity-gain frequency is dependent on the ratio of the transconductances of the two stages.

Physically, the zero arises because the compensation capacitor provides a path for the signal to propagate directly through the circuit to the output at high frequencies. Since there is no inversion in that signal path as there is in the inverting path dominant at low frequencies, stability is degraded. The location of the zero can best be conceptually understood by considering a case in which  $C_1$  and  $C_2$  are zero as illustrated in Fig. 8(b). For low frequencies, this circuit behaves like an integrator, but at high frequencies, the compensation capacitor behaves like a short circuit. When this occurs, the second stage behaves like a diode-connected transistor, presenting a load to the first stage equal to  $1/g_{m2}$ . Thus, the circuit displays a gain at high frequencies which is simply  $g_{m1}/g_{m2}$ , as illustrated in Fig. 8(b). The polarity of this gain is opposite to that at low frequencies, turning any negative feedback that might be present around the amplifier into positive feedback.

In bipolar technology, the transconductance of the second stage is normally much higher than the first because it is operated at relatively high current and the transconductance of the bipolar device is proportional to current level. In MOS amplifiers, the transconductances of the two stages tend to be similar, in part because the transconductance varies only as the square root of the drain current. Also, the transconductance of the first stage must be kept reasonably high for thermal noise reasons.

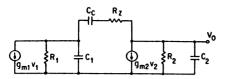

Fortunately, two effective means have evolved for eliminating the effect of the right half-plane zero. One approach has been to insert a source follower in the path from the output back through the compensation capacitor to prevent the propagation of signals forward through the capacitor [7]. This works well, although it requires more devices and dc bias current. An even simpler approach is to insert a nulling resistor in series with the compensation capacitor as shown in Fig. 9 [9]. In this circuit, note that at high frequencies, the output current from the first stage must flow principally as drain current in the second stage transistor. This, in turn, gives rise to voltage variation at the gate of the second stage which is proportional to the small-signal current from the first stage and inversely proportional to the transconductance of the second stage. In the circuit of Fig. 8, this voltage appears directly at the output. However, if a resistor of value equal to  $1/g_{m2}$  is inserted in series with the compensation capacitor, the voltage across this resistor will cancel the small-signal voltage appearing on the left side of the compensation capacitor, resulting in the cancellation of the feedthrough effect.

Using an analysis similar to that performed for the circuit of Fig. 8, one obtains pole locations which are close to those for the original circuit, and a zero location of

$$z = \frac{1}{C_c \left(\frac{1}{g_{m2}} - R_z\right)}.$$

(11)

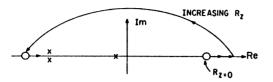

As expected, the zero vanishes when  $R_z$  is made equal to  $1/g_{m2}$ . In fact, the resistor can be further increased to move the zero into the left half-plane to improve the amplifier phase margin [10]. The movement of the zero for increasing values of  $R_z$  is illustrated in Fig. 10.

Fig. 9. Small-signal equivalent circuit of the basic amplifier with nulling resistor added in series with the compensation capacitor.

Fig. 10. Pole-zero diagram showing movement of the transmission zero for various values of  $R_z$ .

A second problem in compensation involves the effects of capacitive loading. From (9), the location of the nondominant pole due to capacitive loading on the output node relative to the unity-gain frequency is determined by the ratio of the second-stage transconductance to that of the first and the ratio of the load capacitance to the compensation capacitance. Since the stage transconductances tend to be similar, this implies that the use of load capacitances of the same order as the compensation capacitance will tend to degrade the unity-gain phase margin because of the encroachment of this nondominant pole. This is of considerable practical significance in switched capacitor filters where large capacitive loads must be driven, and the use of an output stage is undesirable for power dissipation and noise reasons.

## Slew Rate

As in its bipolar counterpart, the CMOS op amp of Fig. 4 displays a relationship among slew rate, bandwidth, input stage bias current, and input device transconductance of

$$SR = \frac{I_{D1}}{g_{m1}} \omega_1 \tag{12}$$

where  $g_{m1}$  is the input transistor transconductance,  $I_{D1}$  is the bias current of the input devices, and  $\omega_1$  is the unity-gain frequency of the amplifier. For the MOS case, this gives

$$SR = \frac{(V_{gs} - V_T)_1}{2} \,\omega_1. \tag{13}$$

In effect, the  $(V_{gs} - V_T)$  of the input stage is the range of differential input voltage for which the input stage stays in the active region. If the bandwidth is kept constant and this range is increased, the slew rate improves. Because this range is usually substantially higher in MOS amplifiers than in bipolar amplifiers, MOS amplifiers usually display relatively good slew rate. In micropower or precision applications where the input transistors are operated at very low  $(V_{gs} - V_T)$ , this may not be the case, however.

#### Power Dissipation

Even for the simple circuit of Fig. 4, the minimum achievable power dissipation is a complex function of the technology used and the particular requirements of the application. In

sampled data systems such as switched capacitor filters, the requirement is that the amplifier be able to settle in a certain time to a certain accuracy with a capacitive load of several picofarads. In this application, the factors determining the minimum power dissipation tend to be the fact that there must be enough standing current in the amplifier class A second stage such that the capacitance can be charged in the allowed time, and the fact that the amplifier must have sufficient phase margin to avoid degradation of the settling time due to ringing and overshoot. The latter requirement dictates a certain minimum  $g_m$  in transistor M6 for a given bandwidth and load capacitor. This, in turn, usually dictates a certain minimum bias current in M6 for a reasonable device size. If a class A source follower output stage is added, then the same comment would apply to its bias current since its  $g_m$ , together with the load capacitance, contribute a nondominant pole.

The preceding discussion is predicted on the use of class A circuitry (i.e., circuits whose available output current is not greater than the quiescent bias current). Quiescent power dissipation can be greatly reduced through the use of dynamic circuits and class B circuits, as discussed later.

## Noise Performance

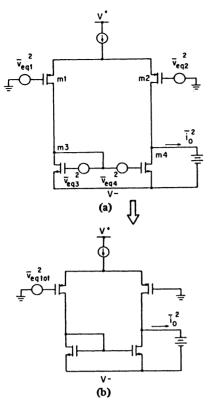

Because of the fact that MOS devices display relatively high 1/f noise, the noise performance is an important design consideration in MOS amplifiers. All four transistors in the input stage contribute to the equivalent input noise, as illustrated in Fig. 11. By simply calculating the output noise for each circuit and equating them (11),

$$V_{eqTOT}^{2} = V_{eq1}^{2} + V_{eq2}^{2} + \left(\frac{g_{m3}}{g_{m1}}\right) \left(V_{eq3}^{2} + V_{eq4}^{2}\right)$$

(14)

where it has been assumed that  $g_{m1} = g_{m2}$  and that  $g_{m3} = g_{m4}$ . Thus, the input transistors contribute to the input noise directly, while the contribution of the loads is reduced by the square of the ratio of their transconductance to that of the input transistors. The significance of this in the design can be further appreciated by considering the input-referred 1/f noise and the input-referred thermal noise separately.

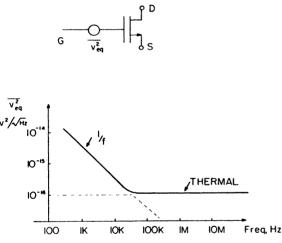

## Input-Referred 1/f Noise

The equivalent input noise spectrum of a typical MOS transistor is shown in Fig. 12. The dependence of the 1/f portion of the spectrum on device geometry and bias conditions has been studied by many authors [12]-[14]. Considerable discrepancy exists in the published data on 1/f noise, indicating that it arises from a mechanism that is strongly affected by details of device fabrication. Perhaps the most widely accepted model for 1/f noise is that for a given device, the gate-referred equivalent mean-squared voltage noise is approximately independent of bias conditions in saturation, and is inversely proportional to the gate capacitance of the device. The following analytical results are based on this model, but it should be emphasized that the actual dependence must be verified for each process technology and device type [12], [15]. Thus,

$$V_{1/f}^{2} = \frac{K}{C_{\text{ox}} WL} \left(\frac{\delta f}{f}\right).$$

(15)

Fig. 11. CMOS input stage. (a) Device noise contributions. (b) Equivalent input noise.

Fig. 12. Typical equivalent input noise, MOS transistor.

Utilizing this assumption, we obtain for the equivalent input noise

$$V_{1/f}^{2} = \frac{2K_{p}}{W_{1}L_{1}C_{\text{ox}}} \left(1 + \frac{K_{n}\mu_{n}L_{1}^{2}}{K_{p}\mu_{p}L_{3}^{2}}\right) \left(\frac{\delta f}{f}\right)$$

(16)

where  $K_n$  and  $K_p$  are the flicker noise coefficients for the nchannel and p-channel devices, respectively. Depending on processing details, these may be comparable or different by a factor of two or more. Note that the multiplying term in front is the input noise of the input transistors, and the second term is the increase in noise due to the loads. It is clear from this second term that the load contribution can be made small by simply making the channel lengths of the loads longer than that of the input transistors by a factor of on the order of two or more. The input transistors can then be made wide enough to achieve the desired performance. It is interesting to note that increasing the width of the channel in the loads does not improve the 1/f noise performance.

## Thermal Noise Performance

The input-referred thermal noise of an MOS transistor is given by [8]

$$V_{eq}^2 = 4kT \left(\frac{2}{3g_m}\right) \delta f.$$

(17a)

Utilizing the same approach as for the flicker noise, this gives

$$V_{eq}^{2} = 4kT \frac{4}{3\sqrt{2\mu_{p}C_{ox}(W/L)_{1}I_{D}}} \left(1 + \sqrt{\frac{\mu_{n}(W/L)_{3}}{\mu_{p}(W/L)_{1}}}\right).$$

(17b)

Again, the first term represents the thermal noise from the input transistors, and the term in parentheses represents the fractional increase in noise due to the loads. The term in parentheses will be small if the W/L's are chosen so that the transconductance of the input devices is much larger than that of the loads. If this condition is satisfied, then the input noise is simply determined by the transconductance of the input transistors.

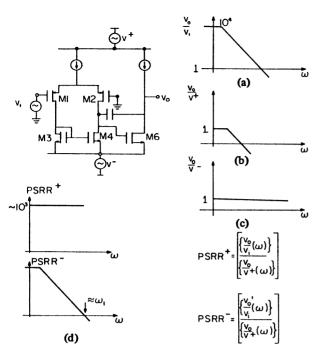

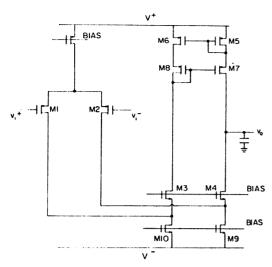

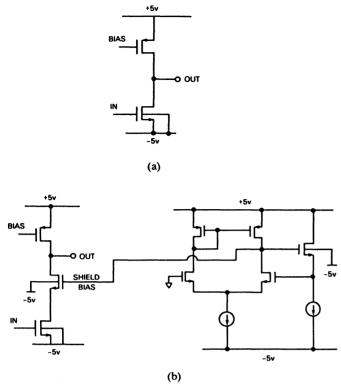

## Power Supply Rejection and Supply Capacitance

Power supply rejection ratio (PSRR) is a parameter of considerable importance in MOS amplifier design. One reason for this is that in complex analog-digital systems, the analog circuitry must coexist on the same chip with large amounts of digital circuitry. Even though separate analog and digital supply buses are often run on chip, it is hard to avoid some coupling of digital noise into the analog supplies. A second reason is that in many systems, switching regulators are used which introduce power supply noise into the supply voltage lines. If these high-frequency signals couple into the signal path in a sampled data system such as a switched capacitor filter or high-speed A/D converter, they can be aliased down into the frequency band where the signal resides and degrade the overall system signal-to-noise ratio. The parameters reflecting susceptibility to this phenomenon in the operational amplifier are the high-frequency PSRR and the supply capacitance.

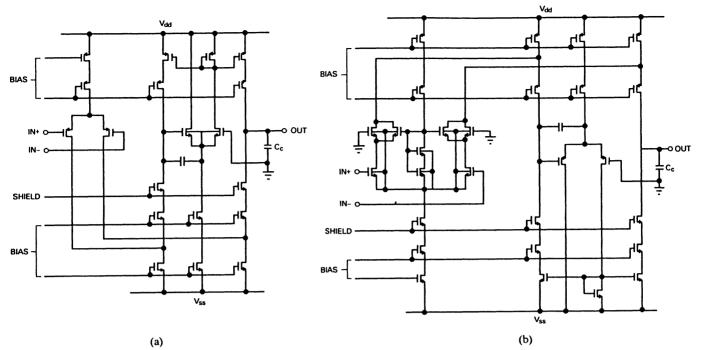

The PSRR of an operational amplifier is simply the ratio of the voltage gain from the input to the output (open loop) to that from the supply to the output. It can be easily demonstrated that for frequencies less than the unity-gain frequency, if the operational amplifier is connected in a follower configuration and an ac signal is superimposed on one of the power supplies, the signal appearing at the output is equal to the applied signal divided by the PSRR for that supply. The basic circuit of Fig. 4 is particularly poor in terms of its high-frequency rejection from the negative power supply, as illustrated in Fig. 13. The primary reason is that as the applied frequency increases, the impedence of the compensation capacitor decreases, effectively shorting the drain of M6 to its gate for ac signals. Thus, the gain from the negative supply to the output

Fig. 13. High-frequency PSRR of bipolar-derived op amp. (a) Gain from input to output. (b) Gain from positive supply to output. (c) Gain from negative supply to output. (d) Positive and negative PSRR.

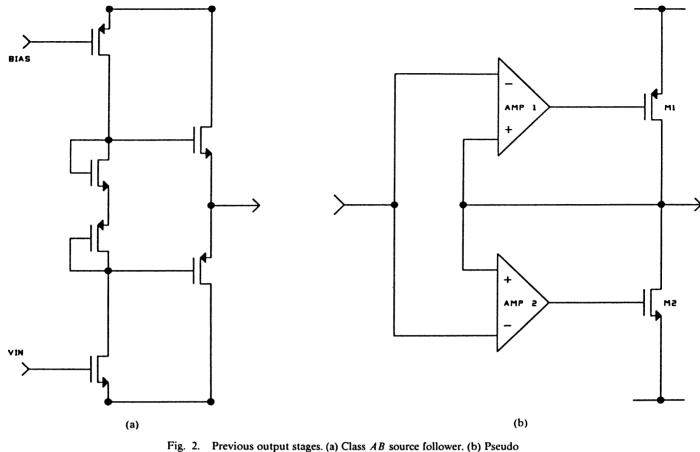

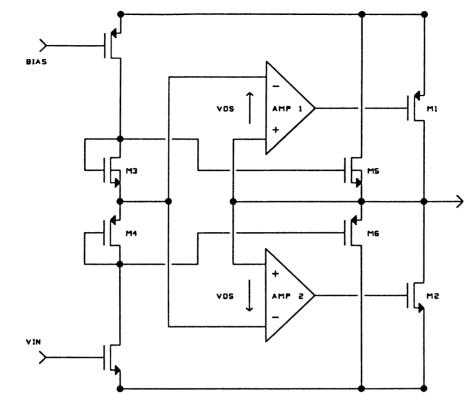

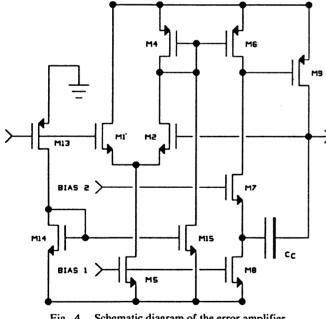

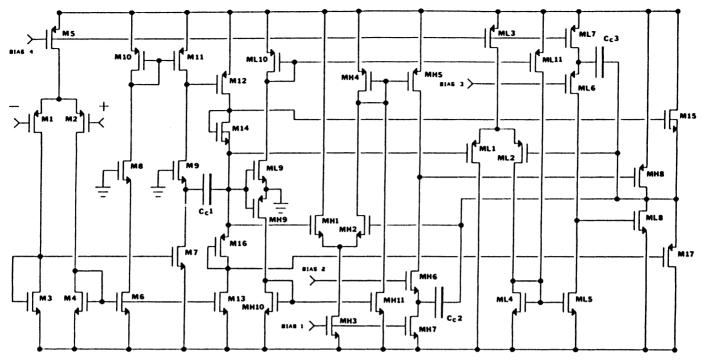

approaches unity and stays there out to very high frequencies. The same phenomenon causes the gain from the positive supply to fall with frequency as the open-loop gain does, so that the positive PSRR remains relatively flat with increasing frequency. The negative supply PSRR falls to approximately unity at the unity-gain frequency of the operational amplifier. Several alternative amplifier architectures have evolved which alleviate this problem, and they are discussed in a later section.