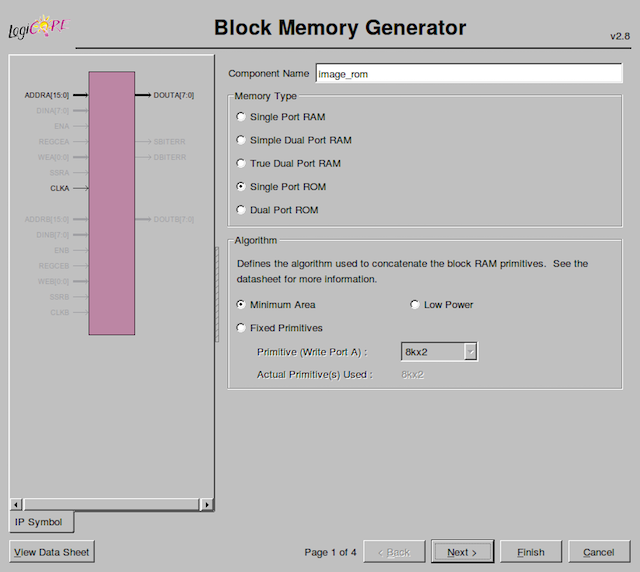

Under your project add a new source using IP Coregn & Architecture wizard and give it a filename in your project folder. [Click Next]

For Core Type select Memory/RAMs & ROMs/Single Port Bock Memory optimized for area. [Click Next]

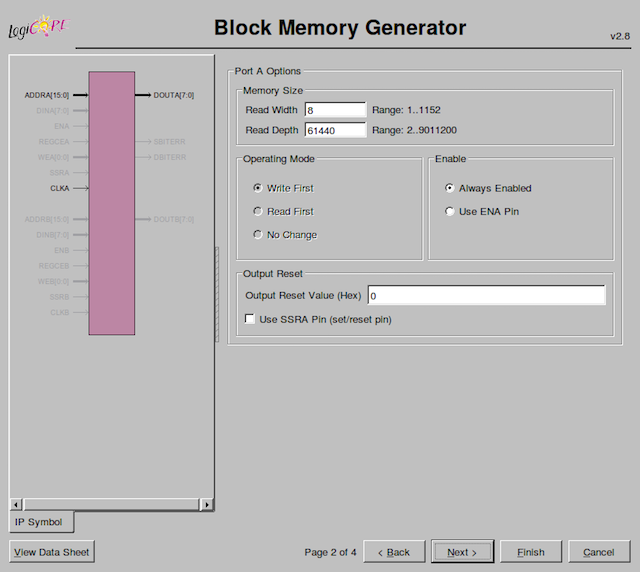

In this example we will create a 8 bit wide ROM for a 256x240 image (=614400). [Click Next]

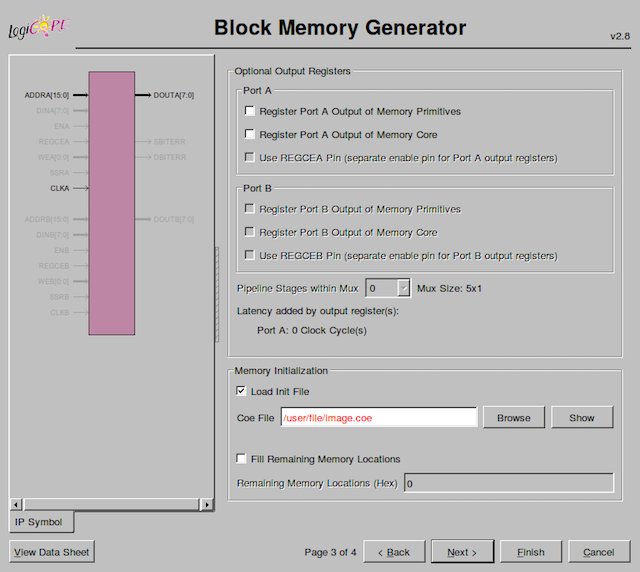

For a ROM, provide a memory initization (COE) file and check "Load Init File".

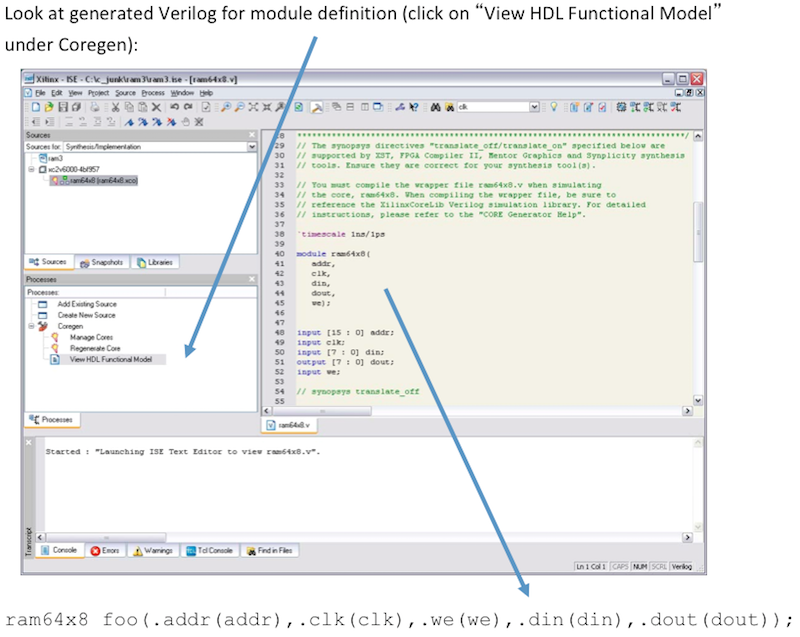

The ports names for the memory can be viewed in the generated Verilog

under "view HDL Functional Model". For this example, we generated a 64K x

8 RAM with clock (clk), address (addr), write enable

(we), data in (din) and data out (dout).

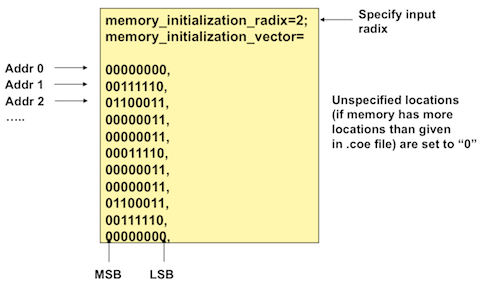

For ROMs, the memory is loaded with the COE files. Here is the content of a

COE file.

We have MATLAB scripts that

extracts the pixel values from BMP files and

output a COE file.