# **REC FPGA Seminar IAP 1998**

Session 1: Architecture, Economics, and Applications of the FPGA

Robotics and Electronics Cooperative FPGA Seminar IAP 1998

1

### Seminar Format Four 45 minute open sessions - two on Wed. January 21st, two on Fri. January 23rd - session 1: Architecture, Economics, and Applications of FPGAs - session 2: Design tools, Configuration and Practical Considerations - session 3: Advanced FPGA design techniques, Optimizations, and Tricks - session 4: Future Directions and Applications of FPGAs ٠ Hands-on session (preregistered only) - starts on Mon. January 26th in 6.004 lab, continues through the week - three 45 minute orientations for design tools and RHP4K board - one basic lab and one advanced lab assignment • "cylon" lab • pong, the video game - plus two days open lab time for your own project Robotics and Electronics Cooperative FPGA Seminar IAP 1998 2

## Architecture: Configuration

- Configuration method

- In-circuit programmable methods

- SRAM based (Xilinx 2K/3K/4K, Altera 8K/10K, Lucent Orca)

- volatile, but fast configuration times

- must reprogram on every power-up

- some architectures offer partial reconfiguration (Atmel)

- most expensive in terms of area and timing costs

- standard CMOS process

- EEPROM based (Altera 7K/9K)

- nonvolatile, slow config; sometimes requires extra voltages for programming and erasing

- special silicon processing required

Robotics and Electronics Cooperative FPGA Seminar IAP 1998

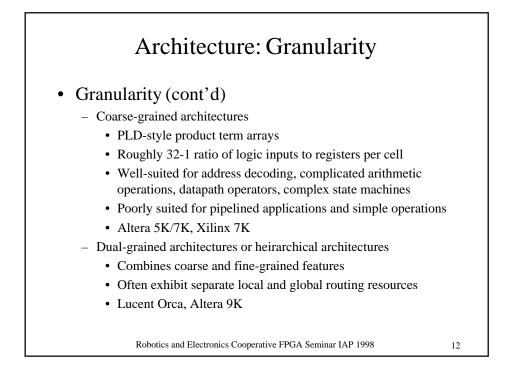

## Architecture: Granularity

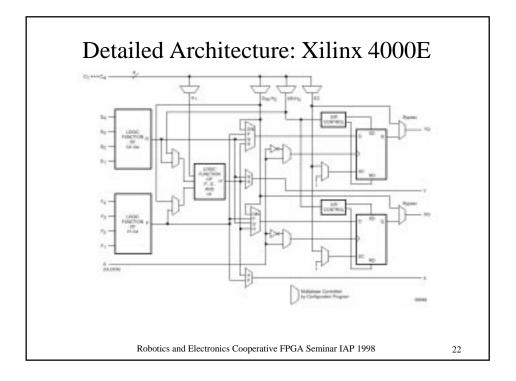

#### • Granularity

- Defined as ratio of logic per cell versus routing

- Very fine-grained architectures

- Partial set of n-input boolean functions per cell

- Roughly 6-1 ratio of logic inputs to registers per cell

- Atmel, Actel

- Fine-grained architectures

- Full set of n-input boolean functions per cell

- Sometimes multiple n-input boolean functions per cell

- Roughly 8-1 ratio of logic inputs to registers per cell

- Well-suited for state machines, simple arithmetic, pipelined applications

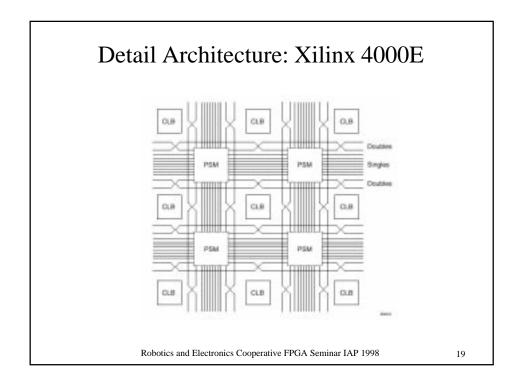

- Xilinx 3K/4K, Altera 8K/10K

Robotics and Electronics Cooperative FPGA Seminar IAP 1998

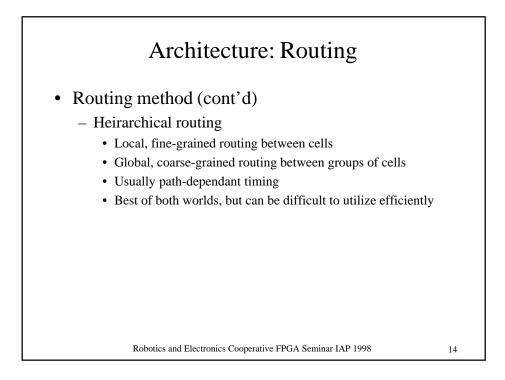

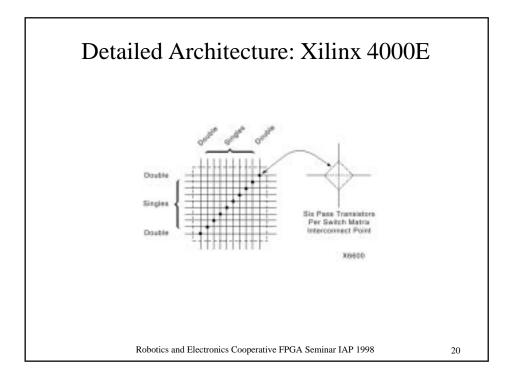

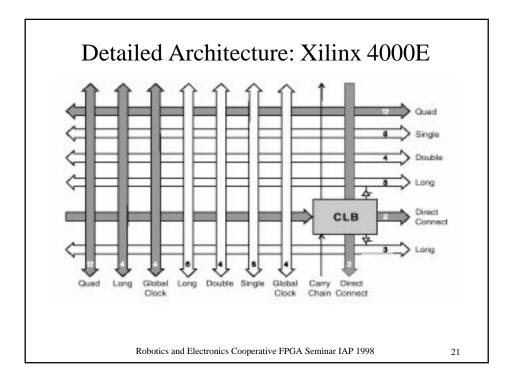

- Routing method

- Fine-grained

- Short hops (1 to 8 logic cells spanned per track)

- Path-dependant timing

- Exhibits high density

- Flexible switch matrices

- Less logic placement constraints

#### - Coarse-grained

- Tracks span entire chip

- Fixed timing regardless of logic placement

- Lower density

- · Logic placement constrained by routing availability

Robotics and Electronics Cooperative FPGA Seminar IAP 1998

- total (device) reconfiguration (no partial reconfig)

- several configuration modes available

- parallel and serial modes

- master and slave modes

- daisy chain ability

- device bitstreams between 50Kbits and 400Kbits

- config rate around 10 Mbit/sec

- max reconfig rate in a few tens of milliseconds

- typical reconfig in a couple of seconds

Robotics and Electronics Cooperative FPGA Seminar IAP 1998

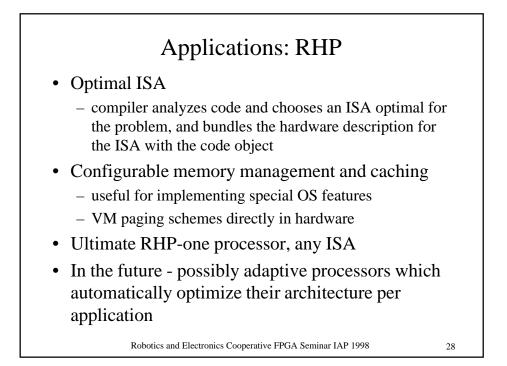

# Applications: RHP

- Direct implementation of algorithms in hardware

- circumvents instruction fetch, decode, issue overhead

- unrestricted parallelism

- disadvantage: little hardware abstraction, difficult to use

- RISC framework with reconfigurable instruction set

- user-defined instructions depending on process context

- prevents the MMX disease

- easier to use, more hardware abstraction, but lower performance

Robotics and Electronics Cooperative FPGA Seminar IAP 1998

- Ideal for implementing simple, repetative operations (overhead operations)

- time synchronization on Novell networks

- CAM lookup tables for IP routing and neural nets

- encryption/decryption

- FEA (finite element analysis)

- Relaxation networks

- database searching

- higher peformance with special architectures (embedded RAM)

Robotics and Electronics Cooperative FPGA Seminar IAP 1998