# Formal Characterization of Hardware Transmitters for Secure Software and Hardware Repair

Yao Hsiao<sup>1</sup>, Christopher W. Fletcher<sup>2</sup>, Caroline Trippel<sup>1</sup>

<sup>1</sup>Stanford University, <sup>2</sup>University of Illinois Urbana-Champaign

### Problem:

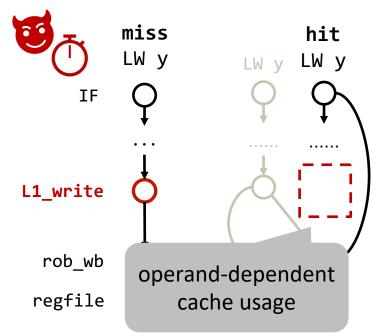

Hardware side-channel attacks exploit unsafe instructions (i.e., transmitters) whose execution creates operand-dependent hardware resource usage that can be observed via some means (e.g., exec. time)

<sup>&</sup>lt;sup>1</sup>Jose Vicarte et al. "Opening Pandora's Box: A Systematic Study of New Ways Microarchitecture Can Leak Private Data". In: ISCA'21.

# Formal Characterization of Hardware Transmitters for Secure Software and Hardware Repair

Yao Hsiao<sup>1</sup>, Christopher W. Fletcher<sup>2</sup>, Caroline Trippel<sup>1</sup>

<sup>1</sup>Stanford University, <sup>2</sup>University of Illinois Urbana-Champaign

### Problem:

- Hardware side-channel attacks exploit unsafe instructions (i.e., transmitters) whose execution creates operand-dependent hardware resource usage that can be observed via some means (e.g., exec. time)

- Mitigating such attacks requires identifying all unsafe instructions on a given RTL design

- Many unsafe instructions can be latent in microarchitecture<sup>1</sup>

<sup>&</sup>lt;sup>1</sup>Jose Vicarte et al. "Opening Pandora's Box: A Systematic Study of New Ways Microarchitecture Can Leak Private Data". In: ISCA'21.

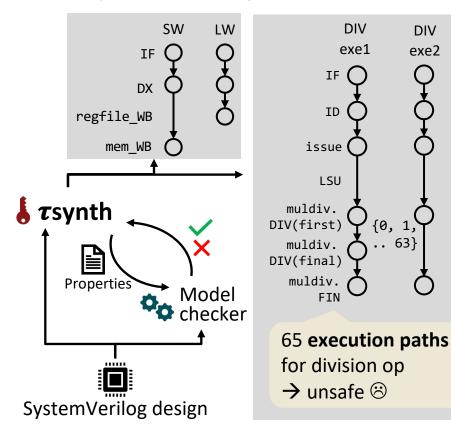

## ausynth: Automated approach and tool for discovering and characterizing unsafe instructions on an input RTL design

## Methodology:

Exhaustive exploration of instruction execution paths using a combination of formal property generation and model checking

### Results:

Identifies 15 timing-differentiable transmitters on RISC-V CVA6

### Ongoing work:

Extracting data that a transmitter depends on to exhibit variable execution