|

|

for 6.111 Introduction to Digital Systems

6.111 home → Labkit home → Test Programs → General I/O Ports Test

General I/O Ports Test

by Nathan IckesIntroduction

Theiotest program tests the following labkit components:

- All four user I/O ports

- The daughtercard connector

- All four logic analyzer ports

- The RS-232 port

- The two PS/2 ports

- The builtin 27MHz oscillator

- The two oscillator sockets

- The alphanumeric displays

- The eight slide switches

- The nine pushbuttons

- The eight individual, user-controlled LEDs

iotest2 program.

Test Setup

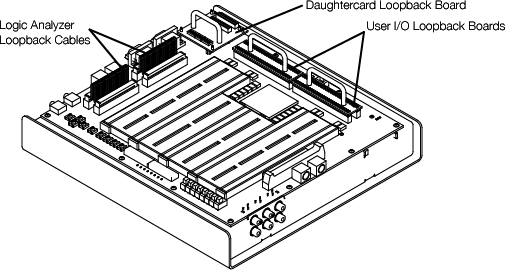

The following equipment is required to run this test

- One daughtercard loopback board

- Two user I/O loopback boards

- Two logic analyzer loopback cables

- One PS/2 keyboard

- A PC with an RS-232 port and an RS-232 terminal program (e.g., HyperTerm or Minicom)

- An RS-232 nullmodem cable with female DB9 connectors

- For configuring using a CompactFlash card:

iotest.ace - For direct download to the FPGA via JTAG:

iotest.bit

LEDs, Switches, and Pushbuttons

The eight user-controlled LEDs, nine pushbuttons, and eight slide-switches (all located near the lower edge of the board) should behave as follows.

- LED 0 (D9): On when the "Enter" pushbutton (S5) is pressed; blinking when pushbutton 0 (S9) is pressed; on if switch 0 (S17) is up; off otherwise.

- LED 1 (D8): On when the "Enter" pushbutton (S5) is pressed; blinking when pushbutton 1 (S8) is pressed; on if switch 1 (S16) is up; off otherwise.

- LED 2 (D7): On when the "Enter" pushbutton (S5) is pressed; blinking when pushbutton 2 (S7) is pressed; on if switch 2 (S15) is up; off otherwise.

- LED 3 (D6): On when the "Enter" pushbutton (S5) is pressed; blinking when pushbutton 3 (S6) is pressed; on if switch 3 (S14) is up; off otherwise.

- LED 4 (D5): On when the "Enter" pushbutton (S5) is pressed; blinking when the "right" pushbutton (S4) is pressed; on if switch 4 (S13) is up; off otherwise.

- LED 5 (D4): On when the "Enter" pushbutton (S5) is pressed; blinking when the "left" pushbutton (S3) is pressed; on if switch 5 (S12) is up; off otherwise.

- LED 6 (D3): On when the "Enter" pushbutton (S5) is pressed; blinking when the "down" pushbutton (S2) is pressed; on if switch 6 (S11) is up; off otherwise.

- LED 7 (D2): On when the "Enter" pushbutton (S5) is pressed; blinking when the "up" pushbutton (S1) is pressed; on if switch 7 (S10) is up; off otherwise.

The clock used to blink each LED when the corresponding pushbutton is pressed is derived from the labkit's built-in 27MHz oscillator (Y4).

Alphanumeric Displays

The alphanumeric display is used to display status information from several of the system tests. When the FPGA is first configured, the display should show something like this:

Alphanumeric display on startup

If the display is blank, or shows mangled characters, something is wrong.

Oscillators

The labkit's built-in 27MHz oscillator is used by the alphanumeric display driver. If the display is functioning, it is safe to assume the built-in oscillator is functioning properly.

The status of the clock signals from the two oscillator sockets in the upper-left corner of the PCB is indicated by the third item on the alphanumeric display ("C:??"). The first character after the colon indicates the state of the Clock 1 oscillator (Y2), and the next character indicates the status of the Clock 2 oscillator (Y3). An upwards pointing arrow indicates the respective clock signal is stuck high; a downwards pointing arrow indicates the respective clock signal is stuck low; and an arrow pointing both upwards and downwards indicates that the respective clock signal is properly toggling.

Obviously, in order to test the oscillator sockets, it is necessary to install an actual oscillator in each socket. Any 3.3V oscillator, with a frequency between 1MHz and 10MHz can be used.

PS/2 Ports

Testing the PS/2 ports requires a PS/2 compatible keyboard. The keyboard should first be plugged into the keyboard port on the labkit (J9). Note that PS/2 is not designed to be a hot-pluggable interface. It's best to plug in the keyboard with the labkit powered off. The keyboard controlled may not reset properly if the keyboard is plugged in while the labkit is on.

Typing any of the keys A through F should cause the first few characters of the alphanumeric display to read "K:X", where X is the character that was typed. The PS/2 test interface only recognizes the key codes A-F. All other key codes are translated as "?"--this includes repeat and release codes.

The mouse port (J8) is tested using a keyboard, in the same manner as the keyboard port. The second field on the alphanumeric display ("M:X") indicates the last key code received over the mouse port.

RS-232 Port

A trivial loopback test is implemented, which includes flow control. Connect the labkit's RS-232 connector (J7) to a PC, using a null-modem cable. Then launch a terminal program (such as HyperTerm) on the PC. Any baud rate, parity, and stop bit settings can be used. Hardware flow control should be turned on, in order to test the labkit's CTS and RTS lines. Local echo should be turned off. Characters typed into the terminal on the PC should be echoed by the labkit.

User I/O, Daughtercard, and Logic Analyzer Connectors

The user I/O, daughtercard, and logic analyzer connectors are tested using a loopback arrangement. The pins of these connectors are split into two banks, as shown in the below table.

| Bank A | Bank B |

|---|---|

| User 1 User 3 Daughtercard [21:0] Logic Analyzer 1 Logic Analyzer 2 |

User 2 User 4 Daughtercard [43:22] Logic Analyzer 3 Logic Analyzer 4 |

The User I/O and Daughtercard loopback test boards must be installed on the labkit in order to connect the banks together. Two user I/O loopback boards are required: one should be installed across user 1 and user 3, and the other across user 2 and user 4. The connectors on the user I/O loopback boards are not polarized, so it is possible to install the boards backwards. The boards must be installed so that the text on the top of the boards is right side up. The daughtercard loopback board installs across J14 and J15. The 22 DIP switches on the daughtercard loopback board must set to the "on" position.

Loopback boards installed on the labkit

The I/O pins are tested using a walking one pattern. One at a time, the pins of bank A are driven high, and bank B is monitored to see that only the corresponding pin in bank B reads high. The other pins in bank A, and all of the pins in bank B are tristated, but with a pulldown resistor in the FPGA. Once all the pins in bank A have been tested, bank B is used to drive bank A, in a similar patter.

The test pattern repeats indefinitely, as long as no errors are detected. If there are no errors, and the entire test has run at least once, the last character of the alphanumeric display will read "P". If an error is detected, the test stops immediately, and an error code is displayed on the last two characters of the alphanumeric display. The table below shows, for each error code, which I/O pins is being driven high, and which pin in the other bank was expected to receive the logic high value.

Error Codes

| Error Code | Driver | Receiver |

|---|---|---|

| 00 | User I/O Bank 1, Pin 0 | User I/O Bank 3, Pin 0 |

| 01 | User I/O Bank 1, Pin 1 | User I/O Bank 3, Pin 1 |

| 02 | User I/O Bank 1, Pin 2 | User I/O Bank 3, Pin 2 |

| 03 | User I/O Bank 1, Pin 3 | User I/O Bank 3, Pin 3 |

| 04 | User I/O Bank 1, Pin 4 | User I/O Bank 3, Pin 4 |

| 05 | User I/O Bank 1, Pin 5 | User I/O Bank 3, Pin 5 |

| 06 | User I/O Bank 1, Pin 6 | User I/O Bank 3, Pin 6 |

| 07 | User I/O Bank 1, Pin 7 | User I/O Bank 3, Pin 7 |

| 08 | User I/O Bank 1, Pin 8 | User I/O Bank 3, Pin 8 |

| 09 | User I/O Bank 1, Pin 9 | User I/O Bank 3, Pin 9 |

| 0A | User I/O Bank 1, Pin 10 | User I/O Bank 3, Pin 10 |

| 0B | User I/O Bank 1, Pin 11 | User I/O Bank 3, Pin 11 |

| 0C | User I/O Bank 1, Pin 12 | User I/O Bank 3, Pin 12 |

| 0D | User I/O Bank 1, Pin 13 | User I/O Bank 3, Pin 13 |

| 0E | User I/O Bank 1, Pin 14 | User I/O Bank 3, Pin 14 |

| 0F | User I/O Bank 1, Pin 15 | User I/O Bank 3, Pin 15 |

| 10 | User I/O Bank 1, Pin 16 | User I/O Bank 3, Pin 16 |

| 11 | User I/O Bank 1, Pin 17 | User I/O Bank 3, Pin 17 |

| 12 | User I/O Bank 1, Pin 18 | User I/O Bank 3, Pin 18 |

| 13 | User I/O Bank 1, Pin 19 | User I/O Bank 3, Pin 19 |

| 14 | User I/O Bank 1, Pin 20 | User I/O Bank 3, Pin 20 |

| 15 | User I/O Bank 1, Pin 21 | User I/O Bank 3, Pin 21 |

| 16 | User I/O Bank 1, Pin 22 | User I/O Bank 3, Pin 22 |

| 17 | User I/O Bank 1, Pin 23 | User I/O Bank 3, Pin 23 |

| 18 | User I/O Bank 1, Pin 24 | User I/O Bank 3, Pin 24 |

| 19 | User I/O Bank 1, Pin 25 | User I/O Bank 3, Pin 25 |

| 1A | User I/O Bank 1, Pin 26 | User I/O Bank 3, Pin 26 |

| 1B | User I/O Bank 1, Pin 27 | User I/O Bank 3, Pin 27 |

| 1C | User I/O Bank 1, Pin 28 | User I/O Bank 3, Pin 28 |

| 1D | User I/O Bank 1, Pin 29 | User I/O Bank 3, Pin 29 |

| 1E | User I/O Bank 1, Pin 30 | User I/O Bank 3, Pin 30 |

| 1F | User I/O Bank 1, Pin 31 | User I/O Bank 3, Pin 31 |

| 20 | User I/O Bank 2, Pin 0 | User I/O Bank 4, Pin 0 |

| 21 | User I/O Bank 2, Pin 1 | User I/O Bank 4, Pin 1 |

| 22 | User I/O Bank 2, Pin 2 | User I/O Bank 4, Pin 2 |

| 23 | User I/O Bank 2, Pin 3 | User I/O Bank 4, Pin 3 |

| 24 | User I/O Bank 2, Pin 4 | User I/O Bank 4, Pin 4 |

| 25 | User I/O Bank 2, Pin 5 | User I/O Bank 4, Pin 5 |

| 26 | User I/O Bank 2, Pin 6 | User I/O Bank 4, Pin 6 |

| 27 | User I/O Bank 2, Pin 7 | User I/O Bank 4, Pin 7 |

| 28 | User I/O Bank 2, Pin 8 | User I/O Bank 4, Pin 8 |

| 29 | User I/O Bank 2, Pin 9 | User I/O Bank 4, Pin 9 |

| 2A | User I/O Bank 2, Pin 10 | User I/O Bank 4, Pin 10 |

| 2B | User I/O Bank 2, Pin 11 | User I/O Bank 4, Pin 11 |

| 2C | User I/O Bank 2, Pin 12 | User I/O Bank 4, Pin 12 |

| 2D | User I/O Bank 2, Pin 13 | User I/O Bank 4, Pin 13 |

| 2E | User I/O Bank 2, Pin 14 | User I/O Bank 4, Pin 14 |

| 2F | User I/O Bank 2, Pin 15 | User I/O Bank 4, Pin 15 |

| 30 | User I/O Bank 2, Pin 16 | User I/O Bank 4, Pin 16 |

| 31 | User I/O Bank 2, Pin 17 | User I/O Bank 4, Pin 17 |

| 32 | User I/O Bank 2, Pin 18 | User I/O Bank 4, Pin 18 |

| 33 | User I/O Bank 2, Pin 19 | User I/O Bank 4, Pin 19 |

| 34 | User I/O Bank 2, Pin 20 | User I/O Bank 4, Pin 20 |

| 35 | User I/O Bank 2, Pin 21 | User I/O Bank 4, Pin 21 |

| 36 | User I/O Bank 2, Pin 22 | User I/O Bank 4, Pin 22 |

| 37 | User I/O Bank 2, Pin 23 | User I/O Bank 4, Pin 23 |

| 38 | User I/O Bank 2, Pin 24 | User I/O Bank 4, Pin 24 |

| 39 | User I/O Bank 2, Pin 25 | User I/O Bank 4, Pin 25 |

| 3A | User I/O Bank 2, Pin 26 | User I/O Bank 4, Pin 26 |

| 3B | User I/O Bank 2, Pin 27 | User I/O Bank 4, Pin 27 |

| 3C | User I/O Bank 2, Pin 28 | User I/O Bank 4, Pin 28 |

| 3D | User I/O Bank 2, Pin 29 | User I/O Bank 4, Pin 29 |

| 3E | User I/O Bank 2, Pin 30 | User I/O Bank 4, Pin 30 |

| 3F | User I/O Bank 2, Pin 31 | User I/O Bank 4, Pin 31 |

| 40 | Daughtercard Pin 0 | Daughtercard Pin 43 |

| 41 | Daughtercard Pin 1 | Daughtercard Pin 42 |

| 42 | Daughtercard Pin 2 | Daughtercard Pin 41 |

| 43 | Daughtercard Pin 3 | Daughtercard Pin 40 |

| 44 | Daughtercard Pin 4 | Daughtercard Pin 39 |

| 45 | Daughtercard Pin 5 | Daughtercard Pin 38 |

| 46 | Daughtercard Pin 6 | Daughtercard Pin 37 |

| 47 | Daughtercard Pin 7 | Daughtercard Pin 36 |

| 48 | Daughtercard Pin 8 | Daughtercard Pin 35 |

| 49 | Daughtercard Pin 9 | Daughtercard Pin 34 |

| 4A | Daughtercard Pin 10 | Daughtercard Pin 33 |

| 4B | Daughtercard Pin 11 | Daughtercard Pin 32 |

| 4C | Daughtercard Pin 12 | Daughtercard Pin 31 |

| 4D | Daughtercard Pin 13 | Daughtercard Pin 30 |

| 4E | Daughtercard Pin 14 | Daughtercard Pin 29 |

| 4F | Daughtercard Pin 15 | Daughtercard Pin 28 |

| 50 | Daughtercard Pin 16 | Daughtercard Pin 27 |

| 51 | Daughtercard Pin 17 | Daughtercard Pin 26 |

| 52 | Daughtercard Pin 18 | Daughtercard Pin 25 |

| 53 | Daughtercard Pin 19 | Daughtercard Pin 24 |

| 54 | Daughtercard Pin 20 | Daughtercard Pin 23 |

| 55 | Daughtercard Pin 21 | Daughtercard Pin 22 |

| 56 | Analyzer Pod 1, Channel 0 (Pin 37) | Analyzer Pod 2, Channel 0 (Pin 37) |

| 57 | Analyzer Pod 1, Channel 1 (Pin 35) | Analyzer Pod 2, Channel 1 (Pin 35) |

| 58 | Analyzer Pod 1, Channel 2 (Pin 33) | Analyzer Pod 2, Channel 2 (Pin 33) |

| 59 | Analyzer Pod 1, Channel 3 (Pin 31) | Analyzer Pod 2, Channel 3 (Pin 31) |

| 5A | Analyzer Pod 1, Channel 4 (Pin 29) | Analyzer Pod 2, Channel 4 (Pin 29) |

| 5B | Analyzer Pod 1, Channel 5 (Pin 27) | Analyzer Pod 2, Channel 5 (Pin 27) |

| 5C | Analyzer Pod 1, Channel 6 (Pin 25) | Analyzer Pod 2, Channel 6 (Pin 25) |

| 5D | Analyzer Pod 1, Channel 7 (Pin 23) | Analyzer Pod 2, Channel 7 (Pin 23) |

| 5E | Analyzer Pod 1, Channel 8 (Pin 21) | Analyzer Pod 2, Channel 8 (Pin 21) |

| 5F | Analyzer Pod 1, Channel 9 (Pin 19) | Analyzer Pod 2, Channel 9 (Pin 19) |

| 60 | Analyzer Pod 1, Channel 10 (Pin 17) | Analyzer Pod 2, Channel 10 (Pin 17) |

| 61 | Analyzer Pod 1, Channel 11 (Pin 15) | Analyzer Pod 2, Channel 11 (Pin 15) |

| 62 | Analyzer Pod 1, Channel 12 (Pin 13) | Analyzer Pod 2, Channel 12 (Pin 13) |

| 63 | Analyzer Pod 1, Channel 13 (Pin 11) | Analyzer Pod 2, Channel 13 (Pin 11) |

| 64 | Analyzer Pod 1, Channel 14 (Pin 9) | Analyzer Pod 2, Channel 14 (Pin 9) |

| 65 | Analyzer Pod 1, Channel 15 (Pin 7) | Analyzer Pod 2, Channel 15 (Pin 7) |

| 66 | Analyzer Pod 1, Clock Channel (Pin 16) | Analyzer Pod 2, Clock Channel (Pin 16) |

| 67 | Analyzer Pod 3, Channel 0 (Pin 37) | Analyzer Pod 4, Channel 0 (Pin 37) |

| 68 | Analyzer Pod 3, Channel 1 (Pin 35) | Analyzer Pod 4, Channel 1 (Pin 35) |

| 69 | Analyzer Pod 3, Channel 2 (Pin 33) | Analyzer Pod 4, Channel 2 (Pin 33) |

| 6A | Analyzer Pod 3, Channel 3 (Pin 31) | Analyzer Pod 4, Channel 3 (Pin 31) |

| 6B | Analyzer Pod 3, Channel 4 (Pin 29) | Analyzer Pod 4, Channel 4 (Pin 29) |

| 6C | Analyzer Pod 3, Channel 5 (Pin 27) | Analyzer Pod 4, Channel 5 (Pin 27) |

| 6D | Analyzer Pod 3, Channel 6 (Pin 25) | Analyzer Pod 4, Channel 6 (Pin 25) |

| 6E | Analyzer Pod 3, Channel 7 (Pin 23) | Analyzer Pod 4, Channel 7 (Pin 23) |

| 6F | Analyzer Pod 3, Channel 8 (Pin 21) | Analyzer Pod 4, Channel 8 (Pin 21) |

| 70 | Analyzer Pod 3, Channel 9 (Pin 19) | Analyzer Pod 4, Channel 9 (Pin 19) |

| 71 | Analyzer Pod 3, Channel 10 (Pin 17) | Analyzer Pod 4, Channel 10 (Pin 17) |

| 72 | Analyzer Pod 3, Channel 11 (Pin 15) | Analyzer Pod 4, Channel 11 (Pin 15) |

| 73 | Analyzer Pod 3, Channel 12 (Pin 13) | Analyzer Pod 4, Channel 12 (Pin 13) |

| 74 | Analyzer Pod 3, Channel 13 (Pin 11) | Analyzer Pod 4, Channel 13 (Pin 11) |

| 75 | Analyzer Pod 3, Channel 14 (Pin 9) | Analyzer Pod 4, Channel 14 (Pin 9) |

| 76 | Analyzer Pod 3, Channel 15 (Pin 7) | Analyzer Pod 4, Channel 15 (Pin 7) |

| 77 | Analyzer Pod 2, Clock Channel (Pin 16) | Analyzer Pod 4, Clock Channel (Pin 16) |

| 78 | User I/O Bank 3, Pin 0 | User I/O Bank 1, Pin 0 |

| 79 | User I/O Bank 3, Pin 1 | User I/O Bank 1, Pin 1 |

| 7A | User I/O Bank 3, Pin 2 | User I/O Bank 1, Pin 2 |

| 7B | User I/O Bank 3, Pin 3 | User I/O Bank 1, Pin 3 |

| 7C | User I/O Bank 3, Pin 4 | User I/O Bank 1, Pin 4 |

| 7D | User I/O Bank 3, Pin 5 | User I/O Bank 1, Pin 5 |

| 7E | User I/O Bank 3, Pin 6 | User I/O Bank 1, Pin 6 |

| 7F | User I/O Bank 3, Pin 7 | User I/O Bank 1, Pin 7 |

| 80 | User I/O Bank 3, Pin 8 | User I/O Bank 1, Pin 8 |

| 81 | User I/O Bank 3, Pin 9 | User I/O Bank 1, Pin 9 |

| 82 | User I/O Bank 3, Pin 10 | User I/O Bank 1, Pin 10 |

| 83 | User I/O Bank 3, Pin 11 | User I/O Bank 1, Pin 11 |

| 84 | User I/O Bank 3, Pin 12 | User I/O Bank 1, Pin 12 |

| 85 | User I/O Bank 3, Pin 13 | User I/O Bank 1, Pin 13 |

| 86 | User I/O Bank 3, Pin 14 | User I/O Bank 1, Pin 14 |

| 87 | User I/O Bank 3, Pin 15 | User I/O Bank 1, Pin 15 |

| 88 | User I/O Bank 3, Pin 16 | User I/O Bank 1, Pin 16 |

| 89 | User I/O Bank 3, Pin 17 | User I/O Bank 1, Pin 17 |

| 8A | User I/O Bank 3, Pin 18 | User I/O Bank 1, Pin 18 |

| 8B | User I/O Bank 3, Pin 19 | User I/O Bank 1, Pin 19 |

| 8C | User I/O Bank 3, Pin 20 | User I/O Bank 1, Pin 20 |

| 8D | User I/O Bank 3, Pin 21 | User I/O Bank 1, Pin 21 |

| 8E | User I/O Bank 3, Pin 22 | User I/O Bank 1, Pin 22 |

| 8F | User I/O Bank 3, Pin 23 | User I/O Bank 1, Pin 23 |

| 90 | User I/O Bank 3, Pin 24 | User I/O Bank 1, Pin 24 |

| 91 | User I/O Bank 3, Pin 25 | User I/O Bank 1, Pin 25 |

| 92 | User I/O Bank 3, Pin 26 | User I/O Bank 1, Pin 26 |

| 93 | User I/O Bank 3, Pin 27 | User I/O Bank 1, Pin 27 |

| 94 | User I/O Bank 3, Pin 28 | User I/O Bank 1, Pin 28 |

| 95 | User I/O Bank 3, Pin 29 | User I/O Bank 1, Pin 29 |

| 96 | User I/O Bank 3, Pin 30 | User I/O Bank 1, Pin 30 |

| 97 | User I/O Bank 3, Pin 31 | User I/O Bank 1, Pin 31 |

| 98 | User I/O Bank 4, Pin 0 | User I/O Bank 2, Pin 0 |

| 99 | User I/O Bank 4, Pin 1 | User I/O Bank 2, Pin 1 |

| 9A | User I/O Bank 4, Pin 2 | User I/O Bank 2, Pin 2 |

| 9B | User I/O Bank 4, Pin 3 | User I/O Bank 2, Pin 3 |

| 9C | User I/O Bank 4, Pin 4 | User I/O Bank 2, Pin 4 |

| 9D | User I/O Bank 4, Pin 5 | User I/O Bank 2, Pin 5 |

| 9E | User I/O Bank 4, Pin 6 | User I/O Bank 2, Pin 6 |

| 9F | User I/O Bank 4, Pin 7 | User I/O Bank 2, Pin 7 |

| A0 | User I/O Bank 4, Pin 8 | User I/O Bank 2, Pin 8 |

| A1 | User I/O Bank 4, Pin 9 | User I/O Bank 2, Pin 9 |

| A2 | User I/O Bank 4, Pin 10 | User I/O Bank 2, Pin 10 |

| A3 | User I/O Bank 4, Pin 11 | User I/O Bank 2, Pin 11 |

| A4 | User I/O Bank 4, Pin 12 | User I/O Bank 2, Pin 12 |

| A5 | User I/O Bank 4, Pin 13 | User I/O Bank 2, Pin 13 |

| A6 | User I/O Bank 4, Pin 14 | User I/O Bank 2, Pin 14 |

| A7 | User I/O Bank 4, Pin 15 | User I/O Bank 2, Pin 15 |

| A8 | User I/O Bank 4, Pin 16 | User I/O Bank 2, Pin 16 |

| A9 | User I/O Bank 4, Pin 17 | User I/O Bank 2, Pin 17 |

| AA | User I/O Bank 4, Pin 18 | User I/O Bank 2, Pin 18 |

| AB | User I/O Bank 4, Pin 19 | User I/O Bank 2, Pin 19 |

| AC | User I/O Bank 4, Pin 20 | User I/O Bank 2, Pin 20 |

| AD | User I/O Bank 4, Pin 21 | User I/O Bank 2, Pin 21 |

| AE | User I/O Bank 4, Pin 22 | User I/O Bank 2, Pin 22 |

| AF | User I/O Bank 4, Pin 23 | User I/O Bank 2, Pin 23 |

| B0 | User I/O Bank 4, Pin 24 | User I/O Bank 2, Pin 24 |

| B1 | User I/O Bank 4, Pin 25 | User I/O Bank 2, Pin 25 |

| B2 | User I/O Bank 4, Pin 26 | User I/O Bank 2, Pin 26 |

| B3 | User I/O Bank 4, Pin 27 | User I/O Bank 2, Pin 27 |

| B4 | User I/O Bank 4, Pin 28 | User I/O Bank 2, Pin 28 |

| B5 | User I/O Bank 4, Pin 29 | User I/O Bank 2, Pin 29 |

| B6 | User I/O Bank 4, Pin 30 | User I/O Bank 2, Pin 30 |

| B7 | User I/O Bank 4, Pin 31 | User I/O Bank 2, Pin 31 |

| B8 | Daughtercard Pin 43 | Daughtercard Pin 0 |

| B9 | Daughtercard Pin 42 | Daughtercard Pin 1 |

| BA | Daughtercard Pin 41 | Daughtercard Pin 2 |

| BB | Daughtercard Pin 40 | Daughtercard Pin 3 |

| BC | Daughtercard Pin 39 | Daughtercard Pin 4 |

| BD | Daughtercard Pin 38 | Daughtercard Pin 5 |

| BE | Daughtercard Pin 37 | Daughtercard Pin 6 |

| BF | Daughtercard Pin 36 | Daughtercard Pin 7 |

| C0 | Daughtercard Pin 35 | Daughtercard Pin 8 |

| C1 | Daughtercard Pin 34 | Daughtercard Pin 9 |

| C2 | Daughtercard Pin 33 | Daughtercard Pin 10 |

| C3 | Daughtercard Pin 32 | Daughtercard Pin 11 |

| C4 | Daughtercard Pin 31 | Daughtercard Pin 12 |

| C5 | Daughtercard Pin 30 | Daughtercard Pin 13 |

| C6 | Daughtercard Pin 29 | Daughtercard Pin 14 |

| C7 | Daughtercard Pin 28 | Daughtercard Pin 15 |

| C8 | Daughtercard Pin 27 | Daughtercard Pin 16 |

| C9 | Daughtercard Pin 26 | Daughtercard Pin 17 |

| CA | Daughtercard Pin 25 | Daughtercard Pin 18 |

| CB | Daughtercard Pin 24 | Daughtercard Pin 19 |

| CC | Daughtercard Pin 23 | Daughtercard Pin 20 |

| CD | Daughtercard Pin 22 | Daughtercard Pin 21 |

| CE | Analyzer Pod 2, Channel 0 (Pin 37) | Analyzer Pod 1, Channel 0 (Pin 37) |

| CF | Analyzer Pod 2, Channel 1 (Pin 35) | Analyzer Pod 1, Channel 1 (Pin 35) |

| D0 | Analyzer Pod 2, Channel 2 (Pin 33) | Analyzer Pod 1, Channel 2 (Pin 33) |

| D1 | Analyzer Pod 2, Channel 3 (Pin 31) | Analyzer Pod 1, Channel 3 (Pin 31) |

| D2 | Analyzer Pod 2, Channel 4 (Pin 29) | Analyzer Pod 1, Channel 4 (Pin 29) |

| D3 | Analyzer Pod 2, Channel 5 (Pin 27) | Analyzer Pod 1, Channel 5 (Pin 27) |

| D4 | Analyzer Pod 2, Channel 6 (Pin 25) | Analyzer Pod 1, Channel 6 (Pin 25) |

| D5 | Analyzer Pod 2, Channel 7 (Pin 23) | Analyzer Pod 1, Channel 7 (Pin 23) |

| D6 | Analyzer Pod 2, Channel 8 (Pin 21) | Analyzer Pod 1, Channel 8 (Pin 21) |

| D7 | Analyzer Pod 2, Channel 9 (Pin 19) | Analyzer Pod 1, Channel 9 (Pin 19) |

| D8 | Analyzer Pod 2, Channel 10 (Pin 17) | Analyzer Pod 1, Channel 10 (Pin 17) |

| D9 | Analyzer Pod 2, Channel 11 (Pin 15) | Analyzer Pod 1, Channel 11 (Pin 15) |

| DA | Analyzer Pod 2, Channel 12 (Pin 13) | Analyzer Pod 1, Channel 12 (Pin 13) |

| DB | Analyzer Pod 2, Channel 13 (Pin 11) | Analyzer Pod 1, Channel 13 (Pin 11) |

| DC | Analyzer Pod 2, Channel 14 (Pin 9) | Analyzer Pod 1, Channel 14 (Pin 9) |

| DD | Analyzer Pod 2, Channel 15 (Pin 7) | Analyzer Pod 1, Channel 15 (Pin 7) |

| DE | Analyzer Pod 2, Clock Channel (Pin 16) | Analyzer Pod 1, Clock Channel (Pin 16) |

| DF | Analyzer Pod 4, Channel 0 (Pin 37) | Analyzer Pod 3, Channel 0 (Pin 37) |

| E0 | Analyzer Pod 4, Channel 1 (Pin 35) | Analyzer Pod 3, Channel 1 (Pin 35) |

| E1 | Analyzer Pod 4, Channel 2 (Pin 33) | Analyzer Pod 3, Channel 2 (Pin 33) |

| E2 | Analyzer Pod 4, Channel 3 (Pin 31) | Analyzer Pod 3, Channel 3 (Pin 31) |

| E3 | Analyzer Pod 4, Channel 4 (Pin 29) | Analyzer Pod 3, Channel 4 (Pin 29) |

| E4 | Analyzer Pod 4, Channel 5 (Pin 27) | Analyzer Pod 3, Channel 5 (Pin 27) |

| E5 | Analyzer Pod 4, Channel 6 (Pin 25) | Analyzer Pod 3, Channel 6 (Pin 25) |

| E6 | Analyzer Pod 4, Channel 7 (Pin 23) | Analyzer Pod 3, Channel 7 (Pin 23) |

| E7 | Analyzer Pod 4, Channel 8 (Pin 21) | Analyzer Pod 3, Channel 8 (Pin 21) |

| E8 | Analyzer Pod 4, Channel 9 (Pin 19) | Analyzer Pod 3, Channel 9 (Pin 19) |

| E9 | Analyzer Pod 4, Channel 10 (Pin 17) | Analyzer Pod 3, Channel 10 (Pin 17) |

| EA | Analyzer Pod 4, Channel 11 (Pin 15) | Analyzer Pod 3, Channel 11 (Pin 15) |

| EB | Analyzer Pod 4, Channel 12 (Pin 13) | Analyzer Pod 3, Channel 12 (Pin 13) |

| EC | Analyzer Pod 4, Channel 13 (Pin 11) | Analyzer Pod 3, Channel 13 (Pin 11) |

| ED | Analyzer Pod 4, Channel 14 (Pin 9) | Analyzer Pod 3, Channel 14 (Pin 9) |

| EE | Analyzer Pod 4, Channel 15 (Pin 7) | Analyzer Pod 3, Channel 15 (Pin 7) |

| EF | Analyzer Pod 3, Clock Channel (Pin 16) | Analyzer Pod 3, Clock Channel (Pin 16) |

Source Code

MIT 6.111 Introduction to Digital Systems, Updated April 05, 2005