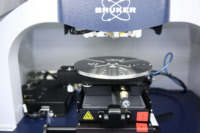

Equipment

| Lab and Coral Name | TRL / dektak-XT |

| Model | Sloan Dektak II |

| Specialist | David Terry (Paul Tierney) |

| Physical Location | 4F Photo-South |

Classification

| Process Category | Metrology |

| Subcategory | Profile |

| Material Keywords | None |

| Sample Size | 6" Wafers, 4" Wafers, 7" Photo Plates, 5" Photo Plates, Pieces |

| Alternative | none |

| Keywords | single wafer, manual load, top side of sample, manual operation, alignment |

Description

The dektak is a stylus (contact) profilometer that is used to measure height differences (steps) on samples for Au based processes. This system operates by the stylus physically making contact with the sample surface and moving the stylus to measure changes in surface height.

| Best for | For measuring the step height for PR, metals and dielectrics. |

| Limitations | Depth monitoring in small openings (~ 100nm wide) is challenging. |

| Characteristics/FOM | Stylus moves over the surface to map the surface topography |

| Caution with | Sample surface should be hard enough to avoid any deposits over the tip (e.g if PR is not sufficiently bakes) |

| Machine Charges | 2/hour |

Documents

Process Matrix Details

Permitted

Been in the ALDSamples that have been in any of the ALD systems

, Pyrex SubstratesPyrex substrates can be a concern due to high sodium content, which contaminates CMOS frontend tools

, III-V SubstratesAny III-V substrates, e.g. GaAs, GaN, InP, and so on. Note though that many common III-V substrates will also carry the Au flag, but there are some GREEN III-V substrates.

, Germanium on surfaceSamples with germanium on the surface (typically grown films)

, Germanium buriedSamples with germanium buried below a different film

, PiecesWafer pieces may not be handled by the equipment, and are harder to thoroughly clean - preventing them from running in certain tools.

, Gold or RED color codeRED color code substrates. These are gold-contaminated or have been processed in gold contaminated tools. Gold and other metals can contaminate silicon devices (GREEN color code) and have to be separated.

, Any exposure to CMOS metalIf the sample had ever seen a CMOS metal (or a tool that accepts CMOS metal), then some frontend tools could be contaminated by this.

, CMOS metal on surfaceCMOS compatible metals exposed on the surface. These are Al,Ni,Pt,Ti,TiN. Other metals such as Au are *NOT* part of this.

, CMOS metal buriedCMOS compatible metals covered entirely by a different material. These are Al,Ni,Pt,Ti,TiN. Other metals such as Au are *NOT* part of this.

, Been in the STS DRIEThe DRIE etch leaves behind polymer residues on the sidewall ripples, which can be a contamination concern for some tools.

, Been in the SEMA sample viewed in the SEM must have used the appropriate chuck to avoid cross-contamination

, Been in the Concept1The Concep1 deposits dielectrics on GREEN wafers, however it also accepts metal and there can be cross-contamination for diffusion area

, Has PhotoresistSamples with photoresist cannot be exposed to high temperatures, which is typical in deposition tools. Outgassing can be a concern.

, Has PolyimidePolyimide is a very chemically resistant polymer, and can tolerate higher temperatures but cannot be exposed to typical PECVD deposition temperatures or diffusion furnaces. Outgassing can be a concern.

, Has Cured SU8Not fully cured SU8 residues can heavily contaminated plasma chambers or destroy other user's samples, but fully cured SU8 is permitted in certain tools.

, Coming from KOHAfter a KOH etch, the samples must receive a special clean because the K ions are highly contaminating to CMOS frontend tools

, Coming from CMPAfter a CMP, the samples must receive a special clean, because the slurry residues otherwise introduce contamination and particles.

Not Allowed

Ever been in EMLSamples from EML are never permitted to return to ICL or TRL

For more details or help, please consult PTC matrix, email ptc@mtl.mit.edu, or ask the research specialist (David Terry)